# VLSI IMPLEMENTATION OF A HIGH-SPEED DELTA-SIGMA ANALOG TO DIGITAL CONVERTER

A Thesis Presented to The Faculty of the Russ College of Engineering and Technology Ohio University

> In Partial Fulfillment of the Requirement for the Degree Master of Science

> > By Zheng Chen November, 1997

# THIS THESIS ENTITLED VLSI IMPLEMENTATION OF A HIGH-SPEED DELTA-SIGMA ANALOG TO DIGITAL CONVERTER by Zheng Chen

has been approved

for the School of Electrical Engineering and Computer Science and the Russ College of Engineering and Technology

Janusz Starzyk, Professor School of Electrical Engineering and Computer Science

Warren K. Wray, Dean Russ College of Engineering and Technology

# ACKNOWLEDGEMENTS

I sincerely thank my thesis advisor, Dr. Janusz Starzyk, for his many hours of generous assistance. Not only did Dr. Starzyk recommend many useful references, but also attributed his insights in many theoretical issues. I will remember the refreshed feeling that I got each time I discussed with him a headache problem disturbing me for several days. That feeling gave me new energy and guided me to the right direction.

Special thanks go to my family and my dear friend, Ling Zhu, as well as his parents, whose support gave me spiritual strength in pursuing my ambition and my staying in the United States.

I am very thankful also, to Dr. Voula Georgopoulos, Dr. Xuefeng Fang at IDT Inc., and Mr. David Zar at Washington University in St. Louis, for their help on digital filter, switched-capacitor circuit, and MOSIS design kits, respectively. Finally, thanks to all my friends, who assisted me upon request and were very helpful in their suggestions.

# TABLE OF CONTENTS

| LIST OF TABLES                      |               |                           |                                                                          |                |

|-------------------------------------|---------------|---------------------------|--------------------------------------------------------------------------|----------------|

| Cl                                  | hapt          | er                        |                                                                          |                |

| $egin{array}{c} 1 \\ 2 \end{array}$ |               |                           | UCTION                                                                   | $rac{1}{3}$   |

|                                     | $2.1 \\ 2.2$  |                           | iew of Various A/D Converter Types                                       | 4<br>9         |

|                                     |               | $2.2.1 \\ 2.2.2 \\ 2.2.3$ | A/D Conversion Terms                                                     | 10<br>12<br>13 |

|                                     | 2.3           | Archit                    | ectures of $\Delta\Sigma$ A/D Converters                                 | 18             |

|                                     |               | $2.3.1 \\ 2.3.2 \\ 2.3.3$ | Higher-Order Single-Stage $\Delta\Sigma$ Converters                      | 19<br>20<br>22 |

|                                     | 2.4           | Digita                    | l Filters for $\Delta\Sigma$ A/D Converters                              | 24             |

|                                     |               | $2.4.1 \\ 2.4.2 \\ 2.4.3$ | Basic Principles of DecimationMultistage ImplementationFilter Structures | 25<br>26<br>28 |

| 3                                   | $\mathbf{AN}$ | ALOG                      | MODULATOR DESIGN                                                         | 33             |

|                                     | 3.1           | A Cas                     | caded Multibit $\Delta\Sigma$ Modulator                                  | 33             |

|                                     |               | 3.1.1                     | $\Delta\Sigma$ Modulation at Low Oversampling Ratios                     | 33             |

|   |              | 3.1.2                                                       | Linear Analysis of the Modulator      | 35                                                                    |

|---|--------------|-------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------|

|   | 3.2          | Modifi                                                      | ed Modulator with Interstage Coupling | 36                                                                    |

|   |              | 3.2.1<br>3.2.2<br>3.2.3                                     | Interstage Coupling                   | 37<br>38<br>39                                                        |

|   | 3.3          | VLSI I                                                      | mplementation                         | 41                                                                    |

|   |              | 3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7 | Top-Level Structure of the Modulator  | $\begin{array}{c} 41 \\ 43 \\ 47 \\ 51 \\ 55 \\ 56 \\ 60 \end{array}$ |

| 4 | DIC          | GITAL                                                       | DECIMATOR DESIGN                      | 68                                                                    |

|   | 4.1          | Digital                                                     | Filter Design                         | 68                                                                    |

|   |              | $4.1.1 \\ 4.1.2$                                            | Fourth-Order Comb $(sinc^4)$ Filter   | 70<br>70                                                              |

|   | 4.2          | Digital                                                     | Filter Structures                     | 77                                                                    |

|   |              | $\begin{array}{c} 4.2.1 \\ 4.2.2 \\ 4.2.3 \end{array}$      | Two's Complement Arithmetic           | 78<br>79<br>81                                                        |

|   | 4.3          | VHDL                                                        | Implementation                        | 83                                                                    |

|   |              | $4.3.1 \\ 4.3.2$                                            | Programming and Simulation            | 83<br>90                                                              |

| 5 | CO           | NCLU                                                        | SION                                  | 94                                                                    |

|   | $5.1 \\ 5.2$ |                                                             | ary                                   | 94<br>96                                                              |

| BI | BIBLIOGRAPHY             |                                                                                                                                                                                                                                                                               |                     |  |

|----|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|

| A  | ppen                     | dix                                                                                                                                                                                                                                                                           |                     |  |

| A  | мо                       | SIS SCMOS PROCESS                                                                                                                                                                                                                                                             | 104                 |  |

|    | A.1<br>A.2               | SCN08HP Technology and Parameter File                                                                                                                                                                                                                                         |                     |  |

| в  | VH                       | DL PROGRAMS                                                                                                                                                                                                                                                                   | 107                 |  |

|    | B.2                      | Comb Filter          Half-Band FIR Filters                                                                                                                                                                                                                                    | $109 \\ 110 \\ 112$ |  |

| С  | MA                       | TLAB PROGRAMS                                                                                                                                                                                                                                                                 | 119                 |  |

|    | C.1<br>C.2<br>C.3<br>C.4 | Herrmann Estimation of FIR Filter Order $\ldots$ $\ldots$ $\ldots$ Frequency Response of $sinc^k$ Comb Filters $\ldots$ $\ldots$ $\ldots$ Two-Stage Half-Band Filter Design $\ldots$ $\ldots$ $\ldots$ Half-Band Filters with Rounded Coefficients $\ldots$ $\ldots$ $\ldots$ | 119<br>121          |  |

# LIST OF TABLES

| 2.1 | Different A/D Converter Types.                       | 5  |

|-----|------------------------------------------------------|----|

| 3.1 | Transistors in the Bias Circuit.                     | 50 |

| 3.2 | Transistors in the Opamp Circuit.                    | 53 |

| 3.3 | Clock Signals Defined in the Simulator               | 61 |

| 4.1 | Design Specifications of the Decimator               | 69 |

| 4.2 | Nonzero Coefficients of the 11-tap Half-Band Filter  | 72 |

| 4.3 | Nonzero Coefficients of the 165-tap Half-Band Filter | 73 |

| 4.4 | Decimal Equivalents of Numbers 0.11 to 1.00.         | 78 |

| 4.5 | Periodical Test Patterns for Digital Filters.        | 90 |

| 4.6 | Global Cell Usage Statistics for Digital Filters     | 91 |

| 4.7 | Hierarchy Statistics for Digital Filters.            | 92 |

# LIST OF FIGURES

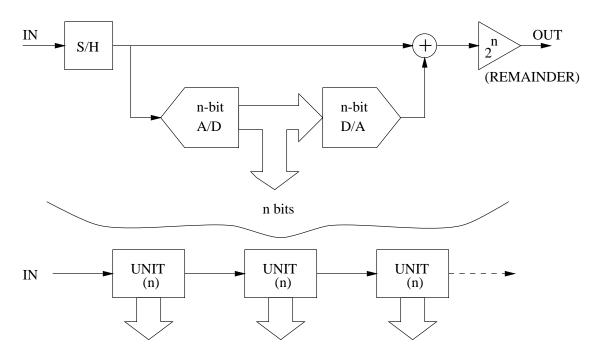

| 2.1  | Block diagram of pipelined A/D converter                                                                                            | 7  |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|

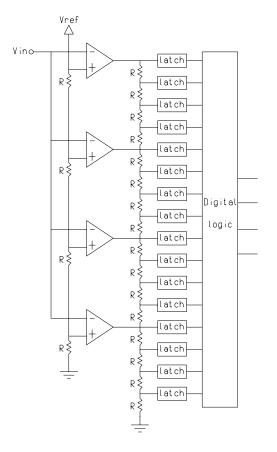

| 2.2  | A 4-bit interpolating A/D converter.                                                                                                | 9  |

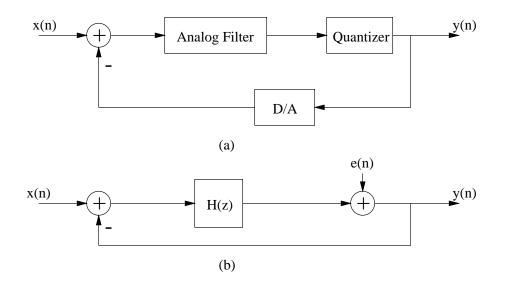

| 2.3  | A $\Delta\Sigma$ modulator and its linear model.                                                                                    | 14 |

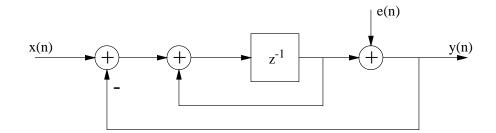

| 2.4  | A first-order $\Delta\Sigma$ modulator                                                                                              | 15 |

| 2.5  | A second-order $\Delta\Sigma$ modulator                                                                                             | 17 |

| 2.6  | Spectral density of noise for some different noise-shaping modulation.                                                              | 18 |

| 2.7  | Chain of integrators with distributed feedback and distributed feedforward inputs.                                                  | 20 |

| 2.8  | Block diagram of cascaded modulator.                                                                                                | 21 |

| 2.9  | Simplified linear model of a $\Delta\Sigma$ ADC with nonlinearity errors                                                            | 23 |

| 2.10 | (a) Leslie-Singh structure. (b) An Equivalent representation                                                                        | 25 |

| 2.11 | A $\Delta\Sigma$ A/D converter system                                                                                               | 26 |

| 2.12 | Decimation by a factor M                                                                                                            | 26 |

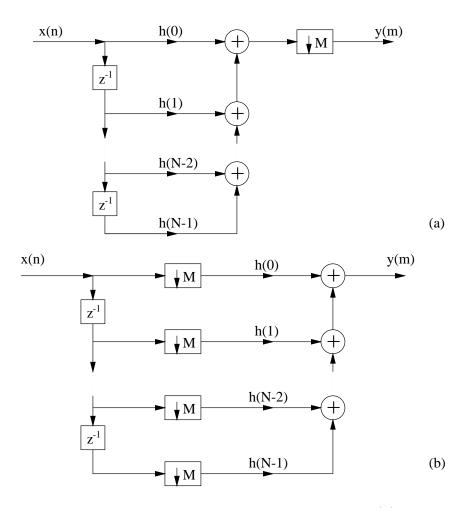

| 2.13 | FIR structures for decimation by a factor M. (a) Direct form. (b)<br>Efficient direct form                                          | 29 |

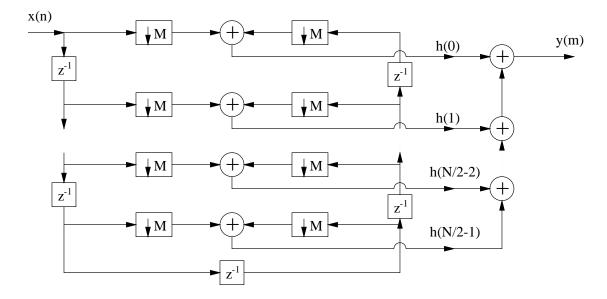

| 2.14 | Symmetrical FIR structure for decimation by a factor M                                                                              | 30 |

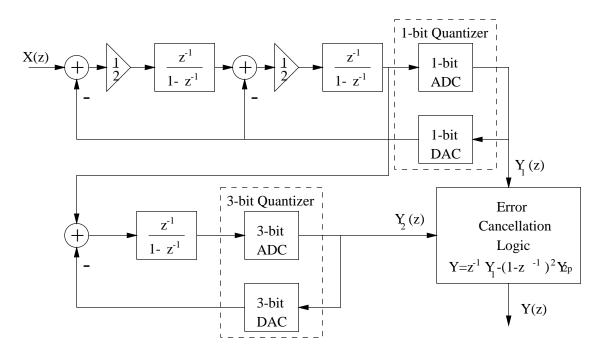

| 3.1  | Block diagram of a third-order cascaded multibit $\Delta\Sigma$ A/D converter.                                                      | 34 |

| 3.2  | A cascaded multibit $\Delta\Sigma$ ADC with interstage coupling                                                                     | 37 |

| 3.3  | Modified structure of the third-order cascaded multibit $\Delta\Sigma$ ADC.<br>Note that the $Y_{2p}$ is defined in Equation (3.6). | 40 |

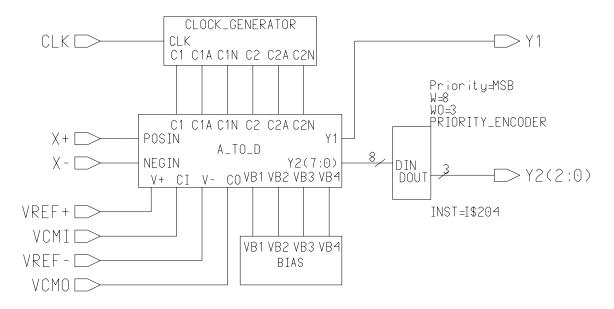

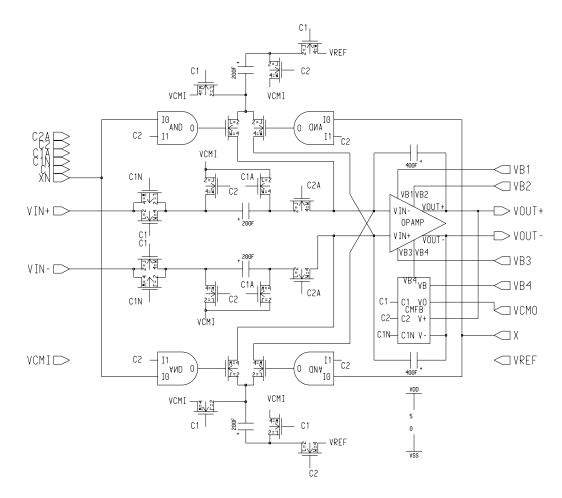

| <b>3.4</b> | Top-level schematic of the modulator                                                                                                         | 41 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------|----|

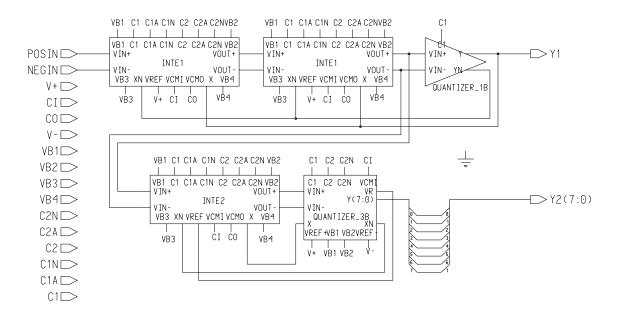

| 3.5        | The $A$ -to- $D$ block in Figure 3.4                                                                                                         | 42 |

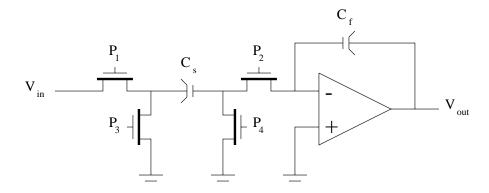

| 3.6        | A parasitic-insensitive switched-capacitor integrator                                                                                        | 43 |

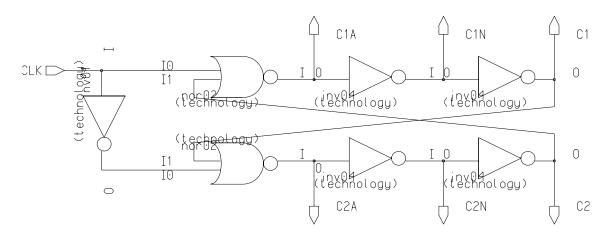

| 3.7        | The <i>CLOCK_GENERATOR</i> block in Figure 3.4                                                                                               | 44 |

| <b>3.8</b> | The $INTE1$ block in Figure 3.5                                                                                                              | 45 |

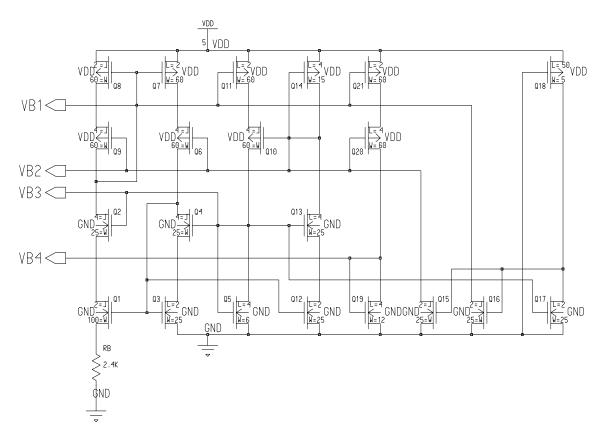

| 3.9        | The $BIAS$ block in Figure 3.4                                                                                                               | 48 |

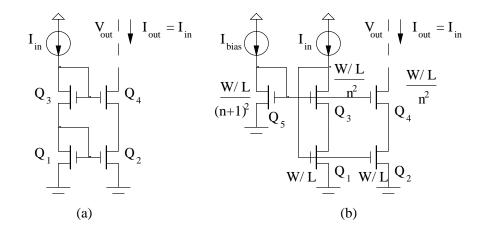

| 3.10       | Conventional (a) and wide-swing (b) cascode current mirrors. $I_{bias}$ typically is set to the nominal or maximum input current, $I_{in}$ . | 49 |

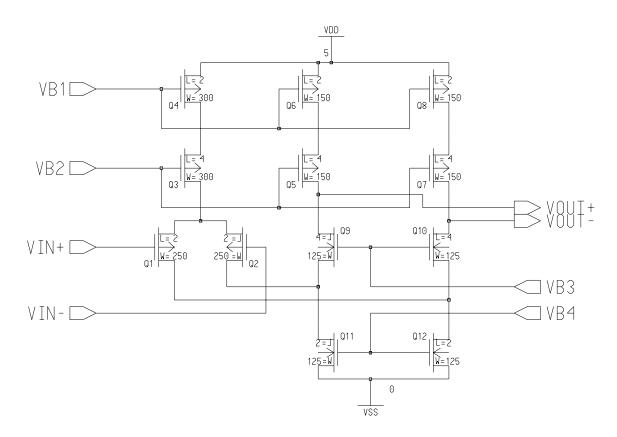

| 3.11       | The <i>OPAMP</i> block in Figure 3.8                                                                                                         | 52 |

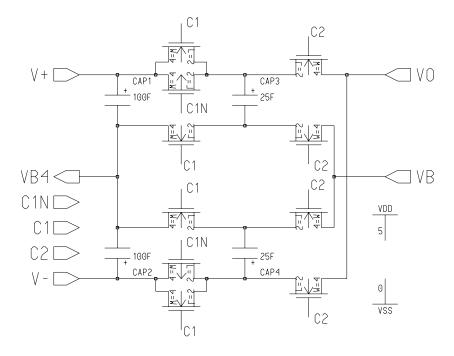

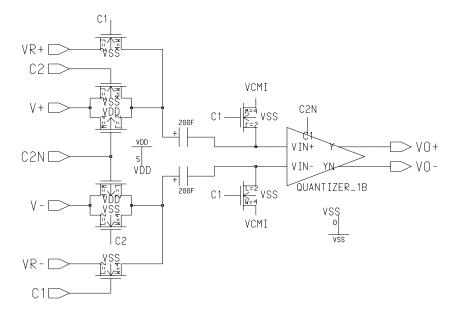

| 3.12       | The $CMFB$ block in Figure 3.8                                                                                                               | 54 |

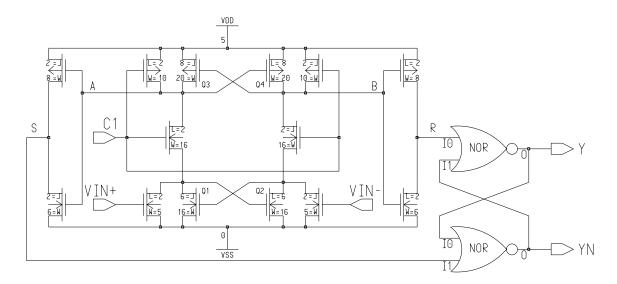

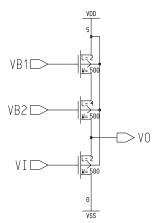

| 3.13       | The $QUANTIZER_{1B}$ block in Figure 3.5                                                                                                     | 55 |

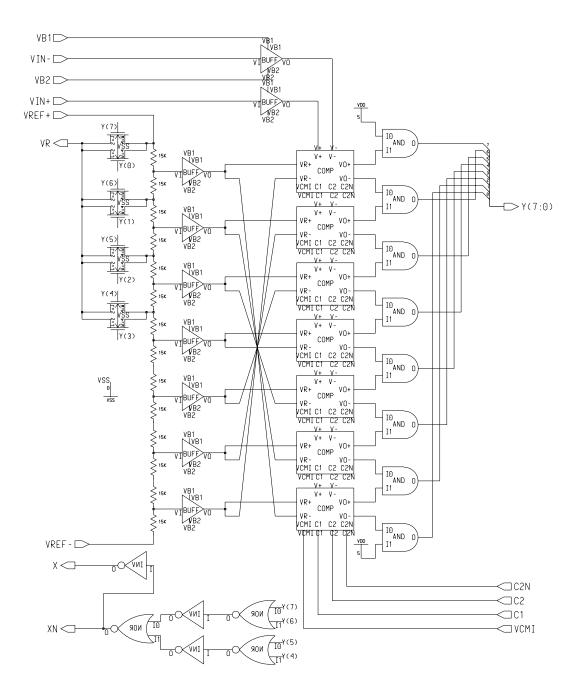

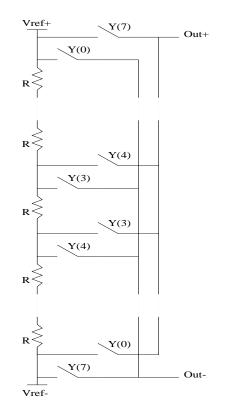

| 3.14       | The $QUANTIZER_{3B}$ block in Figure 3.5                                                                                                     | 57 |

| 3.15       | The $BUFF$ block shown in Figure 3.14                                                                                                        | 58 |

| 3.16       | The $CMPR$ block shown in Figure 3.14                                                                                                        | 59 |

| 3.17       | Block diagram of a 3-bit differential DAC.                                                                                                   | 60 |

| 3.18       | Bias voltages from simulation of the circuit shown in Figure 3.9. $$ .                                                                       | 62 |

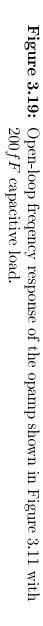

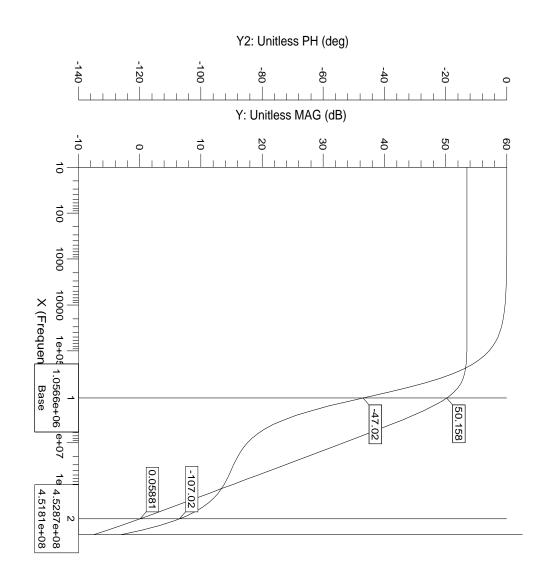

| 3.19       | Open-loop frequency response of the opamp shown in Figure 3.11 with $200 fF$ capacitive load                                                 | 63 |

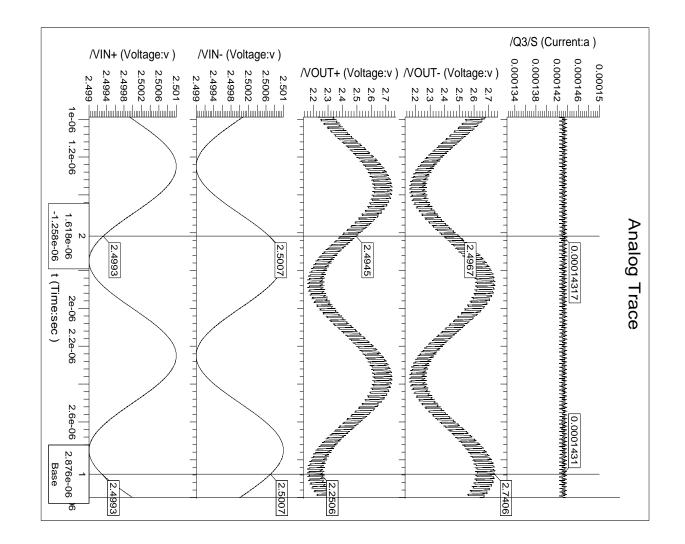

| 3.20       | Open-loop transient analysis of the opamp shown in Figure 3.11 with $200 fF$ capacitive load                                                 | 64 |

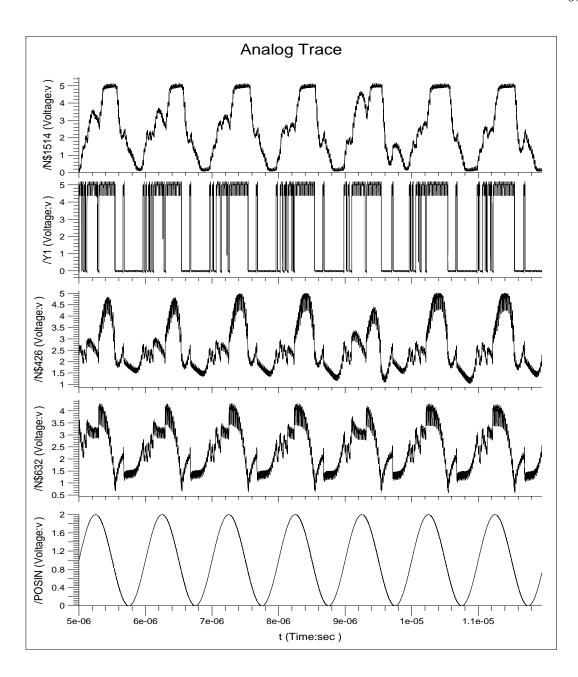

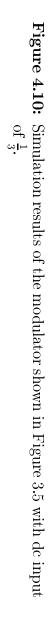

| 3.21       | Simulation results of the modulator shown in Figure 3.5. (a) Outputs of the integrators and 1-bit quantizer                                  | 65 |

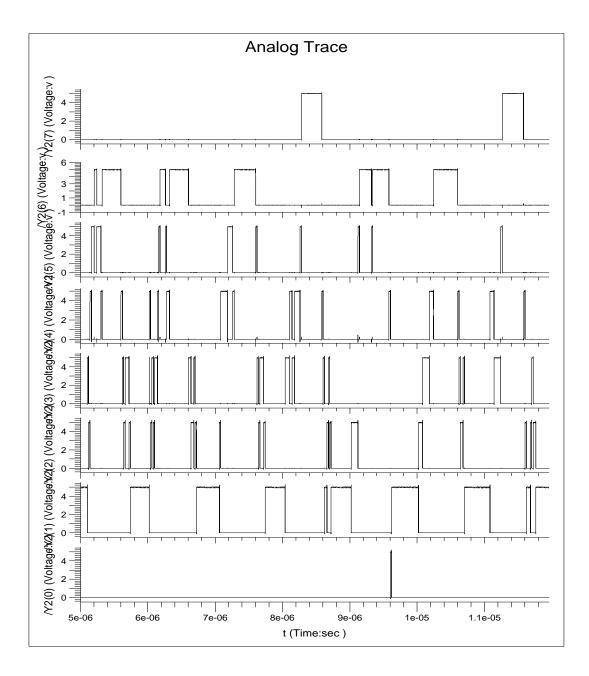

| 3.22 | Simulation results of the modulator shown in Figure 3.5. (b) Outputs of the 3-bit quantizer | 66 |

|------|---------------------------------------------------------------------------------------------|----|

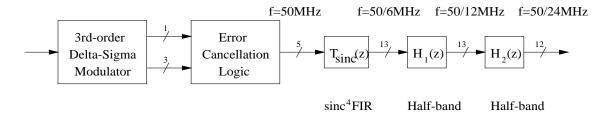

| 4.1  | Block diagram of digital filters.                                                           | 69 |

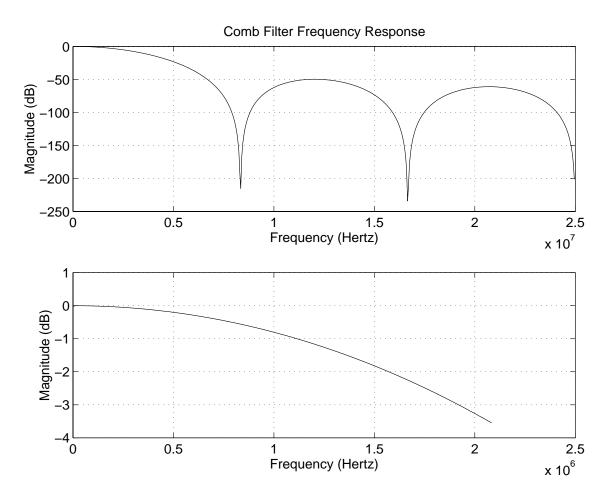

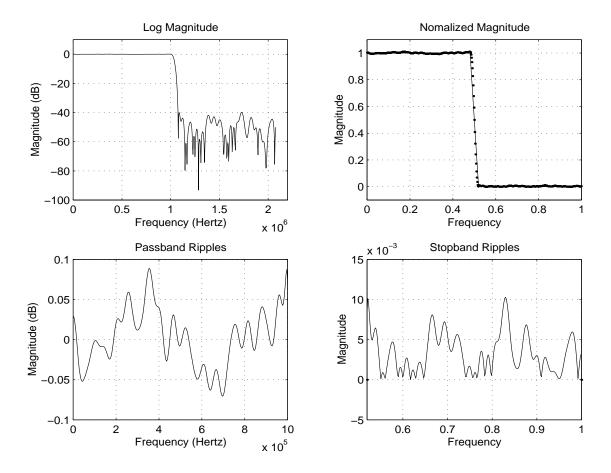

| 4.2  | Frequency response of $sinc^4$ filter with a decimation ratio of 6                          | 71 |

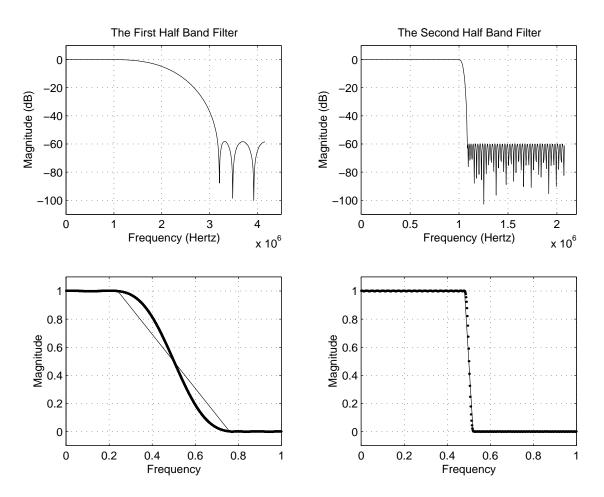

| 4.3  | Frequency responses of 11-tap and 165-tap half-band filters                                 | 74 |

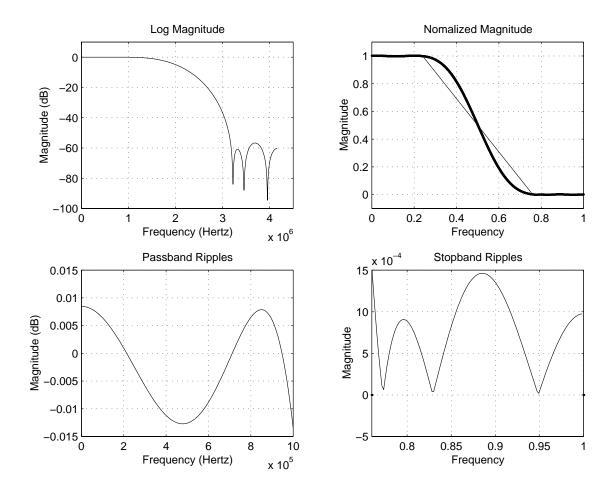

| 4.4  | Frequency responses of 11-tap half-band filter with rounded coefficients.                   | 75 |

| 4.5  | Frequency responses of 165-tap half-band filter with rounded coefficients.                  | 76 |

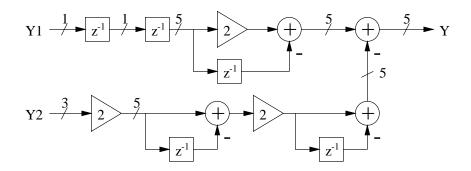

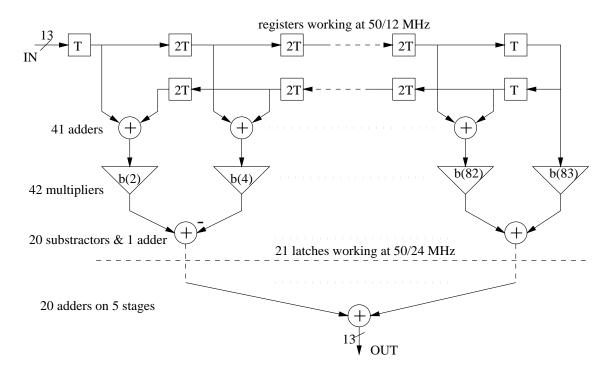

| 4.6  | Structure for error cancellation logic.                                                     | 79 |

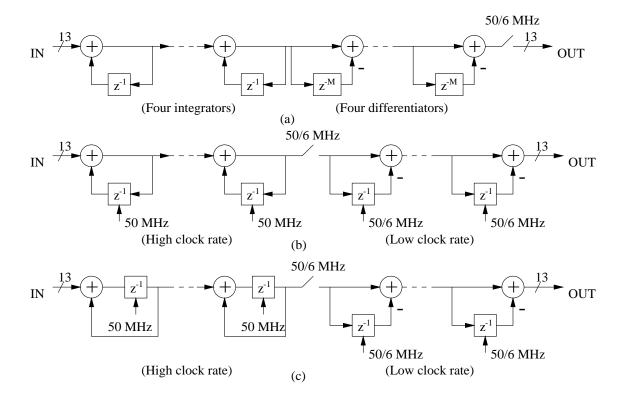

| 4.7  | Structures for the fourth-order comb filter                                                 | 80 |

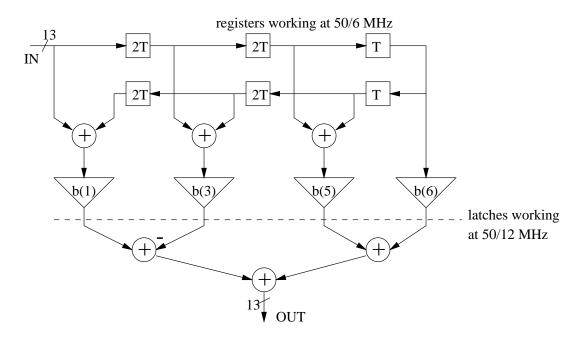

| 4.8  | Structure for the 11-tap half-band filter                                                   | 81 |

| 4.9  | Structure for the 165-tap half-band filter                                                  | 82 |

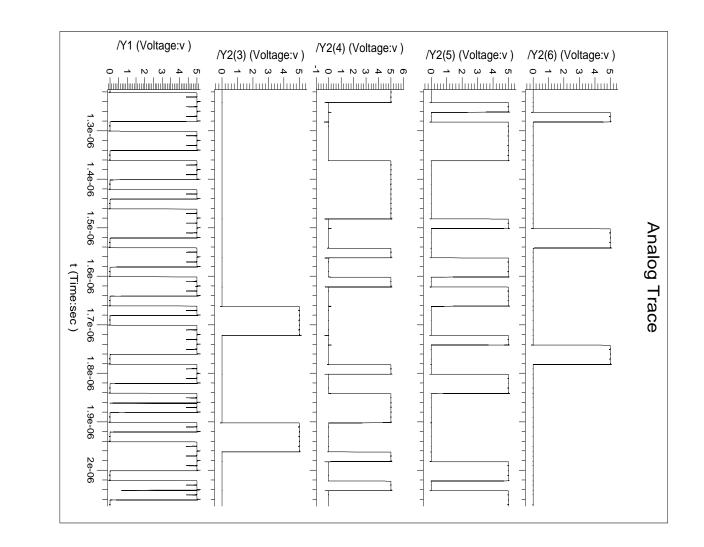

| 4.10 | Simulation results of the modulator shown in Figure 3.5 with dc input of $\frac{1}{3}$      | 88 |

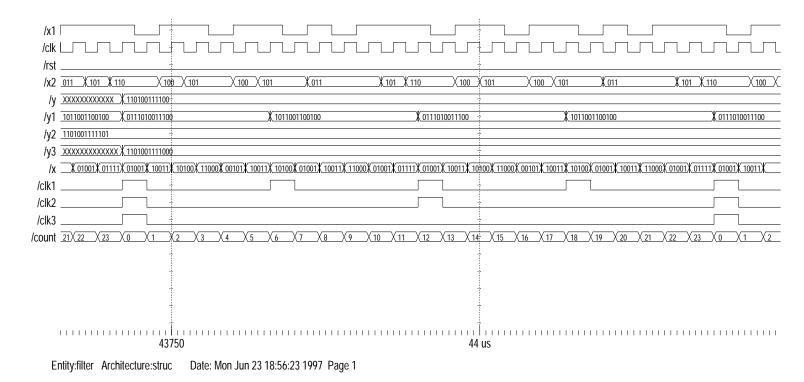

| 4.11 | Simulation results of the digital circuits modeled in Appendix B.5                          | 89 |

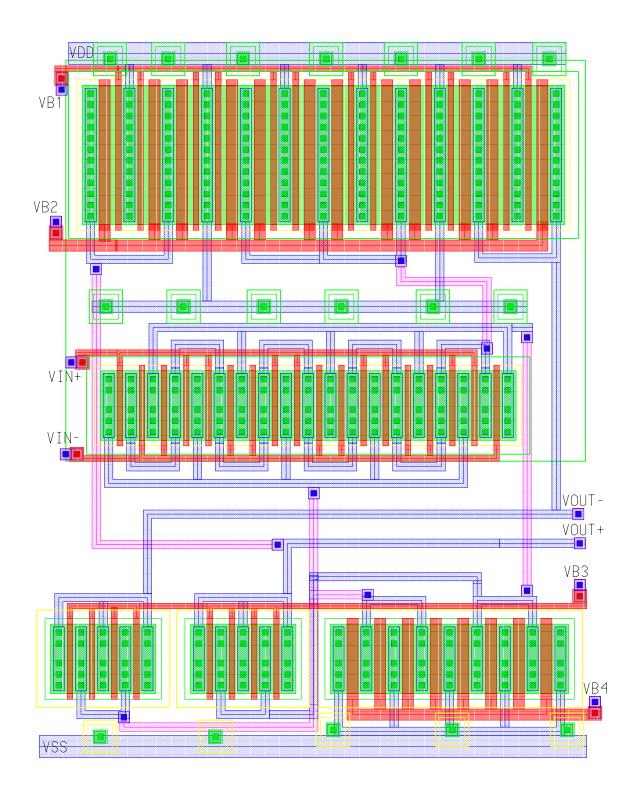

| 5.1  | Layout for the opamp shown in Figure 3.11.                                                  | 97 |

# Chapter 1

# INTRODUCTION

The emergence of powerful digital signal processors for telecommunication and multimedia applications implemented in CMOS VLSI technology creates the need for high-resolution analog-to-digital (A/D) converters that can be integrated in fabrication technologies optimized for digital circuits and systems. However, the same scaling of VLSI technology that makes possible the continuing dramatic improvements in digital signal processor performance also severely constrains the dynamic range available for implementing the interfaces between the digital and analog representation of signals. Oversampled A/D converters based on  $\Delta\Sigma$  (delta-sigma) modulation combine sampling at rates well above the Nyquist rate with negative feedback and digital filtering in order to exchange resolution in time for that in amplitude. These converters are especially insensitive to circuit imperfections and component mismatch, and therefore provide a means of exploiting the enhanced density and speed of scaled digital VLSI circuits so as to avoid the difficulty of implementing complex analog circuit functions within a limited analog dynamic range.

A  $\Delta\Sigma$  modulator consists of an analog filter and a coarse quantizer enclosed in a feed back loop. Together with the filter, the feedback loop acts to attenuate the quantization noise at low frequencies while emphasizing the high-frequency noise. Since the analog signal is sampled at a frequency much greater than the Nyquist rate and the quantization noise in the low-frequency signal band can be shaped to the high frequency range, a conversion with high resolution may be achieved by removing out-of-band quantization noise with a digital low-pass filter operating on the output of the  $\Delta\Sigma$  modulator.  $\Delta\Sigma$  data converters have been successfully applied in many low-frequency fields, such as digital audio and ISDN systems, while efforts are dedicated to developing new  $\Delta\Sigma$  structures for higher-frequency applications. A new structure [1] has been proposed for conversion rate up to 2 MHz. The purpose of this thesis is to implement a  $\Delta\Sigma$  A/D converter system exploiting that proposed structure in a 0.8- $\mu m$  CMOS technology, so that it can achieve 12-bit resolution and 2.08 MHz conversion working at 50 MHz clock for 1 MHz signal band.

Chapter 2 discusses the concepts and structures of  $\Delta\Sigma$  modulation as well as digital filters for decimation of sampling rate. A general introduction of A/D converters is also given in Chapter 2. Chapter 3 contains the design of the analog  $\Delta\Sigma$  modulator. This includes discussion sections on the new structure, VLSI implementation of the structure, and SPICE simulation results. Many analog building blocks, such as folded-cascode opamp, comparator, flash A/D converter, and switched-capacitor integrator, are designed on transistor level. Chapter 4 presents the design of digital filters in Matlab, VHDL modeling and simulation, and synthesis of standard-cell integrated circuits. All of the VHDL codes and Matlab programs are included in the appendices. A conclusion chapter gives some discussions on the future layout design.

# Chapter 2

# FUNDAMENTAL OF DELTA-SIGMA DATA CONVERTERS

Analog-to-digital interfaces are becoming increasingly more important as translators between state-of-the-art digital signal processing (DSP) systems and the stubbornly analog outside world. With strict demands for higher accuracy in signal processing, these interface stages must also become more precise. In particular, the data converters, both analog-to-digital (A/D) and digital-to-analog (D/A), must be at least as accurate as the overall precision of the DSP systems. At the same time, as both the feature sizes and bias voltages of very-large-scale integrated (VLSI) systems decrease, the accuracy and dynamic range of analog components are reduced, making the fabrication of monolithic high-resolution data converters more difficult.

Compared with the conventional Nyquist-rate converters, oversampling converters, where the sampling and processing rate is much higher than the Nyquist rate, relax the requirements placed on the analog circuitry at the expense of more complicated digital circuitry. This trade-off becomes more desirable for modern VLSI technologies. In order to achieve extra resolution and lower the oversampling ratio (OSR), noise-shaping techniques are usually used in oversampling converters, which is commonly referred to as delta-sigma ( $\Delta\Sigma$ ) modulation [2].<sup>1</sup>

In this chapter, an overview of various A/D converters is presented first. Then the basics of oversampling converters and architectures for  $\Delta\Sigma$  modulators are discussed. Finally, digital filters are described for decimating the modulated signal. Since this work is dedicated to a  $\Delta\Sigma$  A/D converter (ADC), the issues special for  $\Delta\Sigma$

$<sup>^{1}</sup>$  Delta-sigma modulation is also sometimes referred to as sigma-delta modulation.

D/A converters (DAC) will not be covered here. Interested readers may refer to [3, Chapter 12] for details of  $\Delta\Sigma$  DAC.

# 2.1 Overview of Various A/D Converter Types

Analog-to-digital converters can be classified in a number of ways. For example, we may classify them into two categories: Nyquist-rate and oversampling [4, Chapter 10], on the basis of their sampling rate of the input signal. If the bandwidth of the signal is  $f_0$ , then the sampling rate  $f_s$  has to be at least Nyquist rate  $2f_0$  in order to avoid aliasing. In the conventional Nyquist-rate A/D converter, the sampling rate  $f_s$  of the analog input signal is the same as the output data rate. Hence, a one-to-one correspondence exists between analog input samples and digital output words. Whereas, in the oversampling A/D converter, the  $f_s$  is much higher than Nyquist rate, and the oversampling ratio (OSR)  $f_s/(2f_0)$  is usually in the range from 16 to 512. Thus, every output word of the oversampling data converter is found as a weighted average of many consecutive analog input samples.

Since the oversampling A/D converter will be thoroughly discussed in the rest of this chapter, this section mainly discusses some types of Nyquist-rate A/D converters. We may further classify these Nyquist-rate A/D converters into three categories—low-to-medium speed, medium speed, and high speed (Table 2.1) [5, 6]. For comparative purpose, oversampling converter is listed in the table.<sup>2</sup>

It should be noted that the speed and resolution ranges in Table 2.1 just show a rough estimate. The classification criteria may need to be expanded based on the actual design.

A brief look at these Nyquist-rate converters may give us an idea of how they work and where they might fit:

$<sup>^{2}</sup>$  The conversion rate is equivalent to that of a Nyquist-rate converter.

|                   |                         | Samples           | Resolution            |

|-------------------|-------------------------|-------------------|-----------------------|

| Classification    | Type of A/D Converter   | per second        | $\operatorname{Bits}$ |

| Low-to-Medium     | Integrating             | 10-30             | 12-24                 |

| $\mathbf{Speed},$ | (dual-slope)            |                   |                       |

| High Accuracy     | Oversampling            | $10^{3} - 10^{6}$ | 12-22                 |

|                   | (delta-sigma)           |                   |                       |

| Medium Speed,     | Sampling (successive    | $10^4 - 10^6$     | 8-16                  |

| Medium Accuracy   | approximation)          |                   |                       |

| High Speed,       | Parallel (flash)        | $10^{6} - 10^{9}$ | 6-16                  |

| Low-to-Medium     | Subranging (two-step,   | $10^{5} - 10^{7}$ | 8-16                  |

| Accuracy          | multistep or pipelined) |                   |                       |

|                   | Interpolating (non-     | $10^{6} - 10^{8}$ | 8-12                  |

|                   | folding, folding)       |                   |                       |

Table 2.1: Different A/D Converter Types.

## Integrating converter:

This is the simplest and a popular approach for realizing high-accuracy data conversion on very slow-moving signals. The basic function of a quantizer is to electronically define a range of input values, subdivide that range into a set of subregions (i.e.,  $2^n$  levels for n-bit resolution), and then decide within which subregion the input sample lies. A *dual-slope* integrating converter achieves this by first performing an integration of an unknown input signal  $(-V_{in})$  in a fixed time period  $(T_1)$ , followed by the integration of a known reference signal of opposite polarity  $(V_{ref})$  to examine how long it takes to decay the integration to zero  $(T_2)$ . The time ratio of  $T_2/T_1$  can be used to determine the  $V_{in}$  level. This kind of converters are widely used in measurement instruments such as voltage or current meters because of their simplicity and insensitivity to hardware imperfections. However, the conversion speed is quite slow. For example, the worst-case conversion speed occurs when  $V_{in}$  equals  $V_{ref}$ . In this case, the conversion is equivalent to going from the lowest level to the highest level then to the lowest level again, which needs  $2^{n+1}$  clock cycles.

# Sampling converter:

This is so far the most popular fully integrated solution for moderate performance systems. This works by applying a "binary search" algorithm to successively approximate the input sample with the output of a digital-to-analog converter (DAC), whose input is also the ADC's output, and test each bit, instead of each level in the integrating converter. A binary search divides the search space in two each time, and the desired input level can be found in n steps for a set of  $2^n$  levels. Specially, in the first clock cycle, the most significant bit (MSB) of the DAC's input is set to '1' so that the output of the DAC equals half of  $V_{ref}$ . The comparison determines whether the MSB should be kept on '1' or not. In the second clock cycle, the bit next to the MSB is determined, followed by next bit and so on until the least significant bit (LSB) is determined. Thus, a successive-approximation converter requires n clock cycles to complete an n-bit conversion. The cost for this speed-up is that a high-speed DAC with precision on the order of the conversion itself is required.

## Parallel converter:

In parallel conversion, all subregions or levels are examined simultaneously using one comparator per subregion. Therefore, it is the highest-speed A/D converter, so called *flash* converter. The result can be obtained in the order of one clock cycle, but the cost in hardware area and power consumption is much greater than successive approximation, especially for higher resolutions (e.g., 8-bit resolution results in  $2^8 - 1 = 255$  comparators!). A 3-bit flash ADC will be designed as a part of this thesis work.

#### Subranging converter:

Very similar to flash converters, except that these perform two or more substeps or multisteps instead of requiring a complete conversion in one cycle. Multistep

Figure 2.1: Block diagram of pipelined A/D converter.

converter is also referred as to *pipelined* converter. These converters utilize a series of cascaded blocks in which a low-resolution A/D converter is used to estimate the signal, and a D/A converter and an analog subtraction block remove this estimate from the signal. A remainder voltage is passed on to the next stage where the process is repeated. A block diagram is shown in Figure 2.1 [4, Chapter 9]. The low-resolution A/D converter inside each cascade block is usually a flash converter. However, these converters can potentially achieve a throughput rate comparable with parallel converters but at much less hardware cost at large resolutions. It is straightforward to see that subranging converters save a lot of comparators over their flash counterparts. For example, an 8-bit *two-step* converter needs only  $2^5 - 2 = 30$  comparators, if each step involves a 4-bit flash converter, a big reduction comparing to 255 comparators required for a parallel converter.

### Interpolating converter:

A serious problem that the flash converters face is the large number of opamps attached to the input signal, which introduce quite high input capacitance so that a very big and power-hungry buffer has to be added to drive the signal. Interpolating converters can alleviate this problem by reducing the number of input amplifiers by an interpolating factor of k. For example, in a 4-bit interpolating A/D converter (Figure 2.2) [5, Chapter 13], only 4 input amplifiers may be used instead of 15 in a flash converter (i.e., interpolating factor of 4). These input amplifiers behave as linear amplifiers near their threshold voltages but are allowed to saturate once their differential inputs become moderately large. As a result, noncritical latches (as simple as an inverter) need only determine the sign of the amplifier outputs (i.e., above or below the threshold, which is near the midpoint of the two logic levels). Other subregions are interpolated between adjacent outputs of these amplifiers (e.g., 3 interpolative levels between each two adjacent amplifiers in Figure 2.2). The output of all the latches is encoded by the digital logic circuit. A *folding* architecture [7] is often used to further reduce the large number of latches in the above interpolating converters. A folding A/D converter works like a two-step converter while not requiring an accurate D/Aconverter.

Other low-speed and low-accuracy A/D converters are not discussed here since the major emphasis in this thesis is on advanced DSP applications in telecommunication. All of the above ADCs except integrating converter have been successfully used in most telecommunication applications. Perhaps the most significant development in telecommunication ADCs in recent years has come from the oversampling delta-sigma approach.

Figure 2.2: A 4-bit interpolating A/D converter.

# 2.2 Basic Concepts of Delta-Sigma A/D Conversion

As mentioned above, oversampling delta-sigma converters are more tolerable to imprecision of analog circuits by taking advantage of complicated and fast digital circuits. The second advantage of delta-sigma converters is that they simplify the requirements placed on the analog anti-aliasing filters for ADCs and smoothing filters for DACs. Furthermore, a sample-and-hold is usually not required at the input of the oversampling ADC. Therefore, they have become popular in recent years at least for medium to low speed applications such as high fidelity digital audio [8, 9, 10], digital telephony [11, 12, 13], and instrumentation. Future applications in digital video and digital radar systems are imminent as faster technologies become available.

# 2.2.1 A/D Conversion Terms

Before detailed concepts of  $\Delta\Sigma$  modulation are discussed, some commonly used terms describing the performance of data converters need to be reviewed.

- **Resolution** The number of bits of resolution refers to the smallest analog input level to cause change in the digital output word. Thus, an n-bit resolution implies that the converter can resolve  $2^n$  distinct analog levels.

- LSB (Least Significant Bit) One LSB=(full-scale input voltage)/resolution. For example, with input full scale= 5V and resolution=10 bits, then 1 LSB=  $5/2^{10} = 4.9mV$ .

- **Offset Error** For an A/D converter, the offset error is defined as the relative deviation of the actual  $V_{0...01}$  from  $\frac{1}{2}$  LSB, or mathematically,

$$E_{off} = \frac{V_{0...01}}{V_{LSB}} - \frac{1}{2}$$

in units of LSBs, where  $V_{0...01}$  refers to the input voltage as the output data becomes 0...01.

**Gain Error** This is also called the *full-scale* error, which refers to the difference between the actual input that produces a full-scale output word and the ideal voltage when the offset error has been reduced to zero. Or mathematically,

$$E_{gain} = \frac{V_{1\dots 11} - V_{0\dots 01}}{V_{LSB}} - (2^n - 2)$$

in units of LSBs, where  $V_{1...11}$  refers to the input voltage as the output data becomes 1...11.

- **Differential Nonlinearity (DNL) Error** In an ideal converter, each analog step size is equal to 1 LSB. After the offset and gain errors have been removed, DNL error is defined as the variation in analog step size away from 1 LSB. Thus, a converter with a maximum DNL of 0.5 LSB has its step size varying from 0.5 LSB to 1.5 LSB. For an ADC, when the DNL reaches 1 LSB or greater, there will be missing output codes.

- **Integral Nonlinearity (INL) Error** The INL is the worst-case deviation from a straight line between zero and full-scale endpoints of the converter's transfer response, expressed in LSBs. An ADC is guaranteed not to have any missing codes if the maximum INL error is less than 0.5 LSB.

- Accuracy The absolute accuracy of a converter is defined to be the difference between the expected and actual transfer responses, which includes the offset, gain, and nonlinearity errors. The relative accuracy is the accuracy after the offset and gain errors have been removed, which is usually referred to as the maximum INL error. Accuracy can be expressed as a percentage error of full-scale value, as the effective number of bits, or as a fraction of an LSB. For example, in order to achieve  $\frac{1}{2}$  LSB integral linearity, an 8-bit accuracy implies  $1/2^8 \approx 0.4\%$ matching, while a 12-bit accuracy implies  $1/2^{12} \approx 0.025\%$  matching. Note that a converter may have 12-bit resolution with only 10-bit accuracy, or 10-bit resolution with 12-bit accuracy. An accuracy greater than the resolution means that the converter's transfer response is very precisely controlled.

- Signal-to-Noise Ratio (SNR) This is the ratio of the original input signal power to the background noise power, or equivalently, the rms ratio of the input signal amplitude to the noise amplitude. For an ideal ADC with a sinusoidal input, the SNR related to the resolution n is

$$SNR_{rms} = 6.02 n + 1.76 \ dB$$

(2.1)

**Dynamic Range** The *dynamic range* of a converter is usually specified as the ratio of the rms value of the *maximum* amplitude of the sinusoidal input signal to the rms output noise plus the distortion measured when the same sinusoid is present at the output. The rms output noise plus distortion is obtained by first eliminating the sinusoid from the measured output. Dynamic range can also be expressed as an effective number of bits using the relationship presented in Equation (2.1). Essentially, this is an indication of how far it is possible to go below the full-scale input signal without hitting noise and/or distortion.

# 2.2.2 Oversampling Without Noise Shaping

The notion of using artificially high sampling rates and 1-bit quantization to achieve high resolution A/D conversion at a lower rate has been of interest ever since *delta modulation* [14] was first proposed in 1946. Extra dynamic range and SNR can be obtained by spreading the quantization noise power over a larger frequency range.

### Quantization Noise

Quantization of amplitude and sampling in time are at the heart of all digital modulators. Periodic sampling at rates more than twice the signal bandwidth need not introduce distortion, but quantization does. A quantizer can be modeled as adding quantization error e(n) to input x(n) to generate output y(n), i.e., y(n) = x(n) + e(n), where n refers to n-th sample. The quantization error is the difference between the input and output values, which is bounded by  $\pm \Delta/2$ , where  $\Delta$  equals the differences between two adjacent quantization levels, i.e., 1 LSB.

The error e(n) is completely defined by the input x(n), but if x(n) is very active, e(n) can be approximated as an independent random number uniformly distributed between  $\pm \Delta/2$ . Thus we can treat the quantization error as white noise e with power:

$$P_e = \frac{1}{\Delta} \int_{-\Delta/2}^{+\Delta/2} e^2 \, de = \frac{\Delta^2}{12}$$

(2.2)

and it is independent of the sampling frequency,  $f_s$ . Also the spectral density of e is white (i.e., a constant over frequency) and all of its power folds into the frequency band  $\pm f_s/2$  (a two-sided representation of frequencies). Then the spectral density of the sampled noise is given by

$$E(f) = \sqrt{\frac{P_e}{f_s}} = \left(\frac{\Delta}{\sqrt{12}}\right) \sqrt{\frac{1}{f_s}}$$

(2.3)

#### **Oversampling Advantage**

Oversampling occurs when the signals of interest are bandlimited to  $f_0$  yet the sampling rate is at  $f_s$ , where  $f_s$  is much larger than  $2f_0$ . As it was defined in the sections above, the oversampling ratio,  $OSR \equiv \frac{f_s}{2f_0}$ .

After quantization, since the signals of interest are all below  $f_0$ , the quantized signal (along with noise) is filtered by

$$H(f) = \begin{cases} 1 & |f| \le f_0 \\ 0 & f_0 < |f| < f_s \end{cases}$$

(2.4)

This filter eliminates quantization noise (together with any other image signals) greater than  $f_0$ .

While the in-band signal power is the same as the original input signal power, the quantization noise power is reduced to

$$P_{e}^{'} = \int_{-f_{s}/2}^{f_{s}/2} E^{2}(f) |H(f)|^{2} df = \int_{-f_{0}}^{f_{0}} E^{2}(f) df = \frac{2f_{0}}{f_{s}} P_{e} = \frac{P_{e}}{OSR}$$

(2.5)

Therefore, each doubling of OSR (i.e., sampling at twice the rate) decreases the inband noise power by one-half or, equivalently, 3 dB, increasing the resolution by only 0.5 bits according to Equation (2.1).

# 2.2.3 Noise-Shaping Oversampling $\Delta \Sigma$ Modulation

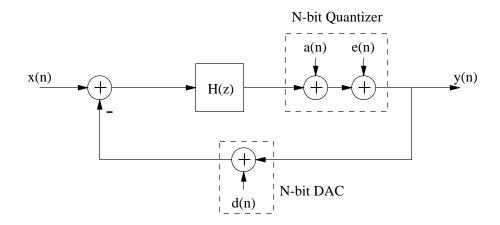

A more efficient oversampling quantizer is the noise-shaped  $\Delta\Sigma$  modulator shown in Figure 2.3(a). Although most present  $\Delta\Sigma$  converters make use of 1-bit

Figure 2.3: A  $\Delta\Sigma$  modulator and its linear model.

quantizers (i.e., only two output levels) due to the inherent linearity between two levels, a general discussion may be addressed on multilevel quantizers. By analyzing the linear model shown in Figure 2.3(b) as having two *independent* inputs x(n) and e(n), which is an approximation for active input signal x(n), we can derive a signal transfer function,  $S_{TF}(z)$ , and a noise transfer function,  $N_{TF}(z)$ , as

$$S_{TF}(z) \equiv \frac{Y(z)}{X(z)} = \frac{H(z)}{1 + H(z)}$$

(2.6)

$$N_{TF}(z) \equiv \frac{Y(z)}{E(z)} = \frac{1}{1 + H(z)}$$

(2.7)

Note that the zeros of  $N_{TF}(z)$  will be equal to the poles of H(z). In other words, when H(z) goes to infinity,  $N_{TF}(z)$  will go to zero.

In the frequency domain, the output signal can be written as the combination of the input signal and the noise signal:

$$Y(z) = S_{TF}(z)X(z) + N_{TF}(z)E(z)$$

(2.8)

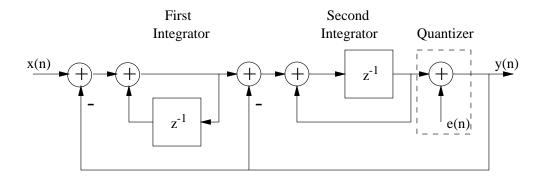

**Figure 2.4:** A first-order  $\Delta \Sigma$  modulator.

To noise-shape the quantization noise in a useful manner, the magnitude of H(z)should be so large over the frequency band of interest as to make  $N_{TF}(z)$  near zero and  $S_{TF}(z)$  near unity. Thus, the quantization noise is reduced over the signal bandwidth while the signal itself is largely unaffected. The feedback will not reduce the highfrequency noise since there is little loop gain at high frequency. However, the out-ofband noise can be removed by additional low-pass digital filters.

### **First-Order Noise Shaping**

To realize first-order noise shaping,  $N_{TF}(z)$  should have a zero at dc (i.e.,  $z = \epsilon^{j\omega T} = 1$ , where  $\omega = 0$ ) so that the quantization noise is high-pass filtered. Since the zeros of  $N_{TF}(z)$  are equal to the poles of H(z), H(z) should also have a pole at z = 1, resulting in a choice of a discrete-time integrator:

$$H(z) = \frac{1}{z - 1}$$

(2.9)

A block diagram for such a choice is shown in Figure 2.4. The signal goes first through a subtractor and then an accumulator, corresponding to  $\Delta\Sigma$ .

From a time domain point of view, the feedback forces the average value of the quantized output y(n) to equal the average value of input x(n) so that the integrator's input x(n)-y(n) equals zero (otherwise, the infinite dc gain will amplify the difference

to infinity). This configuration has similarity with an ideal opamp having unity closeloop gain.

From Equations (2.6), (2.7), and (2.9), we have  $S_{TF}(z) = z^{-1}$  and  $N_{TF}(z) = (1 - z^{-1})$ , corresponding to a one-clock-period delay for signal and a first-order highpass filter for noise. The spectral density of the modulation noise may be expressed as

$$E'(f) = E(f)|N_{TF}(z)| = E(f)|1 - z^{-1}| = E(f)|1 - \epsilon^{-j\omega T}| = \sqrt{8P_e T} \sin\frac{\omega T}{2} \quad (2.10)$$

where  $\omega = 2\pi f$ ,  $\frac{1}{T} = f_s$ , and the relation of E(f) and  $P_e$  is defined in Equation (2.3). Hence, the in-band noise power can be calculated as

$$P_e^{'} = \int_{-f_0}^{f_0} E^{'2}(f) \, df \cong P_e \frac{\pi^2}{3} \left(\frac{1}{OSR}\right)^3 \tag{2.11}$$

for  $f_0 \ll f_s$  (i.e.,  $OSR \ll 1$ ). The final SNR for a sinusoidal input signal can be given [3, Chapter 2] as:

$$SNR_{rms} = 6.02n + 1.76 - 5.17 + 30\log(OSR)$$

(2.12)

We see here that doubling the OSR reduces the noise by 9 dB or provides 1.5 bits of extra effective resolution for the first-order  $\Delta\Sigma$  modulator.

### Second-Order Noise Shaping

A major shortcoming of the simple  $\Delta\Sigma$  system shown in Figure 2.4 is that it may generate low-frequency (and thus in-band) tones for special values of the input x(n). To see how this may occur, assume for the moment that we are using 1-bit quantizer and 1-bit DAC in the system, and the two output levels of the 1-bit DAC are 0V and 1V, while the input x(n) is a constant voltage k/m volt where k and m are relatively prime integers and k < m. Then, it is possible to have a periodic DAC output pattern with each period m pulses long and containing k pulses of value 1V

**Figure 2.5:** A second-order  $\Delta \Sigma$  modulator.

and (m-k) pulses of 0V. The average value of the DAC output will then equal x(n), and hence the loop can settle into a steady state oscillation under these conditions. If m is sufficiently large so that  $m > f_s/f_0 = 2OSR$ , then the fundamental component  $f_s/m$  of the oscillation wave will fall into the signal band, and it may therefore appear as a sinusoid tone of considerable amplitude in the final data output, which is often called *pattern noise* [15].

One way to avoid the pattern noise is to inject an extra noise (call *dither*) into the loop, which will also reduce the dynamic range of the system [16]. Another way is to reduce the correlation between x(n) and e(n) by using a higher-order loop filter, which will also result in more selective noise shaping, and thus in an improved SNR. The modulator shown in Figure 2.5 realizes second-order noise shaping by using two cascaded integrators. For this modulator, the signal transfer function can be derived as  $S_{TF}(z) = z^{-1}$ , corresponding to a clock cycle delay, and the noise transfer function is  $N_{TF}(z) = (1 - z^{-1})^2$ , a second-order high-pass filter.

Similar calculations as in the Section 2.2.3 may give the noise power and SNR for sinusoidal signal as:

$$P'_{e} \cong P_{e} \frac{\pi^{4}}{5} (\frac{1}{OSR})^{5}$$

(2.13)

$$SNR_{rms} = 6.02n + 1.76 - 12.9 + 50\log(OSR)$$

(2.14)

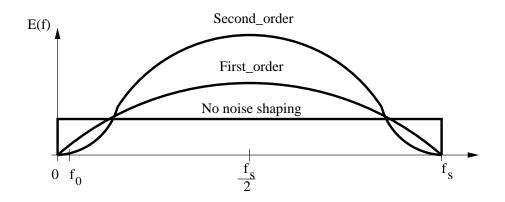

Figure 2.6: Spectral density of noise for some different noise-shaping modulation.

Therefore, doubling the OSR improves the SNR for a second-order modulator by 15 dB or, equivalently, an extra resolution of 2.5 bits/octave. A comparison for the spectral densities of noise among zero-, first-, and second-order noise-shaping modulators is shown in Figure 2.6. The noise power decreases over the signal band (i.e., from 0 to  $f_0$ ) as the noise-shaping order increases. However, the out-of-band noise increase for the higher-order modulators.

Furthermore, the generation of in-band tones is largely prevented by the added feedback path which reduces the dependence of the quantization noise on the recent values of input signal, and thus decrease their correlation. In fact, the feedback signal added to the input of the second integrator acts as a dither signal.

# 2.3 Architectures of $\Delta \Sigma A/D$ Converters

The world of  $\Delta\Sigma$  converters can be roughly divided into the following camps: single-bit single-stage low-order designs, single-bit single-stage high-order designs, multi-stage cascaded designs with feedforward error cancellation, and multibit noise shapers.

The systems shown in Figure 2.4 and 2.5 are in the first category as long as 1-bit quantizers are used. They have guaranteed stability [3, Chapter 3] with little restriction on input range and simple circuit design. However, they cannot achieve high SNR with low-to-medium oversampling ratios.

# 2.3.1 Higher-Order Single-Stage $\Delta\Sigma$ Converters

In principle, arbitrary higher-order loop filters can be used and configured in cascade structure like that in Figure 2.5. When a modulator has L loops and is not overloaded, linear analysis [16] can show that the spectral density and in-band power of the modulation noise are

$$E'(f) = \sqrt{2P_e T} [2\sin(\frac{\omega T}{2})]^L$$

(2.15)

$$P'_{e} \cong P_{e} \frac{\pi^{2L}}{2L+1} \left(\frac{1}{OSR}\right)^{2L+1}$$

(2.16)

This noise falls 3(2L-1) dB for every doubling of OSR, providing  $(L-\frac{1}{2})$  extra bits of resolution.

However, the stability of the loop becomes precarious for loop filters of order L > 2. Linearized analysis, which results in  $N_{TF}(z) = (1 - z^{-1})^L$ , is not a reliable predictor of the stability, since the 1-bit quantizer is a grossly nonlinear element whose equivalent gain varies abruptly with the value of its input. It is revealed [3, Chapter 4] that for guaranteed stability the equivalent quantizer gain must be high. Thus, with the fixed output amplitude, this will be achieved only if the quantizer input is small. To ensure this, the maximum amplitude of input must be restricted to pretty low, so as to inversely decrease the dynamic range.

In practice, the loop filter has to be carefully designed and the stability may be signal dependent. The coefficients of the filter must come from a discrete-time simulation rather than from a linear model. Another challenging aspect of stability analysis lies in establishing a "safe" input range, which is also related to the choice of the filter.

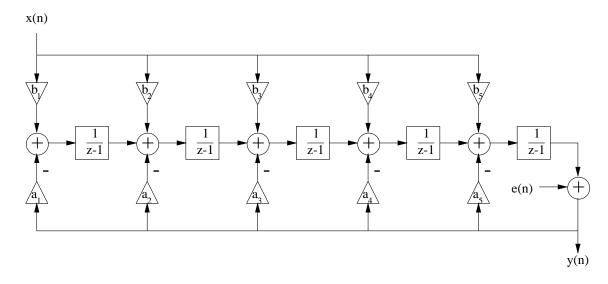

Figure 2.7: Chain of integrators with distributed feedback and distributed feedforward inputs.

There are many loop topologies to build a high-pass filter for modulation noise. One [17] is using chain of integrators with distributed feedback and distributed feedforward inputs as shown in Figure 2.7. This fifth-order modulator has the noise transfer function and signal transfer function as:

$$N_{TF}(z) = \frac{1}{1 - \frac{a_5}{z - 1} - \frac{a_4}{(z - 1)^2} - \dots - \frac{a_1}{(z - 1)^5}} = \frac{(z - 1)^5}{D(z)}$$

(2.17)

$$S_{TF}(z) = \frac{b_1 + b_2(z-1) + \ldots + b_5(z-1)^4}{D(z)}$$

(2.18)

where  $D(z) = (z-1)^5 - a_5(z-1)^4 - \ldots - a_1$ . The basic idea of adding D(z) is to introduce poles to flatten the high-frequency portion of  $N_{TF}(z)$ , so that the quantizer gain will not be too low to result in stability at high frequency.

# **2.3.2** Multi-stage (Cascade) $\Delta\Sigma$ Converters

An alternative structure for realizing higher-order noise-shaping converters, which is free of the stability problems associated with the higher-order single-stage

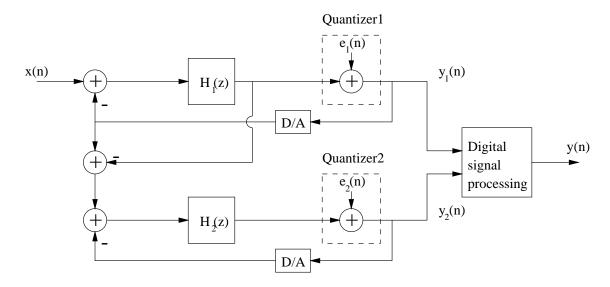

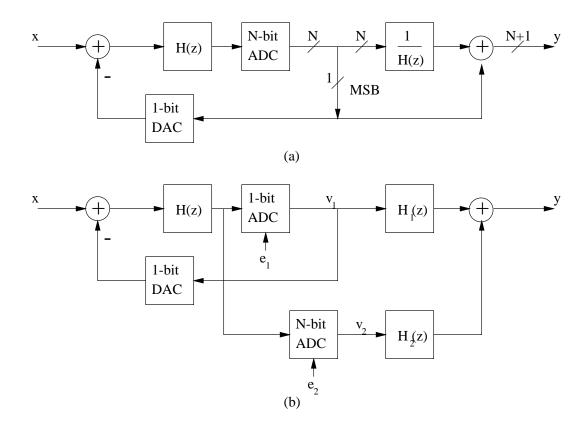

Figure 2.8: Block diagram of cascaded modulator.

converters described above, is the multi-stage or cascade architecture as shown in Figure 2.8. The overall  $\Delta\Sigma$  modulator consists of a cascade of several lower order single-loop modulators, each with its own quantizer. Each single-loop modulator in the cascade converts the quantization error from the preceding modulator. The error of all but the last single-loop modulator are then digitally canceled. The guaranteed stability is achieved by using first- and/or second-order loops in a feedforward (as opposed to feedback) configuration.

Since the design in this thesis is also a cascaded modulator, a detailed analysis will be given in the next chapter. It should be mentioned here that a major disadvantage of the cascaded structure is that the exact cancellation of the error  $e_1(n)$ requires accurate matching of the analog transfer functions  $H_1(z)$  and  $H_2(z)$  to some digital functions determined by the DSP system. If these conditions are not exactly satisfied, then unfiltered or poorly filtered noise due to  $e_1(n)$  will leak into the output data y(n), and the SNR plummets.

# **2.3.3** Multi-bit $\Delta\Sigma$ Converters

As mentioned before, one-bit  $\Delta\Sigma$  modulators employ a 1-bit internal DAC with inherent linearity that does not require precision component matching. This relax of requirement on analog components is a great attractiveness for modern VLSI technologies. However, it is easy to see from Equation (2.12) and (2.14) that employing multibit quantizers in the modulators shown in Figure 2.4 and 2.5 can dramatically increase SNR by 6 dB per additional bit. This is because the  $\Delta$  in Equation (2.2), which is the level spacing of the quantizer, will decrease by a factor of 2 per bit so that the noise power  $P_e$  decreases by a factor of 4 per bit. Equivalently, the multibit  $\Delta\Sigma$ coder can achieve resolution comparable to that of a single-bit modulator at a lower sample rate, which is a significant advantage in applications requiring high bandwidth like digital video. The lower clock rate possible within the multibit modulators may decrease power consumption in the digital circuitry. Finally, the multibit quantizer is a better approximation to a linear amplifier than a single-bit one; hence, the stability properties are better and the agreement between the behavior predicted by linear theory and the actual performance is improved. Therefore, multibit  $\Delta\Sigma$  converters are gaining popularity [18, 1, 19].

The multibit internal A/D converter must be a parallel (flash) type circuit, since stability and noise cancellation allow only one clock period for conversion. On the other hand, the ADC nonlinearity merely increases the quantization noise somewhat, and will be suppressed by the noise shaping process. By contrast, any nonlinearity of the internal feedback DAC will directly affect the output signal. This can be seen from the analysis of the linear model shown in Figure 2.9, where a(n)represents the errors caused by the deviation of the quantizer thresholds from their ideal values, i.e., ADC nonlinearity, and d(n) represents the errors due to the internal DAC nonlinearity. For noise shaping to occur, the gain of H(z) must be large at low frequencies as we saw in Section 2.2.3. Therefore, both a(n) and e(n) are reduced by

Figure 2.9: Simplified linear model of a  $\Delta\Sigma$  ADC with nonlinearity errors.

this large gain when referred back to the input x(n). However, d(n) still resides in the feedback path so that the ultimate linearity of y(n) is no better than the linearity of the N-bit internal DAC. For example, 16-bit resolution of a multibit  $\Delta\Sigma$  converter can only be achieved if the internal DAC has an accuracy of  $1/2^{16} \cong 0.0015\%$ . A direct realization of such high-precision converter (e.g. laser-trimmed resistors) is very expensive and defeats the virtue of using oversampling.

There are several alternative techniques [3, Chapter 8] for reducing the effects of DAC nonlinearity. However, a novel structure using two quantizers (Figure 2.10, proposed by Leslie and Singh [18], is easier to implement. One of the two quantizers is a single-bit circuit contained in a  $\Delta\Sigma$  loop, which includes a single-bit DAC in the feedback path. Since this DAC plays the key role in determining the linearity of the modulator, its inherent linearity is used to full advantage. An added path with a second quantizer, a multibit one, is used to convert and cancel the large quantization error generated by the single-bit quantizer. This scheme is conceptually similar to the cascade technique. Analysis of the system of Figure 2.10(b) gives for the output signal the expression as:

$$Y = H_1 V_1 + H_2 V_2 = S_{TF} (H_1 + H_2) X + (H_1 N_{TF} + H_2 N_{TF} - H_2) E_1 + H_2 E_2$$

Here,  $S_{TF}$  and  $N_{TF}$  are the signal and noise transfer functions, respectively, of the 1-bit loop;  $E_1$  and  $E_2$  are the quantization errors of the 1-bit and N-bit ADCs, respectively, in the z-domain. An appropriate choice of the H(z),  $H_1(z)$ , and  $H_2(z)$ can cancel the large error  $E_1$  by satisfying the condition

$$\frac{H_1}{H_2} = \frac{1}{N_{TF}} - 1 \tag{2.19}$$

It is usually advantageous to choose  $S_{TF}$  and the overall signal transfer function  $S_{TF}(H_1 + H_2)$  both as delays of k clock period, i.e.,  $z^{-k}$ . Then the design equations become  $H_1 = 1 - N_{TF}$ ,  $H_2 = N_{TF}$ , and

$$Y = z^{-k}X + N_{TF}E_2$$

In practice, condition (2.19) cannot be exactly satisfied due to the inaccuracy of analog  $N_{TF}$ . This inaccuracy generally makes it useless to choose the value of N larger than 3-5 bits.

## 2.4 Digital Filters for $\Delta \Sigma A/D$ Converters

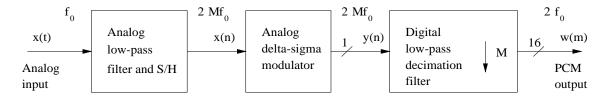

As seen in previous sections, the techniques for  $\Delta\Sigma$  A/D converters are heavily based on principles of the digital signal processing filters, which follow with the analog modulator to remove the shaped out-of-band noise, reduce the sampling rate to Nyquist rate, and increase 1-bit or several-bit data word to high-resolution sample word. The block diagram of a whole  $\Delta\Sigma$  A/D converter system is shown in Figure 2.11. In this system, x(n) and y(n) are working on oversampling rate, while y(m)is working on Nyquist rate. The process of converting a signal from a given rate to a different rate is called *sampling-rate conversion*. In a  $\Delta\Sigma$  A/D converter, the process of reducing the sampling rate is called *decimation*, while in a  $\Delta\Sigma$  D/A converter, the process of increasing the sampling rate is called *interpolation*.

Figure 2.10: (a) Leslie-Singh structure. (b) An Equivalent representation.

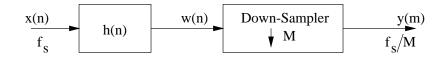

### 2.4.1 Basic Principles of Decimation

The process of decimation in the digital domain can be viewed as a linear filtering operation as shown in Figure 2.12. The input signal x(n) is characterized by the sampling rate  $f_s$ , and the output signal y(m) is characterized by  $f_s/M$ , where Mis an integer factor. The spectrum of x(n),  $X(\omega)$ , is assumed to be nonzero in the frequency interval  $0 \leq |\omega| \leq \pi$  or, equivalently,  $|f| \leq f_s/2$ . To avoid aliasing [20], the bandwidth of x(n) must first be reduced to  $f_{max} = f_s/2M$  or, equivalently,  $\omega_{max} = \pi/M$ , then the band-limited signal w(n) can be down-sampled by simply discarding M - 1 out of every M samples to produce the output y(m).

Figure 2.11: A  $\Delta\Sigma$  A/D converter system.

Figure 2.12: Decimation by a factor M.

The filter is a low-pass filter characterized by the impulse response h(n) and a frequency response  $H_M(\omega)$ , which ideally satisfies the condition

$$H_M(\omega) = \begin{cases} 1 & |\omega| \le \frac{\pi}{M} \\ 0 & otherwise \end{cases}$$

Thus the filter eliminates the spectrum of  $X(\omega)$  in the range  $\pi/M < \omega < \pi$ . Of course, the implication is that only the frequency components of x(n) in the range  $|\omega| \leq \pi/M$  are of interest in further processing of the signal.

In practice, the digital filter, while specified at the high sampling rate  $f_s$ , is actually implemented at the low rate  $f_s/M$ . This is shown by the relationship

$$y(m) = w(mM) = \sum_{k=0}^{\infty} h(k)x(mM - k)$$

Only one out of every M samples of x(n) needs to be convoluted with h(n).

### 2.4.2 Multistage Implementation

An important criterion in the design of an A/D or D/A converter is the efficiency in which the decimator or interpolator operation can be implemented. This

efficiency is directly related to the type, the order, and the architecture of the digital filter used in the implementation. In practical applications, the decimation factor Mis much larger than unity (i.e.,  $OSR \gg 1$ ), so a single-stage implementation (i.e., only one filter to do the decimation) will require a very high-order filter and may be computationally inefficient. However, a multistage implementation, which is a cascade of J decimators with  $M = \prod_{i=1}^{J} M_i$  and the sampling rate at the output of the *i*th stage  $F_i = F_{i-1}/M_i$ , for i = 1, 2, ..., J, can save pretty much computation and thus is used in most  $\Delta\Sigma$  converters.

In a multistage implementation, to ensure that no aliasing occurs in the overall decimation process, each filter stage should be designed to avoid aliasing within the frequency band of interest (e.g., from 0 to  $2f_0$ ). Let us define the passband cutoff frequency  $F_{pc} = f_0$  and the stopband cutoff frequency  $F_{sc} = F_s/2M$  for the overall decimator.<sup>3</sup> Then aliasing in the band  $0 \leq F \leq F_{sc}$  is avoided by selecting the frequency bands of each filter stage as

$$passband: \qquad 0 \le F \le F_{pc}$$

$$transitionband: \qquad F_{pc} \le F \le F_i - F_{sc} \qquad (2.20)$$

$$stopband: \qquad F_i - F_{sc} \le F \le \frac{F_{i-1}}{2}$$

The length or order of a FIR filter may be estimated from one of the well-known formulas given in the literature [20]:

$$N = \frac{D_{\infty}(\delta_p, \delta_s) - f(\delta_p, \delta_s)(\Delta f)^2}{\Delta f} + 1$$

(2.21)

$$D_{\infty}(\delta_{p}, \delta_{s}) = [0.005309(\log \delta_{p})^{2} + 0.07114(\log \delta_{p}) - 0.4761] \log \delta_{s}$$

$$-[0.00266(\log \delta_{p})^{2} + 0.5941(\log \delta_{p}) + 0.4278]$$

$$f(\delta_{p}, \delta_{s}) = 11.012 + 0.51244(\log \delta_{p} - \log \delta_{s})$$

$$\Delta f = \frac{F_{sc} - F_{pc}}{F_{s}}$$

<sup>&</sup>lt;sup>3</sup> In a practical filter design, a transition band has to be allowed, i.e.,  $F_{sc} > F_{pc}$ .

where  $\delta_p$  and  $\delta_s$  represent the passband ripple and stopband ripple, respectively. It is easy to see that in a single-stage implementation, the transition bandwidth becomes small relative to  $F_s$  (e.g., usually  $\Delta f \ll 1$ ), leading to excessively large filter orders and high-word-length requirements on the decimator. Whereas, in a multistage implementation, each stage's  $\Delta f$  (i.e.,  $(F_i - F_{sc} - F_{pc})/F_{i-1}$ ) is not so small that a relative low-order filter can be used. The total orders of all cascaded filters may be much smaller than the orders of the single filter. An example will illustrate this point in Section 4.1.

Although, in principle, an arbitrary number of stages may be used, practical considerations sometimes lead to the conclusion that a two-stage design is best. A further careful consideration of the first stage filter design can relax the filter requirement to a multiple stopband filter design [3, Chapter 13], such as a *comb* or  $sinc^{K}$  filter, which will save more computations than a conventional FIR design.

#### 2.4.3 Filter Structures

In principle, any number of classical filter design techniques can be applied to make the decimator or interpolator. However, because of the multirate and/or multistage considerations, many of these classical techniques are often ruled out in favor of designs that can take better advantage of the above multirate criteria and achieve a more effective design. These considerations often lead to the use of architectures that minimize the coefficient word lengths, eliminate the need for dedicated high-speed parallel multiplier, or reduce the memory storage requirements.

#### FIR and IIR Filters

FIR (Finite Impulse Response) and IIR (Infinite Impulse Response) filters are two basic types of digital filters. In many applications, such as high-quality digital audio, linear phase is important; hence, FIR filtering is used exclusively. In voiceband

Figure 2.13: FIR structures for decimation by a factor M. (a) Direct form. (b) Efficient direct form.

telephony applications, however, linear phase is not required so that IIR filters may be used as intermediate-stage decimators because they typically require lower order than FIR at the expense of higher internal word lengths for coefficients. In my work, FIR filters are designed due to the assumed linear phase requirement.

In principle, the simplest realization of a decimator is the direct-form FIR structure as shown in Figure 2.13(a) with system function

$$H(z) = \sum_{k=0}^{N-1} h(k) z^{-k}$$

(2.22)

Figure 2.14: Symmetrical FIR structure for decimation by a factor M.

where h(k) is the unit sample response of the FIR filter. Any of the standard, wellknown FIR filter design techniques (e.g., window methods, Parks-McClellan algorithm) [21] may be used to carry out the coefficients. Although the direct-form FIR filter realization is simple, it is also very inefficient. The inefficiency results from the fact that the down-sampling process requires only one out of every M output samples at the output of the filter. Consequently, only one out of every M possible values at the output should be computed. Thus, the logical solution to this problem is to embed the down-sampling operation within the filter as illustrated in Figure 2.13(b). Additional reduction in computation can be achieved by exploiting the symmetry characteristics of h(k) as shown in Figure 2.14.

$sinc^{K}$  Filters

The transfer function for a  $sinc^k$  decimation filter has the general form

$$H(z) = \left(\frac{1}{M} \sum_{i=0}^{M-1} z^{-i}\right)^{K} = \left(\frac{1}{M} \frac{1 - z^{-M}}{1 - z^{-1}}\right)^{K}$$

(2.23)

and its frequency response is therefore

$$|H(e^{j\omega})| = \left(\frac{1}{M} \frac{\sin(\omega M/2)}{\sin(\omega/2)}\right)^{\kappa} = \left(\frac{\operatorname{sinc}(\omega M/2)}{\operatorname{sinc}(\omega/2)}\right)^{\kappa}$$

(2.24)

where  $\omega = 2\pi f/f_s$ . It has M/2 spectral zeros if M is even, or  $\lceil M/2 \rceil - 1$  zeros if M is odd, at frequencies that are multiples of the decimated sampling frequency  $\omega_d$ . These zeros correspond to multiple notches or stopbands which are wide enough to cover the required stopband widths of the decimator specification as mentioned in Section 2.4.2. Therefore, this class of filters can be applied to the first stage of a multistage decimator.

Note that the  $sinc^{K}$  filter is actually a cascade of K averaging filters and its impulse response is finite, implying it is an FIR filter. In addition, all of its impulse response coefficients are symmetric (in fact, they are all equal to unity so that no multiplications need to be implemented in hardware), and thus it is also a linearphase filter. A  $sinc^{4}$  filter design will be presented in Chapter 4.

### Half-Band Filters

Half-band filters are characterized by the constraints that their passband and stopband ripples are the same (i.e.,  $\delta_p = \delta_s$ ) and that the cutoff frequencies are symmetrical around  $\pi/2$  such that

$$\omega_p + \omega_s = \pi \tag{2.25}$$

This class of filters exhibits odd symmetry around  $\pi/2$  and has zero impulse response h(n) for all even values of n except n = 0, i.e., almost half of the filter's coefficients are zero. Therefore, these filters can be implemented with half the number of multiplications than arbitrary choices of FIR filter designs. They are appropriate for sampling rate conversion ratios of 2:1 [22].

From Equation (2.20), we may see that if half-band filters are used as the intermediate decimators, aliasing will occur in the final transition band from  $F_{pc}$  to

$F_{sc}$ . This transition band aliasing is a very useful and important technique that leads to a large savings in filter complexity, especially in the last stage of the decimator, as we will see from the design in Chapter 4.

# Chapter 3

# ANALOG MODULATOR DESIGN

In commercial applications, oversampling  $\Delta\Sigma$  converters have been successfully used for high-resolution signal acquisition in voice-band, digital audio, and ISDN fields, which have signal bands less than 100 KHz. The next significant telecommunication application for  $\Delta\Sigma$  converters will be digital video with bandwidth less than 10 MHz. It is obvious that the oversampling ratio in the range of 64 to 512, typically used in oversampling converters, is impractical for such high-speed application. Alternative modulator structures are needed, working at low oversampling ratios to achieve moderate 10-12 bit resolution while maintaining the relative simplicity of analog circuit design. Dr. Brian Brandt [1] [3, Chapter 7] has implemented such a structure for 12-b 2.1 MHz conversion with OSR = 24 in a 1- $\mu m$  CMOS technology, which is so far the fastest  $\Delta\Sigma$  ADC. In my thesis work, an equivalent modulator is re-designed in a 0.8- $\mu m$  CMOS technology with a few modifications of the analog circuits.

#### **3.1** A Cascaded Multibit $\Delta \Sigma$ Modulator

The goal of this modulator design is to reduce the oversampling ratio to as low as 16 while maintaining a dynamic range of 74 dB or, equivalently, a resolution of 12 bits, for conversion rates above 1 MHz.

## **3.1.1** $\Delta\Sigma$ Modulation at Low Oversampling Ratios

The dynamic range of  $\Delta\Sigma$  modulator employing pure differentiation noise transfer functions depends on the oversampling ratio OSR, the order of noise shaping

(b)

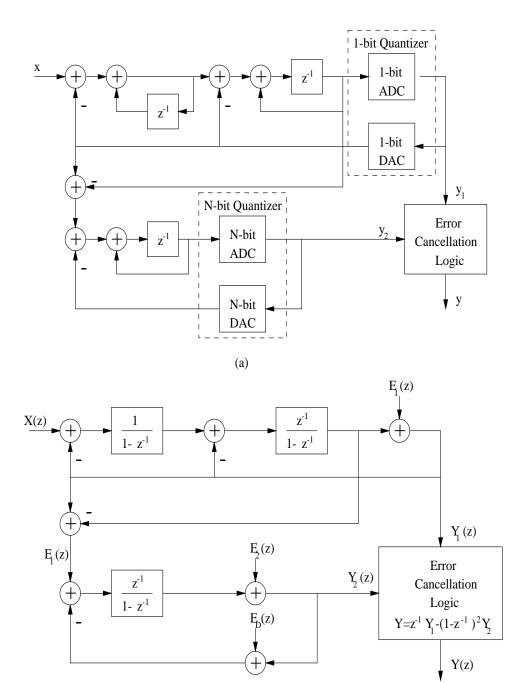

Figure 3.1: Block diagram of a third-order cascaded multibit  $\Delta\Sigma$  A/D converter.

L, and the internal quantizer resolution N, according to [23]

$$DR = \frac{3}{2} \left(\frac{2L+1}{\pi^{2L}}\right) (2^N - 1)^2 OSR^{2L+1}$$

(3.1)

At a given OSR, the dynamic range may be extended by increasing L or by increasing N. Due to the term  $OSR^{2L+1}$  in Equation (3.1), the effectiveness of increasing the order of noise shaping is significantly diminished as the oversampling ratio is reduced. In contrast, the effectiveness of increasing the quantizer resolution is independent of the oversampling ratio and is therefore particularly attractive for applications at low oversampling ratios. For example, when a 4-bit quantizer is used instead of a 1-bit quantizer, the dynamic range increases nearly  $20 \log(2^4 - 1) \cong 24$  dB.

However, as mentioned in Section 2.3.3, linearity and resolution of a modulator based on a multibit quantizer are limited by the precision of the multibit D/Aconverter. To reduce this dependence on DAC linearity, several methods [3, Chapter 8], including element swapping and digital calibration, have been proposed. An alternative method is described here.

#### 3.1.2 Linear Analysis of the Modulator

The cascaded multibit modulator shown in Figure 3.1(a) avoids sensitivity to the DAC precision by placing the multibit quantizer in the final stage of a thirdorder cascaded modulator. The more critical first-stage quantizer has only two analog output levels and is therefore inherently linear. The modulator consists of a secondorder stage with a 1-bit quantizer followed by a first-order stage with a multibit quantizer. The input to the second stage is the difference between the output and the input of the first-stage quantizer, i.e., the quantization error of the first stage.

Shown in Figure 3.1(b) is a linear approximation of this modulator, wherein the quantizers are modeled by signal-independent additive error sources, while the integrators are represented by their transfer functions in the z-domain. The z-transform

of the output of the first stage is

$$Y_1(z) = z^{-1}X(z) + (1 - z^{-1})^2 E_1(z)$$

(3.2)

where  $E_1(z)$  models the quantization noise of the 1-bit quantizer. The input to the second stage is  $E_1(z)$  and the transform of the second-stage output is

$$Y_2(z) = z^{-1}[E_1(z) - E_D(z)] + (1 - z^{-1})E_2(z)$$

(3.3)

where  $E_2(z)$  models the quantization noise of the N-bit quantizer and  $E_D(z)$  models the nonlinearity error of the N-bit DAC. The digital error cancellation logic combines the outputs from the two stages according to

$$Y(z) = z^{-1}Y_1(z) - (1 - z^{-1})^2 Y_2(z)$$

(3.4)

so as to cancel the quantization error  $E_1(z)$  of the first stage in the final output:

$$Y(z) = z^{-2}X(z) + z^{-1}(1 - z^{-1})^2 E_D(z) - (1 - z^{-1})^3 E_2(z)$$

(3.5)

Thus, ideally the quantization error of the first stage is canceled and the quantization error of the second stage is attenuated in the passband by third-order shaping. Also, because  $E_2(z)$  originates from a multibit quantizer, the dynamic range is improved according to Equation (3.1).

More importantly, the nonlinearity error  $E_D(z)$  is attenuated in the passband by second-order shaping so that the cascaded multibit modulator much more tolerant of DAC nonlinearity than the single-stage modulator. Simulation shows that, to achieve 12-bit dynamic range, this modulator requires a DAC accuracy of only 6 bits (i.e., about 1.5% accuracy).

#### 3.2 Modified Modulator with Interstage Coupling

In practical design of the cascaded modulator, some subunity gain factors have to be added for the integrators in Figure 3.1 in order to avoid overload at

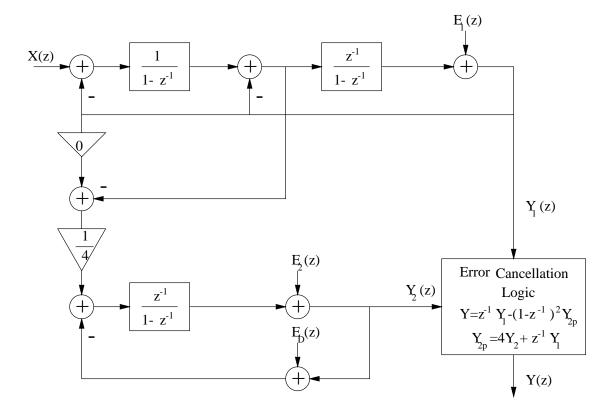

Figure 3.2: A cascaded multibit  $\Delta \Sigma$  ADC with interstage coupling.

the second stage and maintain largest signal range allowed by the power supplies. Also, trade-offs have to be considered to determine the resolution N of the multibit quantizer and simplify the circuit design. Brandt has experimented several alternative choices and concluded that the measured difference in dynamic range among them was negligible [1]. Therefore, the choice with the simplest circuit design is used in this thesis work.

# 3.2.1 Interstage Coupling

It is preferable that both stages in the modulator have the same input range, which is defined by the two levels of the 1-bit DAC or by the two outermost levels of the N-bit DAC, in order to utilize the maximum signal swing allowed by the power supplies and also to reduce the number of required voltage references. If unity gains are used for the summation nodes in Figure 3.1(b), however, the large amplitude of the quantization error produced by the second-order first stage would overload the input range of the second stage and therefore the input range of the first stage must be reduced.

To reduce the signal range at the input to the second stage while keeping the same input range for both stages, some kind of interstage coupling coefficients should be added around the interstage summation node. An empirical selection of the interstage coupling coefficients results in a modified version of the modulator shown in Figure 3.2. In this configuration, the interstage subtraction node is actually not needed at all due to the coefficient 0 so that the complexity of the modulator is reduced. The gain coefficient  $\frac{1}{4}$  reduces the output of the second integrator to onefourth to avoid overloading the input range of the second stage. Due to these two coefficients, the  $Y_2(z)$  in Equation (3.4) must be replaced by

$$Y_{2p}(z) = 4Y_2(z) + z^{-1}Y_1(z)$$

(3.6)

so as to prevent the overall output Y(z) from containing  $E_1(z)$ .

The trade-offs concerning the selection of appropriate coupling coefficients are presented in [1, 24].

### 3.2.2 Multibit Quantizer

In principle, the multibit quantizer resolution N can be increased indefinitely to improve the dynamic range. However, in practical implementations, increasing the resolution of the multibit quantizer reduces the second-stage quantization noise and thereby increases the sensitivity to uncanceled quantization noise from the first range.

The cancellation of  $E_1(z)$  depends on the noise shaping performed in the first stage precisely matching the shaping provided by the error cancellation logic. In practical, the first-stage noise shaping deviates from  $(1 - z^{-1})^2$  because of circuit nonidealities such as gain errors from capacitor mismatch and dc gain in the opamps so that  $E_1(z)$  cannot be totally canceled. Thus, increasing the resolution N of the multibit quantizer in the second stage increases the sensitivity to gain errors. At increasing levels of gain error, the performance of the modulator becomes dominated by uncanceled first-stage noise, and less benefit is derived from increasing the secondstage quantizer resolution.

The resolution can be tailored to the expected capacitor matching of the fabrication process. For a moderate 2% gain error margin, the benefit of a 4-bit quantizer over a 3-bit quantizer does not justify doubling the size of the second-stage quantizer. Hence, a 3-bit quantizer was chosen for the second stage.

# 3.2.3 Modified Integrators

Figure 3.3 shows the approximate structure of the practical modulator, where a 3-bit quantizer is used in the second stage. Two modifications of the modulator in Figure 3.1(b) are evident in the practical structure. First, both integrators in the first stage include delays in their forward paths, as well as gain factors of one-half at their inputs. Thus, the transfer function of both first-stage integrators is

$$H(z) = \frac{1}{2} \frac{z^{-1}}{1 - z^{-1}} \tag{3.7}$$

An extraction of the modified architecture from the ideal structure results in a configuration with an attenuation of 0.5 preceding the first integrator and a gain of 2 at the input of the second integrator [25]. However, since the second integrator is followed immediately by a single-threshold (1-bit) quantizer, its gain can be adjusted arbitrarily without impairing the performance of the modulator. Hence, the output of the first stage given in Equation (3.2) is changed only slightly to include an additional

**Figure 3.3:** Modified structure of the third-order cascaded multibit  $\Delta \Sigma$  ADC. Note that the  $Y_{2p}$  is defined in Equation (3.6).

delay  $(z^{-1})$  preceding X(z). Moreover, simulations reveal that this configuration reduces the signal range required at the outputs of the first-stage integrators to about 1.7 times the modulator's input range.

The second modification present in Figure 3.3 is that the input to the second stage is simply the output of the second integrator in the first stage. The combination of this simple interstage coupling and the  $\frac{1}{2}$  gain factors in the first-stage integrators implements the configuration shown in Figure 3.2.

In practical implementations, the modulator's performance may be degraded by integrator leakage resulting from the finite dc gain of operational amplifiers, which introduces a subunity factor for  $z^{-1}$  in the denominator of Equation (3.7). Simulations show that approximately 60 dB of dc gain is required to prevent performance degradation and maintain a 12-bit dynamic range.

Figure 3.4: Top-level schematic of the modulator.

## 3.3 VLSI Implementation

The analog modulator is implemented in a  $0.8-\mu m$  CMOS technology supplied by MOSIS (see Appendix A) through full-custom design methods. The performance objective is a Nyquist conversion rate of 2.1 MHz and a dynamic range of 12 bits while operating under 50 MHz clocks and from a single 5-V power supply. This section mainly discusses design issues for all of the building blocks in the modulator. All of the circuit diagrams are generated by **Design Architect**, a schematic capture tool in Mentor Graphics EDA system installed in the VLSI Lab.

## 3.3.1 Top-Level Structure of the Modulator