# FEASIBILITY STUDY FOR THE IMPLEMENTATION OF GLOBAL POSITIONING SYSTEM BLOCK PROCESSING TECHNIQUES IN FIELD PROGRAMMABLE GATE ARRAYS

A Thesis Presented to

The Faculty of the

Fritz J. and Dolores H. Russ

College of Engineering and Technology

Ohio University

In Partial Fulfillment

of the Requirements for the Degree

Master of Science

by

Sanjeev Gunawardena

November, 2000

### THIS THESIS ENTITLED

# "FEASIBILITY STUDY FOR THE IMPLEMENTATION OF GLOBAL POSITIONING SYSTEM BLOCK PROCESSING TECHNIQUES IN FIELD PROGRAMMABLE GATE ARRAYS"

by Sanjeev Gunawardena

has been approved

for the School of Electrical Engineering and Computer Science

and the Russ College of Engineering and Technology

Janusz A. Starzyk Professor of Electrical Engineering

Jerrel R. Mitchell, Dean Fritz J. and Dolores H. Russ College of Engineering and Technology

#### ACKNOWLEDGMENTS

First and foremost, I must thank God for giving me the wisdom and strength to complete this work. I firmly believe that my faith in Him has brought me through this and many trials in life. I continue to give Him all the glory and honor He so rightly deserves.

Special thanks to my wife, Amali, for standing by my side, believing in me and encouraging me through this project. Without her prayers and undying support, this work would not have been completed. Thanks also to my daughter, Serendipity (7 months) who probably did not appreciate those times when Thathi (Daddy) had to go work on his thesis rather than play with her. Thanks to my parents for their prayers, support, and encouragement; my mother, who at times gave most of her paycheck to fund my electronics projects as a child, and my father who showed me the value of education and was instrumental in giving me the opportunity to study in the US.

A special thanks to my advisor, Dr. Starzyk, whom I have known and respected since my days as a sophomore at Ohio University. Not only is Dr. Starzyk responsible for teaching me most of what I know about hardware design during those six years, but he has been there for me numerous times; from understanding why an assignment was late, to making sure I had the opportunity to go to graduate school by nominating me to receive teaching assistantships. I appreciate the patience Dr. Starzyk had with me especially during the final days of completing this thesis. I also thank him for having faith in me to teach his VLSI design sequence while he was on sabbatical. That experience boosted my self esteem, and helped me discover talents I didn't know I had.

Special thanks to Dr. Frank van Graas for giving me the opportunity to work on this project. Without that summer internship, this work would not have been possible. I appreciate all those insightful discussions we had and thank him for letting me sit-in on his classes where I learned much more than GPS. Frank has been an invaluable resource and a great motivator.

Thanks to my graduate committee: Dr. Celenk, Dr. Curtis and Dr. Hunt for their time and helpful comments and suggestions. Dr. Hunt has given me many opportunities to shine while I worked for him in the Physics Department. Special thanks to Dr. Maarten Uijt de Haag for his suggestions, advice, and support; and for attending the defense of this thesis.

I must thank Ms. Gang Feng for providing the GPS dataset used in this work, and some of the results presented in Table 4.1. Thanks also to Dr. Chris Bartone for his helpful comments. Thanks to Jonathon Sayre for the many insightful discussions we had about block processing, and for showing me how to cool the Triple7 computer in order to run my simulations. Finally, thanks to all my friends and colleagues of the Avionics Engineering Center at Ohio University for their help and support in so many ways that are too numerous to mention.

## **TABLE OF CONTENTS**

| A | CKNO   | OWLEDGMENTS                          | iii  |

|---|--------|--------------------------------------|------|

| T | ABLE   | OF CONTENTS                          | iv   |

| L | IST OI | F TABLES                             | vii  |

| L | IST OI | F FIGURES                            | viii |

| S | YMBO   | LS AND ABBREVIATIONS                 | xii  |

| 1 | INT    | RODUCTION                            | 1    |

| 2 | TH     | E GLOBAL POSITIONING SYSTEM          | 7    |

|   | 2.1    | Positioning With GPS                 | 8    |

|   | 2.2    | GPS Link Budget                      | 12   |

|   | 2.3    | GPS Signal Structure                 | 13   |

|   | 2.4    | SV-to-User Dynamics                  | 15   |

| 3 | GPS    | S RECEIVER ARCHITECTURE              | 16   |

|   | 3.1    | Overview of Generic GPS-SPS Receiver | 16   |

|   | 3.2    | Tracking Loops                       | 20   |

|   | 3.2.   | 1 Carrier Tracking                   | 21   |

|   | 3.2.2  | 2 Code Tracking                      | 22   |

|   | 3.3    | Signal Acquisition                   | 23   |

| 4 | BLO    | OCK PROCESSING GPS RECEIVER          | 29   |

|   | 4.1    | GPS Data Collection System           | 30   |

|   | 4.2 | GPS Fast Correlator                                |    |

|---|-----|----------------------------------------------------|----|

|   | 4.3 | Block Processing Hardware Performance Measures     | 40 |

|   | 4.3 | .1 Acquisition Margin and Implementation Loss      | 40 |

|   | 4.3 | .2 Code Phase Detection and Range Error            |    |

|   | 4.4 | Applications of Block Processing                   |    |

|   | 4.5 | Real Time Block Processing GPS Receiver            | 51 |

| 5 | FI  | ELD PROGRAMMABLE GATE ARRAYS                       | 54 |

|   | 5.1 | Introduction to FPGAs                              | 54 |

|   | 5.2 | Architecture of Xilinx XC4000 Series FPGAs         | 55 |

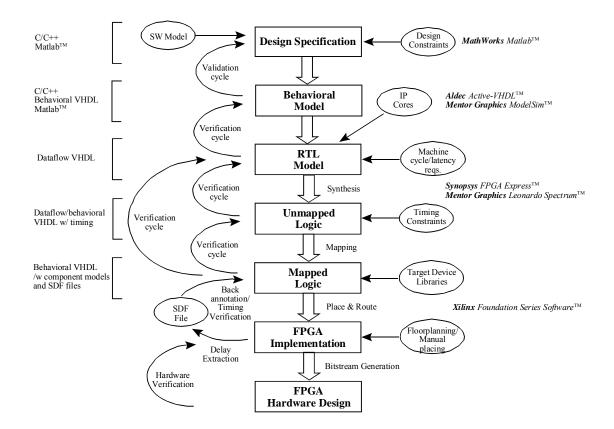

|   | 5.3 | FPGA Based Design Flow                             | 60 |

| 6 | DE  | SIGN OF 5000 POINT FFT/IFFT                        | 65 |

|   | 6.1 | The Fast Fourier Transform Algorithm               | 65 |

|   | 6.2 | The Inverse FFT                                    | 67 |

|   | 6.3 | Radix-2 FFT Building Block                         | 68 |

|   | 6.4 | Radix-4 FFT Building Block                         |    |

|   | 6.5 | Winograd Radix-5 FFT Building Block                | 73 |

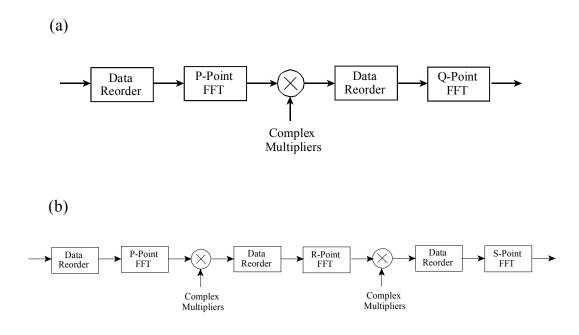

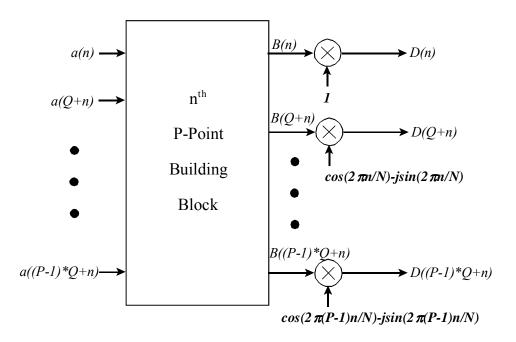

|   | 6.6 | Mixed-Radix Approach to FFT Algorithm Construction | 74 |

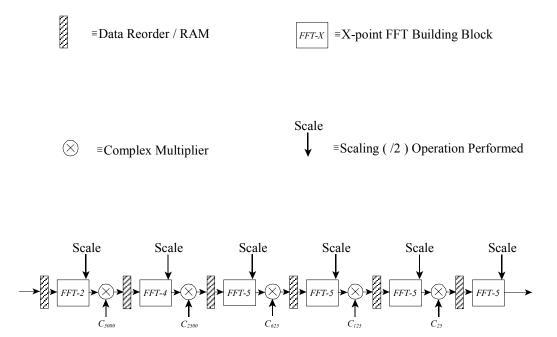

|   | 6.7 | The 5000-Point FFT/IFFT Algorithm                  | 78 |

| 7 | DE  | SIGN OF GPS BLOCK PROCESSING DATAPATH IN FPGA      |    |

|   | 7.1 | Numerically Controlled Oscillator                  | 85 |

|   | 7.2 | Complex Multiplier                                 | 80 |

v

|   |       |                                                    | vi   |

|---|-------|----------------------------------------------------|------|

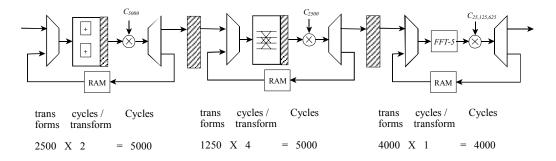

|   | 7.3   | FFT/IFFT Datapath                                  | . 92 |

| 8 | BLO   | OCK PROCESSING HARDWARE SIMULATIONS                | . 96 |

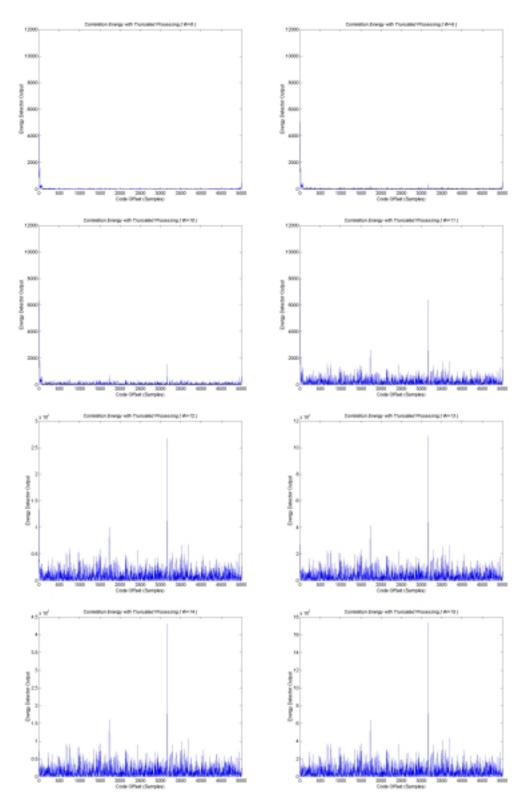

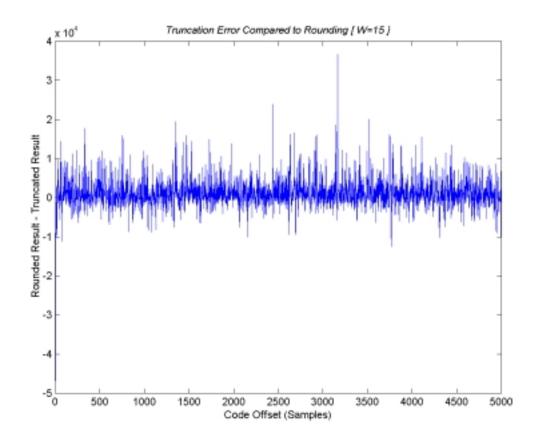

|   | 8.1   | Effect of Truncation                               | . 99 |

|   | 8.2   | Effect of ADC Quantization                         | 102  |

|   | 8.3   | Effect of Carrier NCO Amplitude Quantization       | 110  |

|   | 8.4   | Effect of Finite-Precision Hardware Processing     | 115  |

|   | 8.5   | The Optimum Block Processing Hardware Architecture | 120  |

| 9 | SUN   | MMARY AND CONCLUSIONS                              | 127  |

| R | EFERI | ENCES                                              | 130  |

| A | BSTRA | АСТ                                                |      |

## LIST OF TABLES

| Table 4.1 | GPS Data Set Parameters | 33 | 3 |

|-----------|-------------------------|----|---|

|-----------|-------------------------|----|---|

## LIST OF FIGURES

| Figure 2.1  | Graphical Illustration of Tri-Lateration                             | 8    |

|-------------|----------------------------------------------------------------------|------|

| Figure 2.2  | GPS Satellite Constellation (Not to Scale)                           | 9    |

| Figure 2.3  | GPS Satellite Global Visibility Profile                              | 10   |

| Figure 2.4  | GPS Link Budget                                                      | 12   |

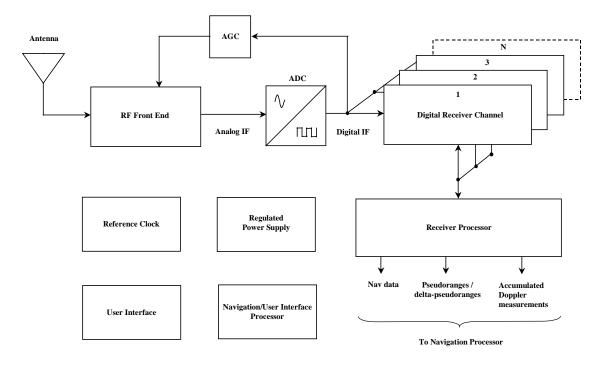

| Figure 3.1  | Block Diagram of a Generic GPS Receiver                              | 17   |

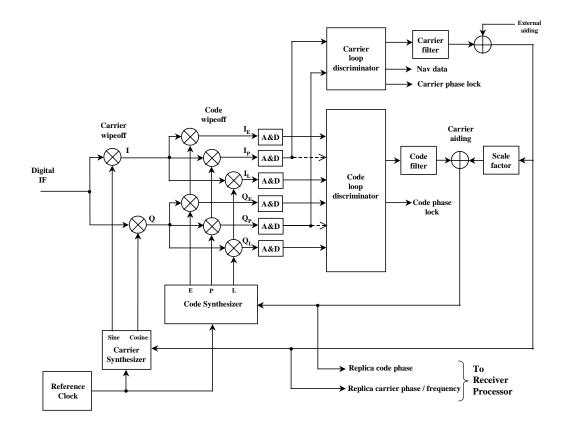

| Figure 3.2  | Block Diagram of a GPS Receiver Channel                              | 21   |

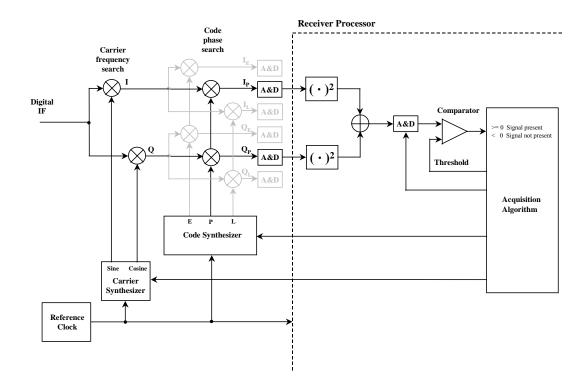

| Figure 3.3  | GPS Acquisition Configuration within a Receiver Channel              | 24   |

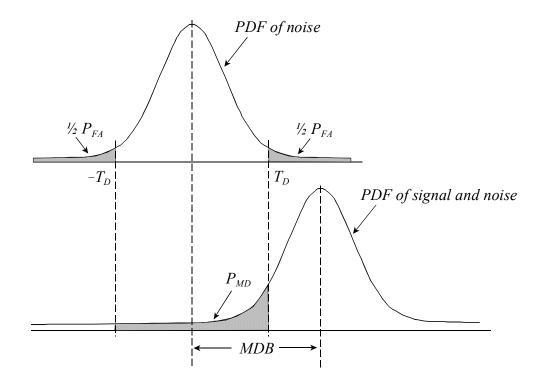

| Figure 3.4  | Illustration of $P_{MD}$ , $P_{FA}$ , and $MDB$ using Gaussian PDFs  | 25   |

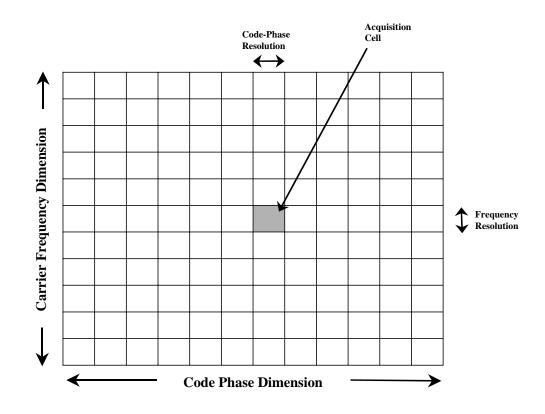

| Figure 3.5  | GPS Acquisition Search Space                                         | 26   |

| Figure 4.1  | Illustration of Block Processing for a Block of Five Samples         | 30   |

| Figure 4.2  | GPS-SPS Data Collection System                                       | 31   |

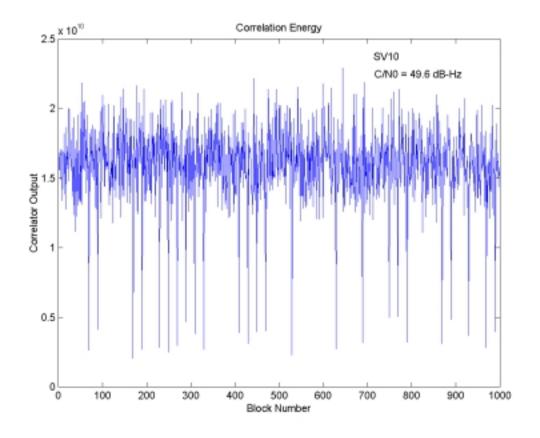

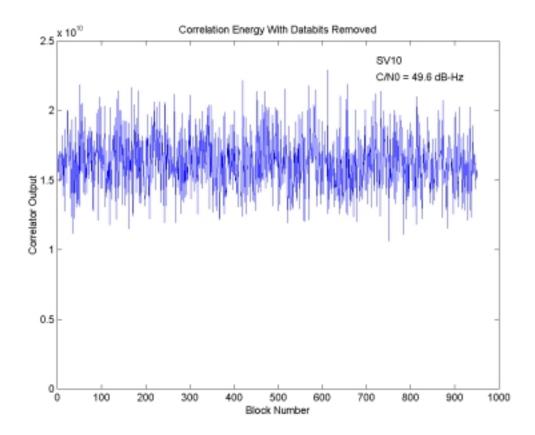

| Figure 4.3  | Correlation Energy Amplitudes for Each Block in Data Set             | 35   |

| Figure 4.4  | Correlation Energy Amplitudes with Databit-Transitioning Blocks Remo | oved |

|             |                                                                      | 36   |

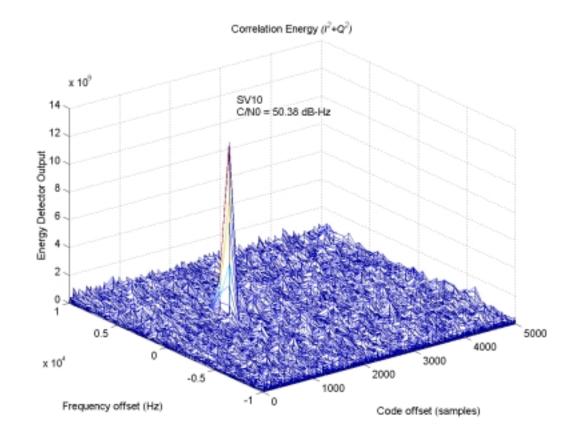

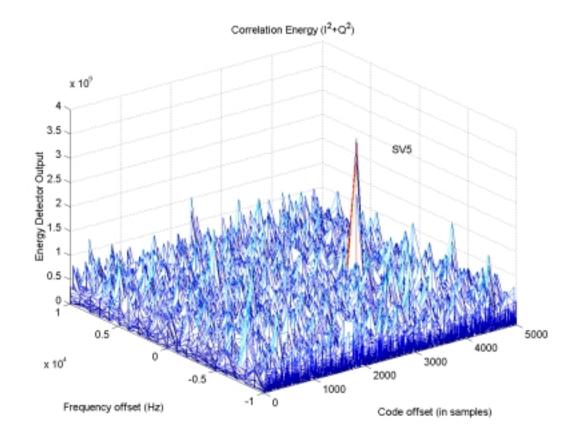

| Figure 4.5  | Fast Correlation Based GPS Signal Acquisition                        | 38   |

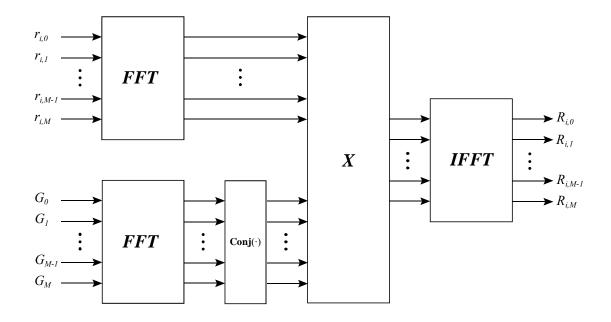

| Figure 4.6  | Block Diagram of GPS Fast Correlator                                 | 39   |

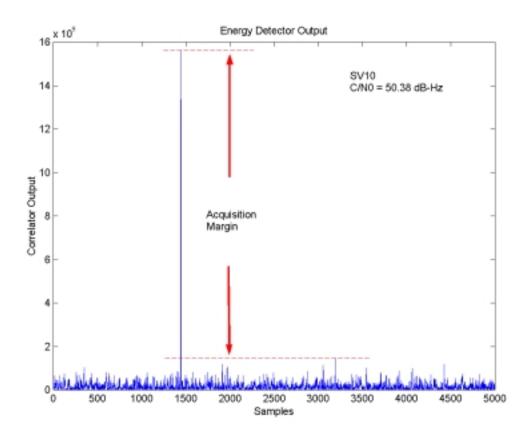

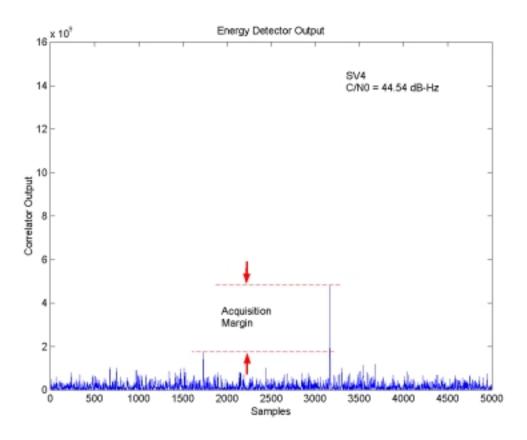

| Figure 4.7  | Correlation Peak for a 50 dB-Hz Signal                               | 41   |

| Figure 4.8  | Correlation Peak for a 45 dB-Hz Signal                               | 42   |

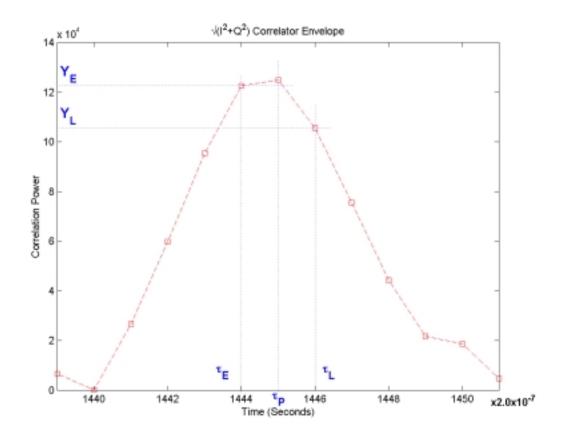

| Figure 4.9  | Illustration of Code Phase Measurement Parameters                    | 44   |

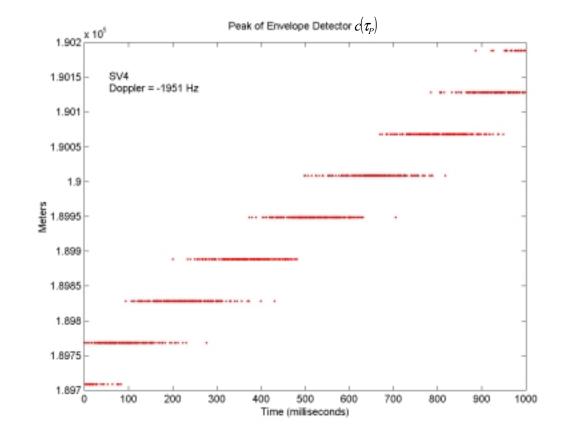

| Figure 4.10 | Envelope Detector Peak Location Showing Relative Motion of SV        | 45   |

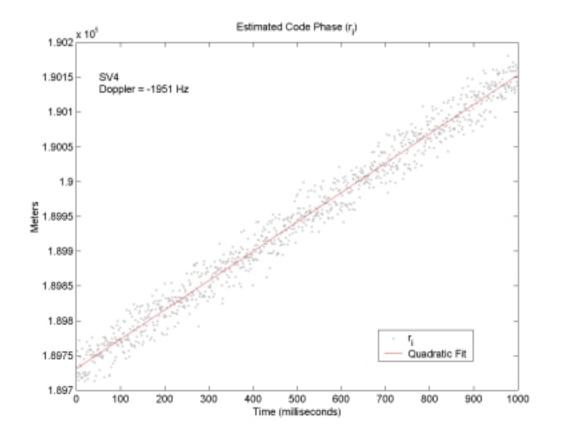

| Figure 4.11 | Estimated Code Phase Measurements for a Period of One Second              | 46    |

|-------------|---------------------------------------------------------------------------|-------|

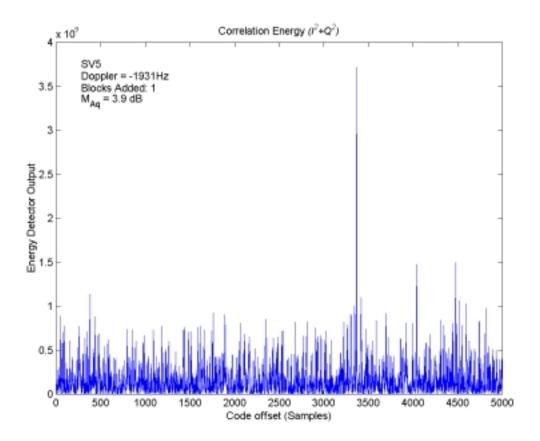

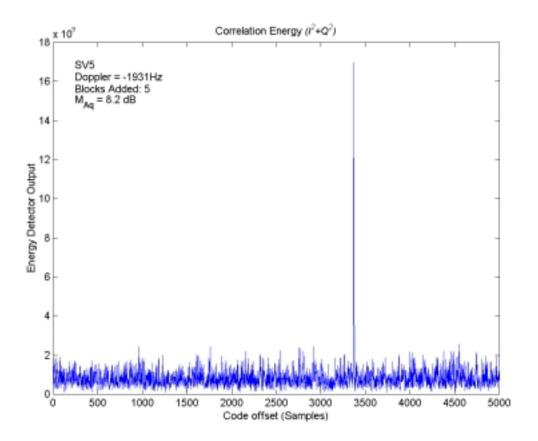

| Figure 4.12 | Acquisition of a weak GPS signal                                          | 48    |

| Figure 4.13 | Fast Correlator Output for Weak GPS signal                                | 49    |

| Figure 4.14 | Result of Block Addition Technique Applied to Weak GPS Signal             | 50    |

| Figure 4.15 | System Diagram of Real-Time Block Processing GPS Receiver                 | 52    |

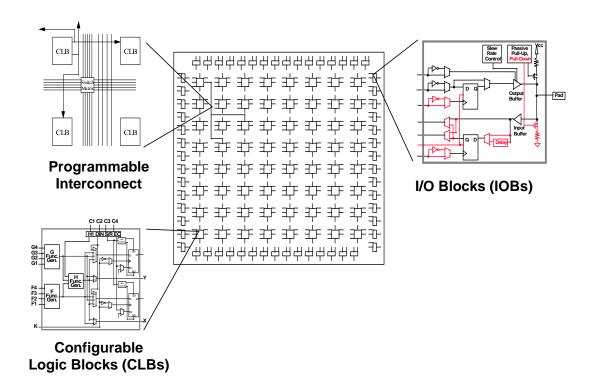

| Figure 5.1  | Anatomy of an FPGA [Xilinx99]                                             | 56    |

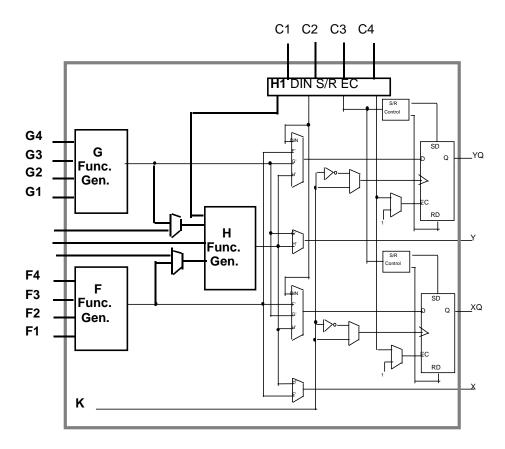

| Figure 5.2  | XC4000 Configurable Logic Block [Xilinx99]                                | 58    |

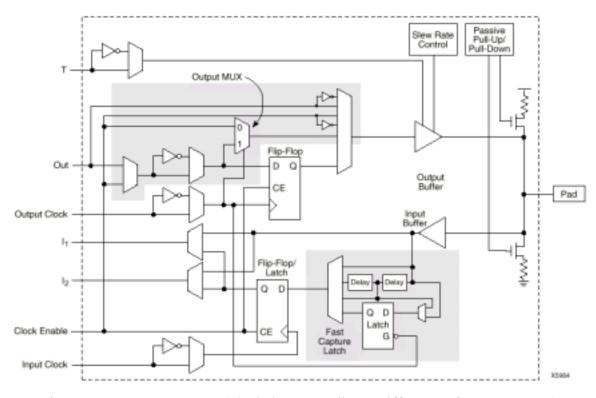

| Figure 5.3  | XC4000X IOB (Shaded Areas Indicate Differences from XC4000E)              |       |

| [Xili       | inx99]                                                                    | 59    |

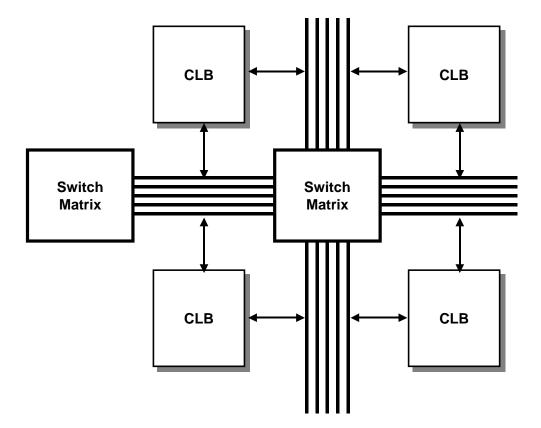

| Figure 5.4  | XC4000 Interconnect Scheme [Xilinx99]                                     | 60    |

| Figure 5.5  | Typical FPGA Design Flow                                                  | 61    |

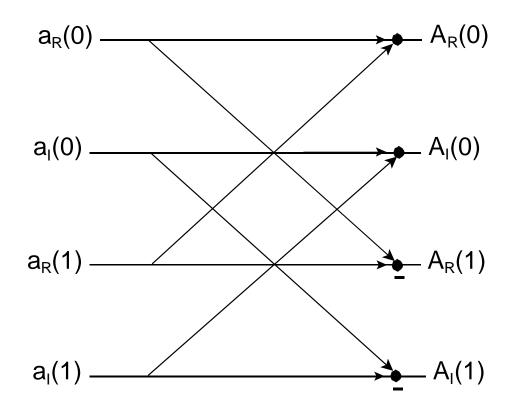

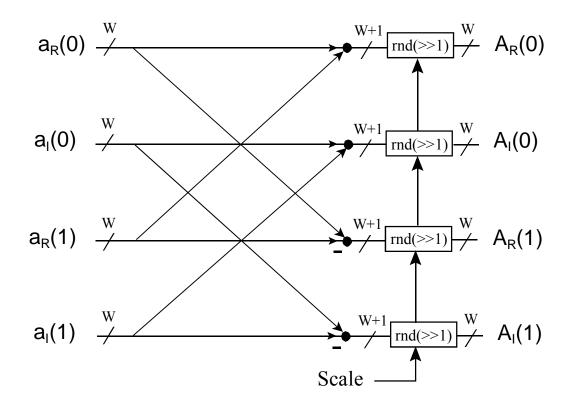

| Figure 6.1  | Radix-2 FFT Signal Flow Graph                                             | 68    |

| Figure 6.2  | Radix-2 FFT Computation in Hardware                                       | 70    |

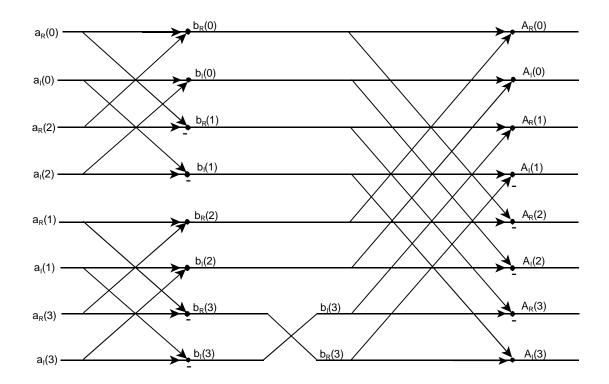

| Figure 6.3  | Radix-4 FFT Signal Flow Graph                                             | 71    |

| Figure 6.4  | Radix-4 FFT Computation in Hardware                                       | 72    |

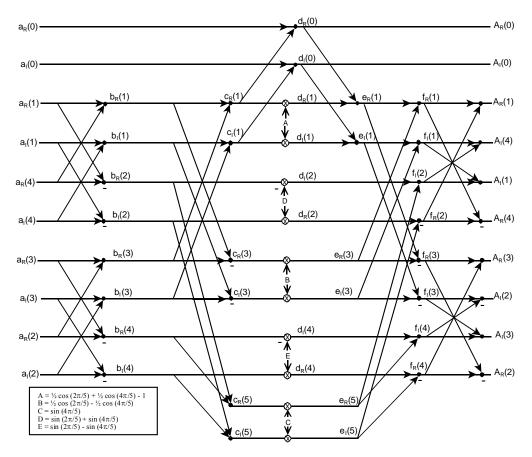

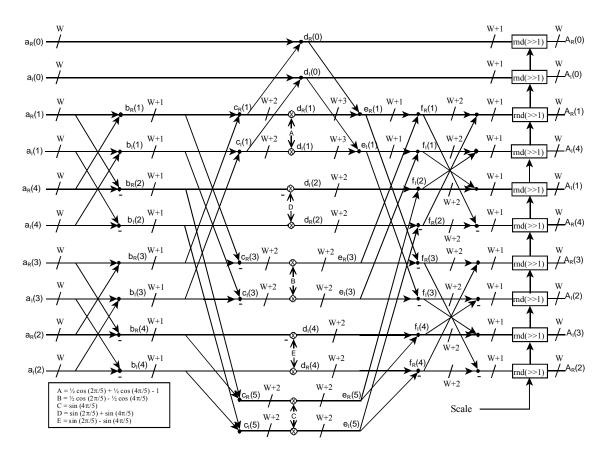

| Figure 6.5  | Winograd Radix-5 FFT Signal Flow Graph                                    | 73    |

| Figure 6.6  | Winograd Radix-5 FFT Computation in Hardware                              | 74    |

| Figure 6.7  | Two-Factor and Three-Factor Mixed-Radix FFT Construction                  | 75    |

| Figure 6.8  | <i>n<sup>th</sup></i> P-point Building-Block Output's Complex Multipliers | 76    |

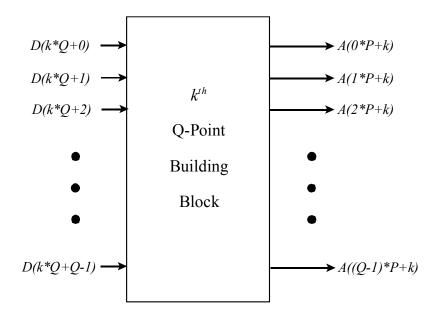

| Figure 6.9  | $k^{th}$ Q-point building block input's connections                       | 77    |

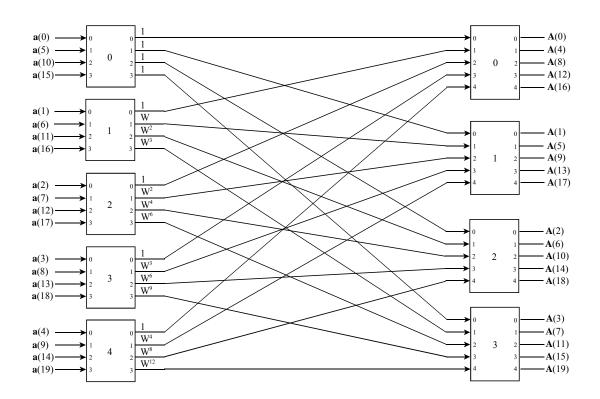

| Figure 6.10 | 20-Point Mixed-Radix FFT Constructed from 4-Point and 5-Point Bui         | lding |

| Bloc        | ks                                                                        | 78    |

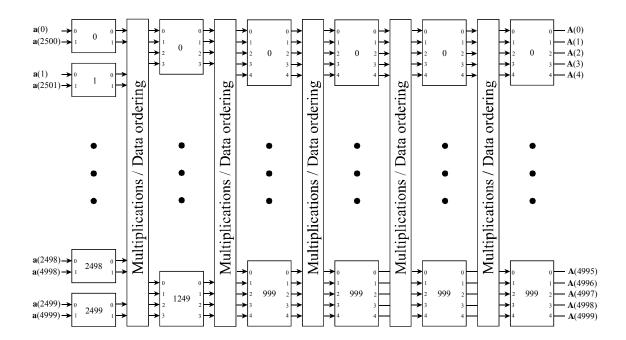

| Figure 6.11 | 5000-Point FFT Block Diagram                                          | 79  |

|-------------|-----------------------------------------------------------------------|-----|

| Figure 6.12 | 5000-Point FFT Algorithm after Vertical Projection                    | 80  |

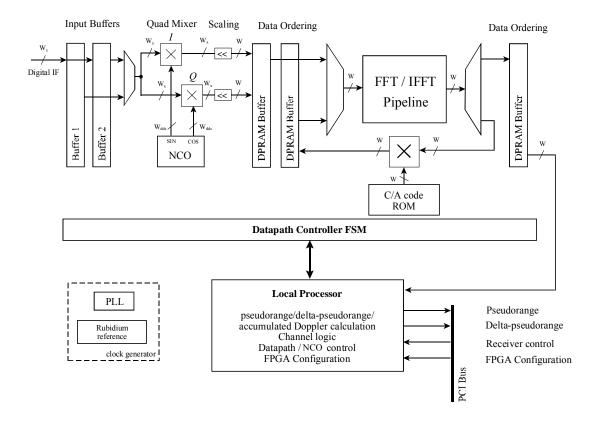

| Figure 7.1  | Block Diagram of FPGA Fast Correlator Processor                       | 82  |

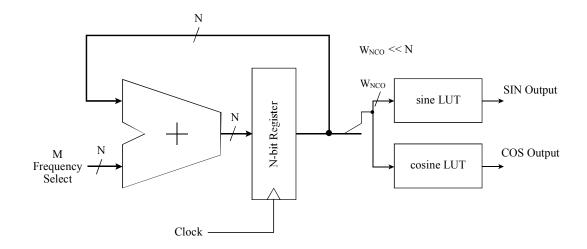

| Figure 7.2  | Block Diagram of Carrier NCO                                          | 86  |

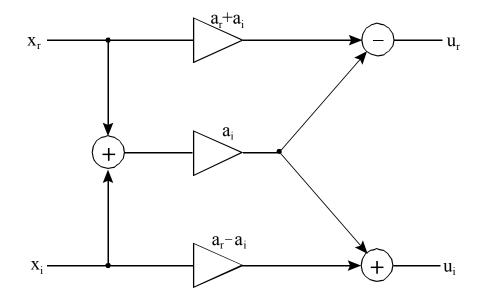

| Figure 7.3  | Complex Multiplier Structure Using Three Real Multipliers             | 90  |

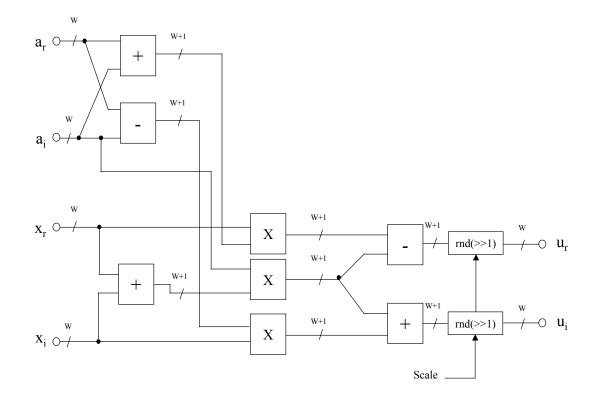

| Figure 7.4  | Block Diagram of Hardware Complex Multiplier                          | 91  |

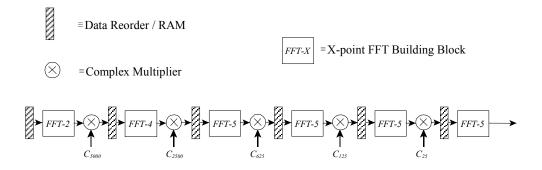

| Figure 7.5  | 5000-Point FFT/IFFT Structure Showing Scaling Distribution            | 93  |

| Figure 7.6  | Processing-Cycle optimized 5000-Point FFT/IFFT Datapath               | 95  |

| Figure 8.1  | Plots Showing the Effect of Truncation on the Datapath from W=8 to    |     |

| W=]         | 15                                                                    | 100 |

| Figure 8.2  | Difference Between Rounded and Truncated Processing Schemes           | 101 |

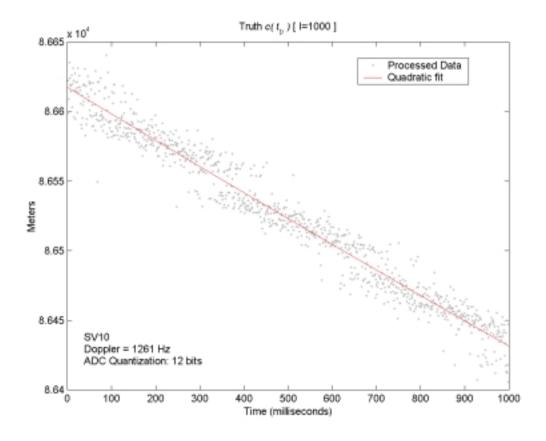

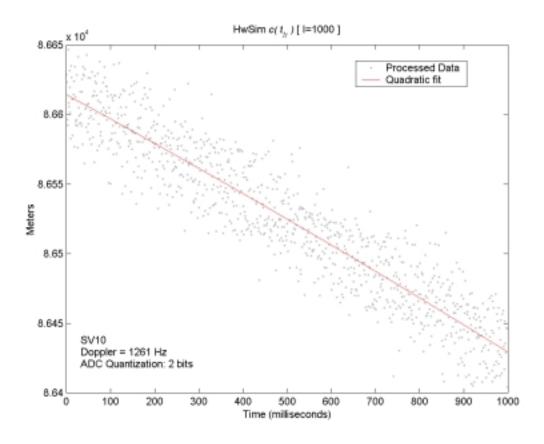

| Figure 8.3  | $c(t_{tr})$ for SV10 With 12-bit ADC                                  | 103 |

| Figure 8.4  | $c(t_{tr})$ for SV10 With 2-bit ADC                                   | 104 |

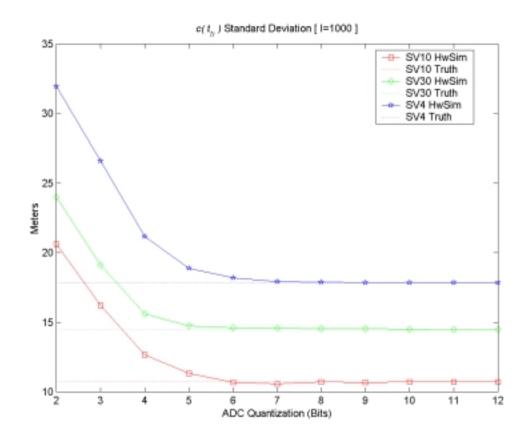

| Figure 8.5  | Effect of ADC Quantization on $c(t_{tr})$ Standard Deviation          | 105 |

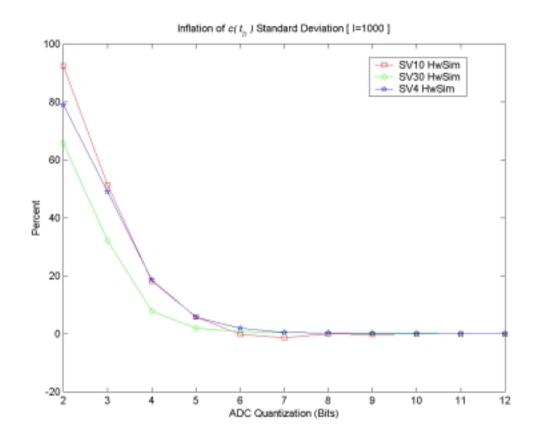

| Figure 8.6  | Inflation of $c(t_{tr})$ Standard Deviation With Respect to the Truth | 106 |

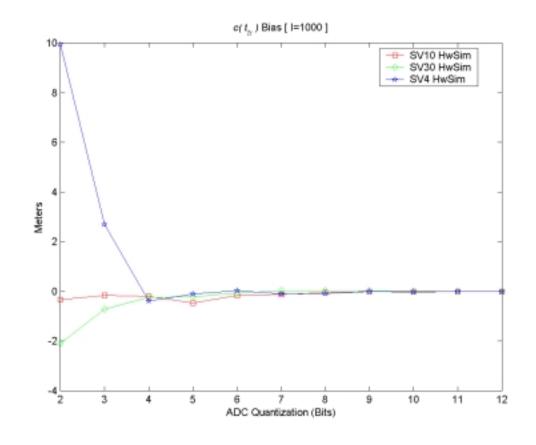

| Figure 8.7  | Ranging Bias Due to ADC Quantization (I=1000)                         | 107 |

| Figure 8.8  | Ranging Bias Due to ADC Quantization (I=100)                          | 108 |

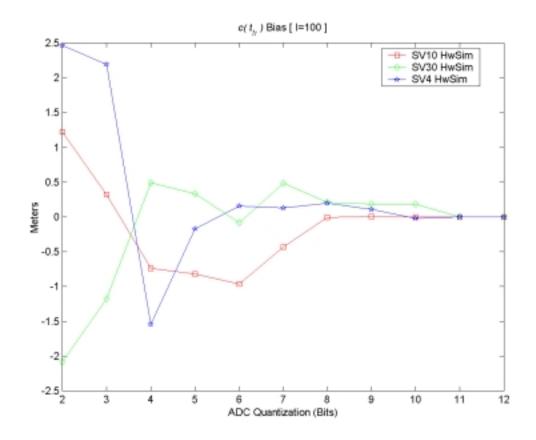

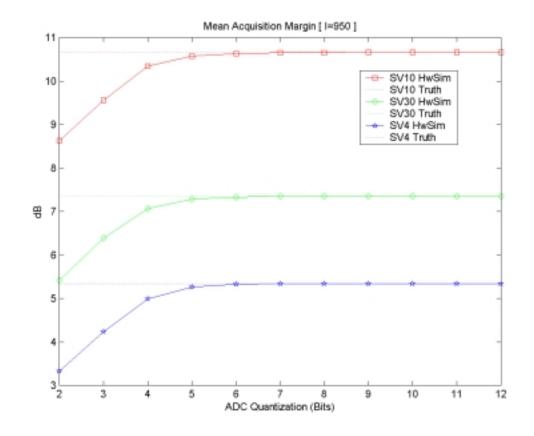

| Figure 8.9  | Effect of ADC Quantization on the Signal Acquisition Margin           | 109 |

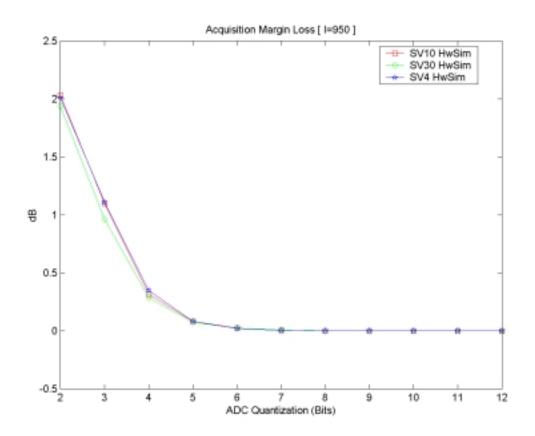

| Figure 8.10 | Loss of Acquisition Margin due to ADC Quantization                    | 110 |

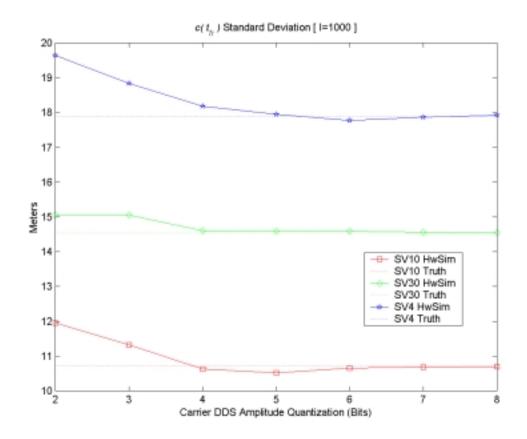

| Figure 8.11 | Effect of Carrier NCO Amplitude Quantization on $c(t_{tr})$ Standard  |     |

| Dev         | iation                                                                | 111 |

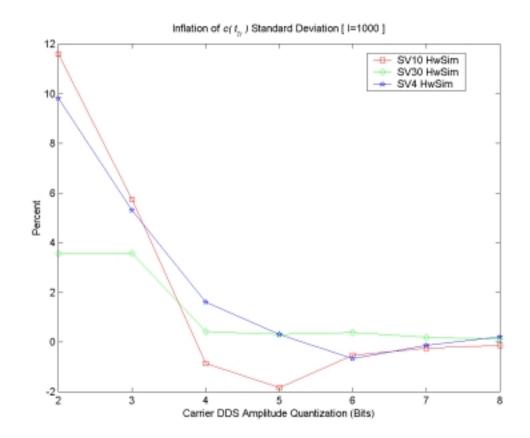

| Figure 8.12 | Inflation of $c(t_{tr})$ Standard Deviation With Respect to the Truth | 112 |

Х

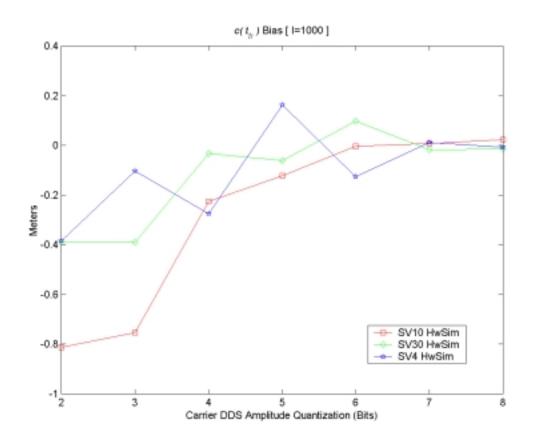

| Figure 8.13 | Ranging Bias Due to Carrier NCO Amplitude Quantization (I=1000)       | 113 |

|-------------|-----------------------------------------------------------------------|-----|

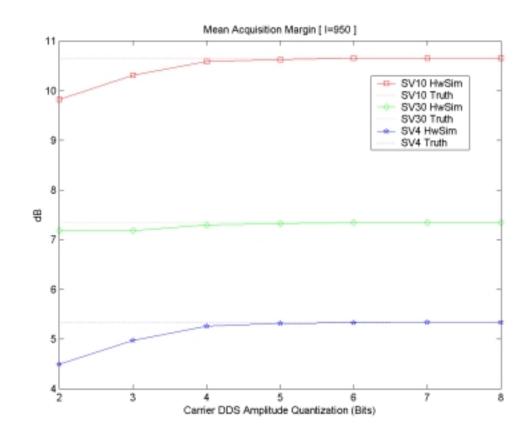

| Figure 8.14 | Effect of Carrier NCO Amplitude Quantization on the Signal Acquisit   | ion |

| Marg        | ;in                                                                   | 114 |

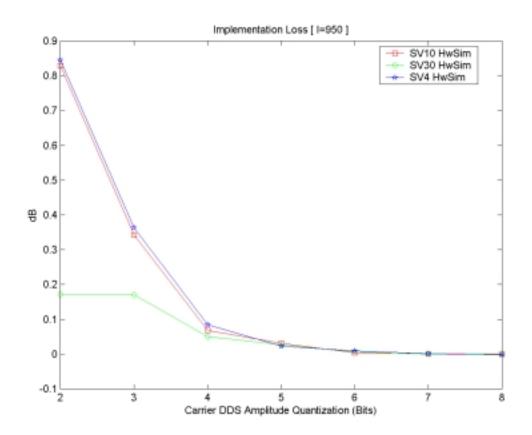

| Figure 8.15 | Implementation Loss due to Carrier NCO Amplitude Quantization         | 115 |

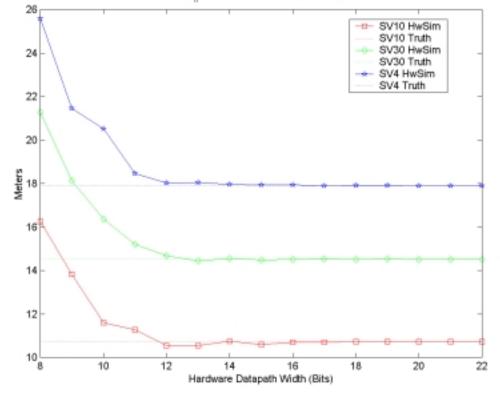

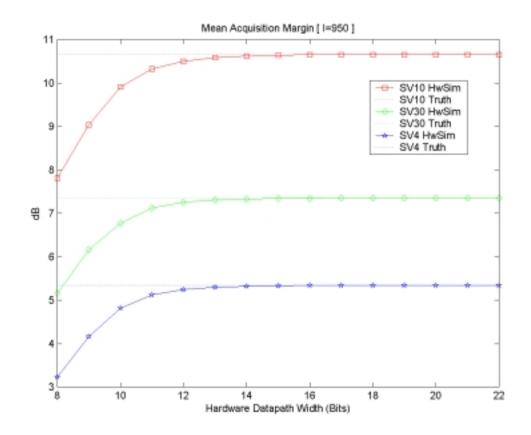

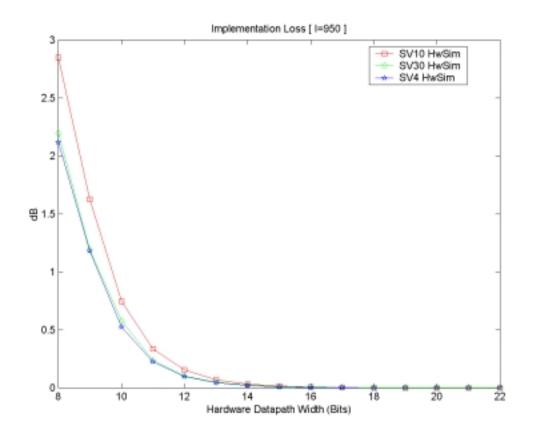

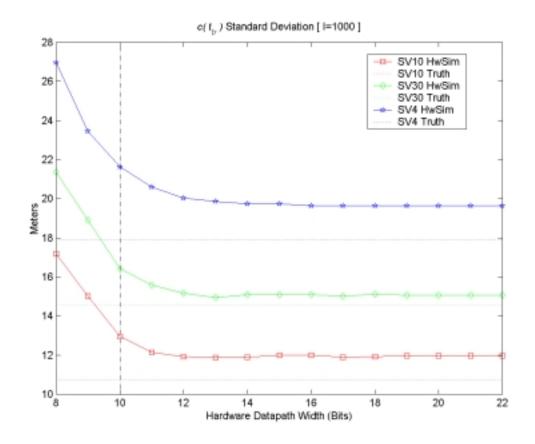

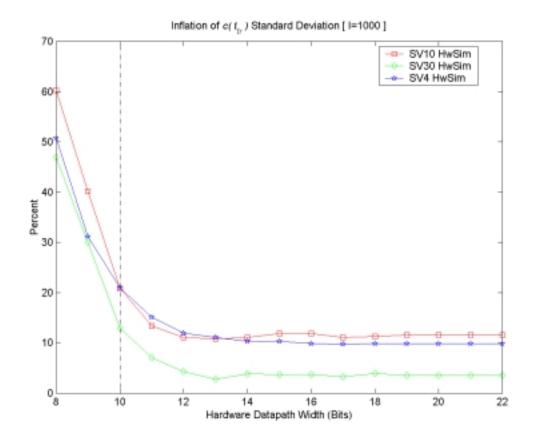

| Figure 8.16 | Effect of Hardware Pipeline Width on $c(t_{tr})$ Standard Deviation   | 116 |

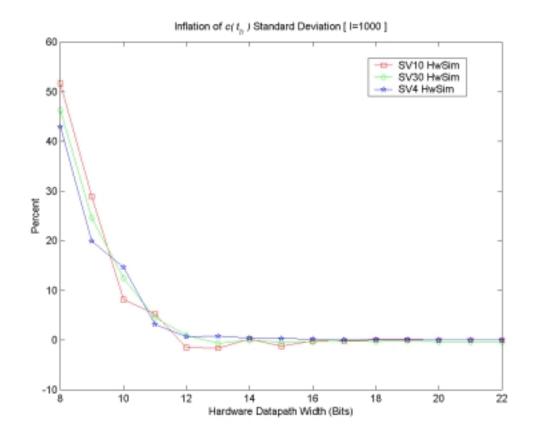

| Figure 8.17 | Inflation of $c(t_{tr})$ Standard Deviation With Respect to the Truth | 117 |

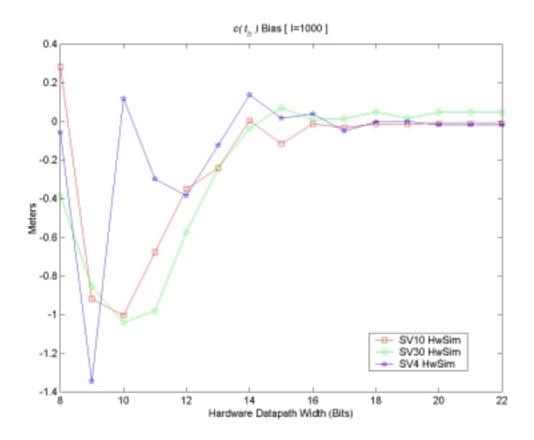

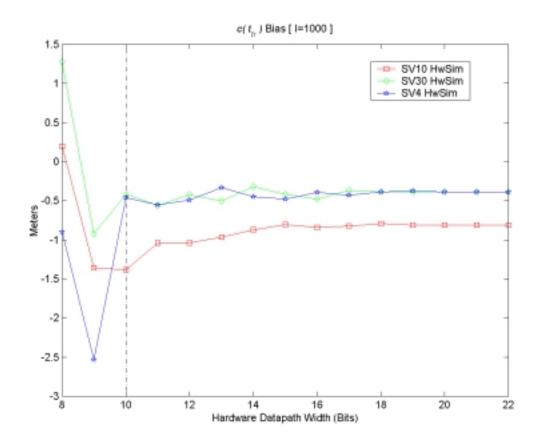

| Figure 8.18 | Ranging Bias Due to Finite Precision Processing                       | 118 |

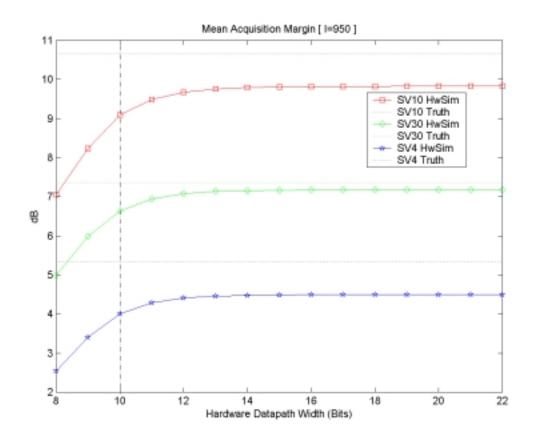

| Figure 8.19 | Effect of Pipeline Width on the Signal Acquisition Margin             | 119 |

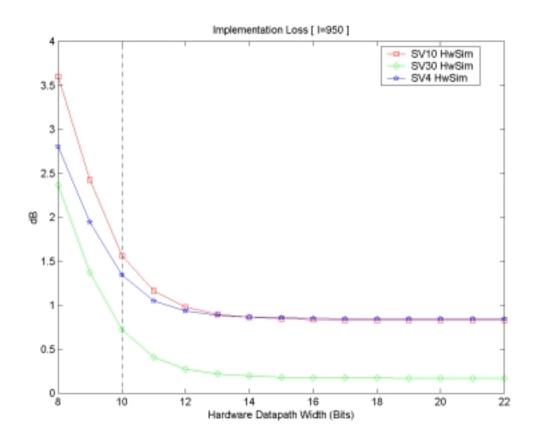

| Figure 8.20 | Implementation Loss due to Finite Precision                           | 120 |

| Figure 8.21 | Range Deviation of Target Hardware Architecture                       | 122 |

| Figure 8.22 | Range Deviation Inflation for Target Hardware Architecture            | 123 |

| Figure 8.23 | Ranging Bias for Target Hardware Architecture                         | 124 |

| Figure 8.24 | Acquisition Margin for Target Hardware Architecture                   | 125 |

| Figure 8.25 | Implementation Loss for Target Hardware Architecture                  | 126 |

xi

## SYMBOLS AND ABBREVIATIONS

| σ                               | Standard Deviation                                                                                            |

|---------------------------------|---------------------------------------------------------------------------------------------------------------|

| 2D                              | two-Dimensional                                                                                               |

| 3D                              | three-Dimensional                                                                                             |

| A&D                             | Accumulate-and-Dump (signal processing operation)                                                             |

| AD                              | Accumulated Doppler                                                                                           |

| ADC                             | Analog-to-Digital Converter                                                                                   |

| AGC                             | Automatic Gain Control                                                                                        |

| AM                              | Amplitude Modulation                                                                                          |

| ASIC                            | Application Specific Integrated Circuit                                                                       |

| ASSP                            | Application Specific Standard Products                                                                        |

| BPF                             | Bandpass Filter                                                                                               |

| bps                             | bits per second                                                                                               |

| BPSK                            | Binary Phase Shift Keying                                                                                     |

| $\mathbf{B}_{\mathbf{W}}$       |                                                                                                               |

| = W                             | Bandwidth                                                                                                     |

| C/A                             | Bandwidth<br>Coarse/Acquisition (GPS ranging PRN code)                                                        |

|                                 |                                                                                                               |

| C/A                             | Coarse/Acquisition (GPS ranging PRN code)                                                                     |

| C/A<br>C/N <sub>0</sub>         | Coarse/Acquisition (GPS ranging PRN code)<br>Carrier to Noise Ratio in dB-Hz                                  |

| C/A<br>C/N <sub>0</sub><br>CDMA | Coarse/Acquisition (GPS ranging PRN code)<br>Carrier to Noise Ratio in dB-Hz<br>Code Division Multiple Access |

| CPLD    | Complex Programmable Logic Device                        |

|---------|----------------------------------------------------------|

| CW      | Continuous Wave                                          |

| DDS     | Direct Digital Synthesis                                 |

| DFF     | D-type Flip-Flop                                         |

| DFT     | Discrete Fourier Transform                               |

| DLL     | Delay Locked Loop                                        |

| DoD     | Department of Defense (United States)                    |

| DPRAM   | Dual-Port Random Access Memory                           |

| DRAM    | Dynamic Random Access Memory                             |

| DSP     | Digital Signal Processing                                |

| FFT     | Fast Fourier Transform                                   |

| FLL     | Frequency Locked Loop                                    |

| FM      | Frequency Modulation                                     |

| FPGA    | Field Programmable Gate Array                            |

| FSM     | Finite State Machine                                     |

| GAEM    | GPS Anomalous Event Monitor                              |

| GLONASS | Global Orbiting Navigation Satellite System              |

| GNSS    | Global Navigation Satellite System                       |

| GPS     | Global Positioning System                                |

| GPS-PPS | Global Positioning System – Precise Positioning Service  |

| GPS-SPS | Global Positioning System – Standard Positioning Service |

| GUI     | Graphical User Interface                                 |

| HOW                                           | Hand-Over Word                                                                                                                                                             |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O                                           | Input/Output                                                                                                                                                               |

| IDFT                                          | Inverse Discrete Fourier Transform                                                                                                                                         |

| IEEE                                          | Institute of Electrical and Electronics Engineers Inc.                                                                                                                     |

| IF                                            | Intermediate Frequency                                                                                                                                                     |

| IFFT                                          | Inverse Fast Fourier Transform                                                                                                                                             |

| IMU                                           | Inertial Measurement Unit                                                                                                                                                  |

| IOB                                           | Input/Output Block                                                                                                                                                         |

| IP                                            | Intellectual Property                                                                                                                                                      |

| kHz                                           | kilohertz                                                                                                                                                                  |

| km                                            | kilometers                                                                                                                                                                 |

|                                               |                                                                                                                                                                            |

| LAAS                                          | Local Area Augmentation System                                                                                                                                             |

| LAAS<br>LGF                                   | Local Area Augmentation System<br>LAAS Ground Facility                                                                                                                     |

|                                               |                                                                                                                                                                            |

| LGF                                           | LAAS Ground Facility                                                                                                                                                       |

| LGF<br>LNA                                    | LAAS Ground Facility<br>Low Noise Amplifier                                                                                                                                |

| LGF<br>LNA<br>LUT                             | LAAS Ground Facility<br>Low Noise Amplifier<br>Lookup Table                                                                                                                |

| LGF<br>LNA<br>LUT<br>MAC                      | LAAS Ground Facility<br>Low Noise Amplifier<br>Lookup Table<br>Multiply-and-Accumulate (signal processing operation)                                                       |

| LGF<br>LNA<br>LUT<br>MAC<br>MDB               | LAAS Ground Facility<br>Low Noise Amplifier<br>Lookup Table<br>Multiply-and-Accumulate (signal processing operation)<br>Minimum Detectable Bias                            |

| LGF<br>LNA<br>LUT<br>MAC<br>MDB<br>MHz        | LAAS Ground Facility<br>Low Noise Amplifier<br>Lookup Table<br>Multiply-and-Accumulate (signal processing operation)<br>Minimum Detectable Bias<br>Megahertz               |

| LGF<br>LNA<br>LUT<br>MAC<br>MDB<br>MHz<br>mHz | LAAS Ground Facility<br>Low Noise Amplifier<br>Lookup Table<br>Multiply-and-Accumulate (signal processing operation)<br>Minimum Detectable Bias<br>Megahertz<br>millihertz |

| NF                                             | Noise Figure                                                                                                                                                                 |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NRE                                            | Non-recoverable Expenditure                                                                                                                                                  |

| OCXO                                           | Oven Compensated Crystal Oscillator                                                                                                                                          |

| PAL                                            | Programmable Array Logic                                                                                                                                                     |

| PC                                             | Personal Computer                                                                                                                                                            |

| PCI                                            | Peripheral Component Interconnect (computer bus standard)                                                                                                                    |

| PDF                                            | Probability Density Function                                                                                                                                                 |

| PE                                             | Processing Element                                                                                                                                                           |

| PLA                                            | Programmable Logic Array                                                                                                                                                     |

| PLD                                            | Programmable Logic Device                                                                                                                                                    |

| PLL                                            | Phase Locked Loop                                                                                                                                                            |

| DD                                             | Decudorance                                                                                                                                                                  |

| PR                                             | Pseudorange                                                                                                                                                                  |

| PR<br>PRN                                      | Pseudo-Random Noise                                                                                                                                                          |

|                                                | -                                                                                                                                                                            |

| PRN                                            | Pseudo-Random Noise                                                                                                                                                          |

| PRN<br>PSOC                                    | Pseudo-Random Noise<br>Programmable System on a Chip                                                                                                                         |

| PRN<br>PSOC<br>RAM                             | Pseudo-Random Noise<br>Programmable System on a Chip<br>Random-Access Memory                                                                                                 |

| PRN<br>PSOC<br>RAM<br>RF                       | Pseudo-Random Noise<br>Programmable System on a Chip<br>Random-Access Memory<br>Radio Frequency                                                                              |

| PRN<br>PSOC<br>RAM<br>RF<br>ROM                | Pseudo-Random Noise<br>Programmable System on a Chip<br>Random-Access Memory<br>Radio Frequency<br>Read-Only Memory                                                          |

| PRN<br>PSOC<br>RAM<br>RF<br>ROM<br>RTL         | Pseudo-Random Noise<br>Programmable System on a Chip<br>Random-Access Memory<br>Radio Frequency<br>Read-Only Memory<br>Register Transfer Level                               |

| PRN<br>PSOC<br>RAM<br>RF<br>ROM<br>RTL<br>RTOS | Pseudo-Random Noise<br>Programmable System on a Chip<br>Random-Access Memory<br>Radio Frequency<br>Read-Only Memory<br>Register Transfer Level<br>Real Time Operating System |

| SRAM   | Static Random Access Memory         |

|--------|-------------------------------------|

| SS     | Spread Spectrum                     |

| SV     | Space Vehicle (satellite)           |

| TOA    | Time of Arrival                     |

| TOW    | Time of Week                        |

| UI     | User Interface                      |

| UTC    | Coordinated Universal Time          |

| VHDL   | VHSIC Hardware Description Language |

| VHSIC  | Very High Speed Integrated Circuit  |

| VLSI   | Very Large Scale Integration        |

| w.r.t. | with respect to                     |

| μs     | microseconds                        |

|        |                                     |

#### **1** INTRODUCTION

Satellite based navigation systems represents the pinnacle of navigation technology for the 21<sup>st</sup> century. Presently, there are two such global navigation satellite systems (GNSSs) in operation: the US developed Navstar Global Positioning System (GPS) and the Russian Global Orbiting Navigation Satellite System (GLONASS). Initially developed by the US department of Defense (DoD), the popularity of GPS has soared over the past decade due to new and ingenious commercial and consumer applications that include surveying, civil aviation, rescue operations, recreational uses, and emergency 911 location services to name but a few. As these applications become more widespread, users demand increased reliability, accuracy and availability that is not always possible with the current capabilities of GPS. This is particularly true when the system is used in urban environments, canyons, and inside buildings where the GPS signal is too weak to detect, or its performance is severely hampered by multipath reflections. These issues have driven the development of new receiver architectures that strive to improve the accuracy and reliability of GPS under these severe operating environments.

Modern GPS receivers use sequential digital signal processing (DSP) techniques. That is, the signal is processed sample by sample. These types of sequential receivers use traditional phase-locked loops (PLLs), frequency-locked loops (FLLs), delay-locked loops (DLLs), and correlators to process the received signal. The front ends of these receivers require high-precision analog components that are expensive and difficult to manufacture. In addition, the component values used deviate from one to another, which means that the receivers need to be individually calibrated. Furthermore, the component values drift over time and reduce reliability and accuracy as the receivers age. Even though modern GPS receivers are built using dedicated hardware due to their application specific nature and the need for tight integration, the sequential processing scheme has limited the performance of these receivers when used in severe operating environments.

A novel receiver architecture known as a software radio has emerged in the last decade. Due to its radically new architecture, the software radio has been referred to as the most significant development in receiver technology since the superheterodyne concept. The goal of the software radio is to sample the received signal as close as possible to the antenna using an analog to digital converter (ADC) and perform all processing in software. By sampling the signal close to the antenna, most of the analog processing components such as mixers, oscillators, filters, and their associated nonlinearities can be removed since the signal is processed entirely in the digital domain using relatively cheap general-purpose microprocessors or DSP processors. Thus, the software radio offers increased reliability and repeatability (i.e. manufacturability) compared to traditional receivers. In practice, sampling at the antenna requires an ADC capable of operating at the Nyquist rate of the incoming signal, while having exceptionally low sampling noise and good stability. Such components are either not available today, or are too expensive for mass production. Processing the huge amounts of data generated through such a scheme presents another more severe problem. Due to

these technology limitations, a compromise is reached by having at least one stage of analog downconversion before sampling.

The software radio is the ultimate receiver architecture since it offers infinite flexibility for implementing the processing algorithms. In other words, a software radio is a universal receiver that is programmable for virtually any application imaginable (within spectrum limitations). This receiver architecture is ideal for today's fast paced world, where product life cycles are measured in months and telecommunication standards and user requirements keep changing regularly.

The software radio has also unleashed a new breed of DSP techniques available for processing GPS signals. Instead of the DSP equivalents of the various sequential processing techniques used in the past, blocks of incoming data may be processed at once, similar to the techniques used for image processing. When applied to GPS, these blockprocessing techniques have been successful in pushing the envelope of its capability. For example, a GPS signal with a carrier-to-noise ratio lower than 44 dB-Hz is too weak and difficult for a standard receiver to detect. However, block-processing techniques have been used to successfully acquire signals as low as 20 dB-Hz [UijtdeHaag99]. This capability enables GPS positioning to work inside buildings and terrain with thick vegetation where GPS would otherwise be unusable.

The drawback of block processing techniques is their huge computational requirement. Currently developed block processing techniques require the computation of large discrete Fourier transforms (DFTs) using the fast Fourier transform (FFT) algorithm, and takes on the order of several seconds to process a single millisecond of

data in a fast (~500 MHz) computer. This means even dedicated DSP processors would fail to handle the task in real time, because they do not offer such a leap in performance compared to general-purpose microprocessors. A custom hardware solution, such as an application specific integrated circuit (ASIC) could handle the computational requirement, but would defeat the philosophy of the software radio since it would then lack the desired flexibility. The ideal implementation platform for the GPS software radio is one that possesses the processing power of ASICs with the programming flexibility of general-purpose microprocessors.

Field Programmable Gate Arrays (FPGAs) are the latest addition to the family of programmable logic devices (PLDs) that includes programmable logic arrays (PLAs), programmable array logic (PALs) and complex programmable logic devices (CPLDs). The Xilinx<sup>™</sup> Corporation invented the FPGA in 1987 [Roelandts99]. FPGAs are manufactured using Static Random Access Memory (SRAM) technologies, and can therefore be considered as specialized memory circuits. The functionality of the FPGA is determined by programming SRAM cells that work as look up tables (LUTs) to determine the logic function, or drive CMOS pass transistors that act as switches to make connections between the various logic functions. Present day FPGAs have relatively large equivalent gate counts (between 100,000 and 10 million gates), operate at high system clock rates (~300 MHz for the Virtex-E<sup>™</sup> device), and are capable of supporting large system-on-chip (SOC) applications. The rapid evolution of the FPGA to an above-million-gate device has made it a viable contender in applications that were once dominated by the ASIC. By far the most advantageous feature of the FPGA is that it can

be programmed quickly and easily with any design an infinite number of times, whereas ASICs take several months to develop and manufacture. FPGAs are widely used today as prototyping tools to test and validate large designs before they are manufactured in ASIC technologies. They have also found a niche in the data communications industry, where FPGAs are used for complex data switching and routing applications. Another new area of research that involves FPGAs is called dynamic reconfiguration. Here, a section of the processor can be made to change its architecture on the fly based on intelligence about the application that is currently being processed in real time. The FPGA is the only technology available today that simultaneously fulfils the processing power and flexibility requirements needed for a real-time block-processing GPS software radio.

This thesis studies the feasibility of implementing a real-time block-processing GPS receiver using FPGAs. This is the first time an effort has been made to migrate the novel algorithms developed in software to custom designed digital hardware to ultimately realize such a receiver. The actual hardware implementation of the block processing algorithms is an immense task that would require years to develop a working prototype, and is beyond the scope of this work. The goal of this work was as follows: 1) Determine how the block processing algorithms can be implemented in FPGA hardware. 2) Develop a high-level hardware architecture that is optimized as much as possible for implementation in an FPGA, which can also be easily broken down to lower levels of abstraction within a hardware design flow. 3) Determine what type of throughput could be obtained from this architecture based on a high level machine-cycle based evaluation. 4) Determine the optimum datapath precision needed for acceptable performance based

on a behavioral simulation of the developed architecture using real GPS data. 5) Determine if it is feasible to implement this architecture with currently existing FPGA technology. Since the architecture developed in this work is modeled at a high level of abstraction and not largely implementation platform specific, it is possible to take the results presented in this thesis to target a technology other than FPGAs (such as ASICs). However, the overall architecture described was meant for a FPGA implementation because of its obvious advantages.

This thesis is organized as follows: Chapters 2 covers the necessary GPS background. Chapter 3 describes the sequential GPS receiver architecture that is used in all modern receivers. Chapter 4 describes the GPS block-processing algorithms, examines some of their potential applications, and presents a concept model for a real-time block processing GPS receiver. Chapter 5 introduces FPGAs and presents their internal architecture. Chapter 6 covers FFT theory and describes the development of the 5000-point mixed-radix FFT/IFFT algorithm that is the basis for the GPS block processing techniques. Chapter 7 covers the hardware architectures of the individual block-processing subsystems developed in this work and evaluates the feasibility of the real time requirement based on a machine-cycle based analysis. Chapters 8 presents simulation results based on real GPS data that was used to test and validate the hardware architecture and determine its optimal parameters. Finally, Chapter 9 gives a summary of the work done for this thesis and discusses future work for realizing the long-term goals of this project.

#### 2 THE GLOBAL POSITIONING SYSTEM

Global navigation satellite systems (GNSSs) are the latest and most advanced class of navigation systems based on the simple time-of-arrival (TOA) ranging concept. GNSSs use satellites in space to implement TOA raging using a principal known as trilateration. Presently, two such systems exist: the United States' Global Positioning System (GPS) and the Russian Global Orbiting Navigation Satellite System (GLONASS). Both systems were developed in parallel during the latter years of the Cold War. The scope of this thesis is limited to GPS.

GPS was developed by the DoD primarily for military use. However, since an initial positioning capability needed to be incorporated to acquire the precise positioning component of GPS, that initial positioning service was made available to civilian users. This lower-precision component is known as the standard positioning service (GPS-SPS), whereas the military component is known as the precise positioning service (GPS-PPS). GPS-SPS has found a tremendous wealth of applications ranging from recreational uses such as hiking to commercial and civil aviation, and today is the basis for a rapidly growing industry that is expected to double in the next three years to \$16 Billion annually [AP00]. This is even truer after May 2, 2000 when the US government turned off Selective Availability (SA), which intentionally limited positioning accuracy to 150 Meters ( $2\sigma$ ) for civilian users [WH00].

The following sections describe how the system is used to obtain a position solution; along with the GPS link budget, its signal structure and dynamics, as applicable to this thesis.

### 2.1 Positioning With GPS

As described above, GPS is based on TOA ranging. TOA ranging involves measuring the time taken for a signal transmitted by an emitter (foghorn, radiobeacon, or satellite) in a known location to reach an observer (receiver) at an unknown location (i.e. propagation time).

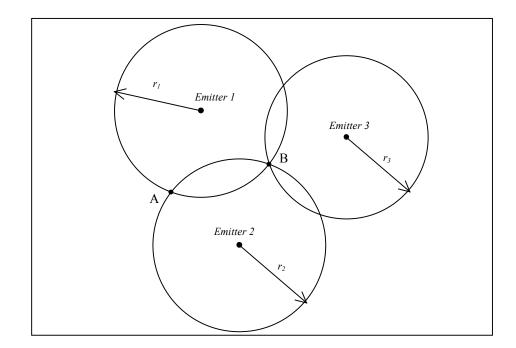

Figure 2.1 Graphical Illustration of Tri-Lateration

For the two dimensional (2D) case depicted in Figure 2.1, for one emitter, the position of the observer can be placed anywhere on a circle with radius r given by the measured range from the emitter. The difference between the time of reception,  $t_{re}$ , and

the time of transmission,  $t_{tr}$ , times the propagation speed of the signal gives the range from the emitter to the observer. If the range from two emitters with known locations can be measured, the position of the observer is one of two solutions, A or B. Three range measurements results in a unique solution, B, for the position of the observer. Hence, this type of positioning is referred to as tri-lateration. For the three-dimensional (3D) case, the circles in Figure 2.1 are replaced with spheres. For satellite navigation, three range measurements alone would give rise to an ambiguity for the observer's position. This is resolved without the use of a fourth measurement by realizing that one solution is close to the surface of the earth whereas the other is not.

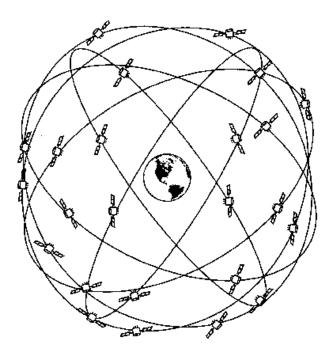

The GPS constellation (GPS space segment) consists of 24 satellites, called space vehicles (SVs), in six orbital planes, as illustrated in Figure 2.2.

Figure 2.2 GPS Satellite Constellation (Not to Scale)

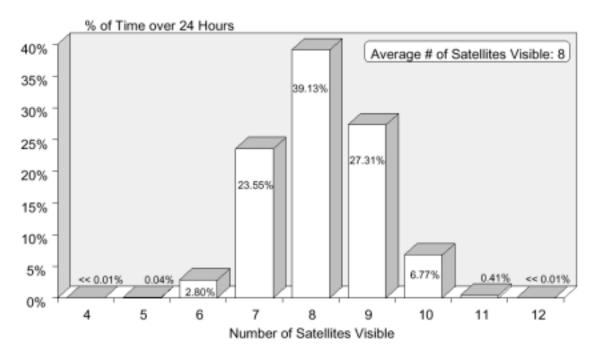

The orbits are configured in such a manner as to have at least four satellites visible to a user near the surface of the earth at any given location and time. Practically, it is common to receive between seven to nine SVs. Figure 2.3 shows the GPS SV global visibility profile for a 24-hour period [USDOT95].

Figure 2.3 GPS Satellite Global Visibility Profile

For the  $i^{th}$  satellite, the true SV-to-user range,  $R_i$  is given by:

$$R_i = c \left( t_{re} - t_{tr_i} + \Delta t_{SV_i} + \Delta t_{Rcvr} \right)$$

(2.1)

Where:

$t_{tr_i}$ :time of transmission of SV\_i $t_{re}$ :time of reception relative to the receiver clock $\Delta t_{SV_i}$ :clock offset of SV\_i w.r.t. transmitted timing signals $\Delta t_{Rcvr}$ :offset in the receiver's internal clock w.r.t. received timing signalsc:GPS propagation constant (2.99792458 × 10<sup>8</sup> m/s)

A pseudorandom noise (PRN) code embedded within the GPS broadcast is used to perform timing measurements. When the code-tracking loop of the GPS receiver is time aligned to the incoming PRN code, the delay between the receiver's replica code epoch and the incoming code epoch (hence known as the *code phase*) gives the time of transmission,  $t_{tr}$ , of the signal. Since the range measurement for  $SV_i$  obtained from  $t_{tr}$  still contains the clock biases of the receiver and satellite, it is known as the *pseudorange* (PR) to  $SV_i$  and is given by:

$$PR_{i} = c(t_{re}(n) - t_{tr_{i}}(n))$$

(2.2)

Where:

| $t_{re}(n)$ :   | receiver time corresponding to epoch $n$ of the GPS receiver's clock |

|-----------------|----------------------------------------------------------------------|

| $t_{tr_i}(n)$ : | transmit time based on the $SV_i$ clock                              |

Hence, when the receiver picks any replica code epoch to make range measurements for all SVs,  $t_{n_1}(n)$  is the natural measurement (obtained from the code tracking loop) that is used to calculate the pseudorange. The receiver and satellite clock biases are subsequently corrected when the receiver solves for the navigation position solution. The data stream embedded within the GPS broadcast contains the SV clock offset,  $\Delta t_{SV}$ . Once the receiver obtains the pseudoranges of at least four SVs, it can solve for position, (x, y, z), and the clock bias, *B*, from:

$$PR_{i} = \sqrt{(x - x_{i})^{2} + (y - y_{i})^{2} + (z - z_{i})^{2}} + cB$$

(2.3)

Where:

$(x_i, y_i, z_i)$ : position of SV<sub>i</sub> (from SV<sub>i</sub> ephemeris data)

When the receiver clock bias is corrected, the local reference clock is accurately synchronized to GPS time. Thus, GPS provides an accurate timing capability in addition to positioning. The absolute time (GPS time) is obtained from the time-of-week (TOW)

contained in the data broadcast. The TOW count has a resolution of 1.5 seconds and is reset every Sunday at 00.00 hrs, GPS time. The offset between GPS time and UTC is also contained within the data broadcast.

#### 2.2 GPS Link Budget

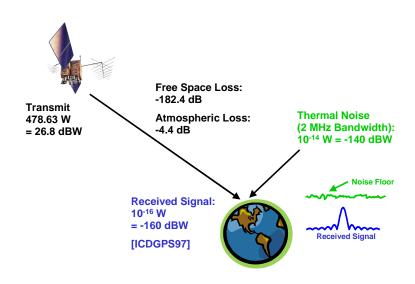

Figure 2.4 shows the link budget for GPS. A block IIR GPS SV transmits an equivalent power of 480 Watts towards the earth. Most of this power is lost according to the inverse-square law when the signal travels approximately 20,000 km to the earth's surface. By the time the GPS signal is received at the antenna, it is about 20 dB below the receiver's thermal noise floor.

Figure 2.4 GPS Link Budget

Hence, traditional signal demodulation schemes such as those used for FM or AM cannot be used for spread-spectrum (SS) signals such as GPS because the signal is buried within the noise. Instead, the signal must be observed (integrated) over time so that the noise is averaged out, thereby raising the signal above the noise floor. To detect a GPS signal, integration is initially performed using *estimates* for the signal's code phase and carrier frequency using local synthesizers. This signal detection process is known as *acquisition*.

The received signal strength is guaranteed to be a minimum of -160 dBW[ICDGPS97]. The noise floor is approximated by  $N = kTB_W$ , where k is Boltzmann's constant ( $1.3807 \times 10^{-23} J/K$ ), T is the Kelvin temperature, and  $B_W$  is the input bandwidth of the receiver in Hertz. Because the signal-to-noise ratio, S/N, is dependent on the input bandwidth, it is not a good measure of the true received signal strength. Hence, the carrier-to-noise ratio, given by  $C/N_0 = S/kT$  [Braash91] is used instead.  $C/N_0$  is expressed in dB-Hz. Given the minimum GPS received signal strength of -160 dBW, and a temperature of 300K, the minimum received C/N<sub>0</sub> is 44 dB-Hz.

#### 2.3 GPS Signal Structure

The scope of this thesis is limited to the GPS-SPS broadcast. The signal structure for the GPS-SPS signal, S(t), can be modeled as:

$$S(t) = A(t)G(t)D(t)\sin(2\pi(f_0 + \Delta f_{SV}) + \phi_0)$$

(2.4)

Where:

| A(t)            | : | time dependant amplitude of the transmitted signal |

|-----------------|---|----------------------------------------------------|

| G(t)            | : | C/A code for the satellite (1.023 Mbps)            |

| D(t)            | : | navigation data stream (50 bps)                    |

| $f_0$           | : | carrier frequency of broadcast (1575.42 MHz)       |

| $\Delta f_{SV}$ | : | satellite frequency offset                         |

| $\phi_0$        | : | carrier phase offset                               |

Each SV transmits at the same  $L_1$  carrier frequency of 1575.42 MHz. Spreadspectrum code division multiple access (CDMA) technology is used to demodulate the signal of each SV received at the antenna. The PRN code used for GPS-SPS is called the coarse acquisition (C/A) code. The 1023-chip long C/A code has a chipping rate of 1.023 Mbps, and hence a period,  $T_c$ , of 1 ms. The C/A code belongs to the family of Gold codes, possessing good multiple access properties for its period [Spilker78], an important factor for CDMA systems. However, unlike communications systems that use CDMA technology mainly for its inherent security and multiple-access capabilities, GPS uses its PRN code for ranging as well [Equation 2.2]. C/A code generation details are described in [ICDGPS97].

Modulo-2 added onto the C/A code is the 50 bps data stream, D(t). The databits are generated in synchronous to the C/A code. The data message structure consists of a 1,500-bit long frame that is made up of five subframes, 1 through 5. Each subframe is 300 bits long, and consists of ten 30-bit words. The full data message consists of 25 full frames (12.5 minutes) since subframes 4 and 5 are subcommutated 25 times. However, decoding a full frame (30 seconds) is sufficient for a position calculation since it contains the necessary clock and ephemeris data in subframes 1 through 3. The second word of each subframe is the hand-over-word (HOW), which gives the precise GPS time-of-week (TOW) that will be valid at the starting edge of the next subframe. Thus, TOW updates are available every 6 seconds.

The bitstream containing the SV PRN code and the embedded data message is Binary Phase Shift Keying (BPSK) modulated onto the  $L_1$  carrier.

#### 2.4 SV-to-User Dynamics

Even though a GPS SV transmits at a constant  $L_1$  carrier frequency,  $f_0$ , of 1575.42 MHz, SV-to-user dynamics causes the carrier frequency to vary depending on the relative line-of-sight velocity,  $v_r$ , causing a Doppler frequency shift,  $\Delta f_D$ , given by:

$$\Delta f_D = \pm \left(\frac{v_r}{c - v_r}\right) f_0 \tag{2.5}$$

For a stationary user,  $v_r$  is typically less than 1,500 m/s, which corresponds to a Doppler frequency offset of ±8 kHz.

The goal of this chapter was to explain the basic principals of GPS operation. In practice, many parameters such as geometry, atmospheric and ionospheric group delays, and multipath reflections affect the performance of GPS. The analysis of these effects and the errors they introduce to the final position calculation are beyond the scope of this work. The next chapter describes the architecture of a GPS receiver.

#### **3 GPS RECEIVER ARCHITECTURE**

In order to apply new signal processing techniques to GPS receivers, it is important to understand the architecture and functionality of traditional GPS receivers. Almost all modern GPS receivers sample the downconverted RF signal and perform all signal processing algorithms in the digital domain [Parkinson96]. The DSP techniques process the incoming data one sample at a time; that is, the processing technique is sequential. In order to differentiate this type of receiver from block processing receivers described in Chapter 4, the term *sequential receiver* is used in this thesis. This chapter describes the architecture and operation of a generic GPS-SPS sequential receiver.

#### 3.1 Overview of Generic GPS-SPS Receiver

Figure 3.1 shows the block diagram of a generic GPS receiver. This diagram represents the minimum system required to receive the GPS-SPS broadcast of Equation 2.4 and calculate a navigation solution.

Figure 3.1 Block Diagram of a Generic GPS Receiver

The receiver can be sectioned into three main parts: 1) the RF front end, digitizing and automatic gain control (AGC), 2) the individual receiver channels and controlling processor, hereafter referred to as the *receiver processor*, and 3) the navigation/user interface processor and peripheral components such as power supply, user interface (UI), etc.

The RF front end amplifies the weak signals received at the antenna while rejecting unwanted out-of-band noise and downconverts the  $L_1$  signal to the intermediate frequency (IF). All signal Doppler offsets and code phase information is preserved after downconversion (only the carrier frequency is lowered). An analog-to-digital converter

(ADC) samples the downconverted signal. The signal may also be digitally downconverted by the sampling process by using bandpass sampling techniques [Chapter 4]. Assuming the signal parameters do not change over the integration time of the receiver channel, the resulting digital IF signal,  $r_k$ , where k is the sample point (k = 1,2,3...), can be represented as follows:

$$r_k = AG_{k,\tau}D_{\tau}\sin\left(2\pi(f_{IF} + \Delta f)T_S(k) + \phi\right) + n_k \tag{3.1}$$

Where:

| τ            | : | time delay due to signal transmission |

|--------------|---|---------------------------------------|

| A            | : | signal amplitude                      |

| $G_{k,\tau}$ | : | sampled, time-delayed C/A code        |

| $D_{	au}$    | : | time delayed navigation data stream   |

| $f_{IF}$     | : | digital IF frequency                  |

| Δf           | : | frequency offset                      |

| $T_S$        | : | sampling period (1/fs)                |

| $\phi$       | : | phase offset                          |

| $n_k$        | : | sampled noise term                    |

The received noise, n, is commonly modeled as additive white Gaussian noise [Parkinson96]. The frequency offset of the received signal,  $\Delta f$ , is the sum of four components:

$$\Delta f = \Delta f_{SV} + \Delta f_D + \Delta f_{LO} + \Delta f_S \tag{3.2}$$

Where:

| $\Delta f_{SV}$ | : | satellite frequency offset [Equation 2.4]    |

|-----------------|---|----------------------------------------------|

| $\Delta f_D$    | : | Doppler frequency offset [Equation 2.5]      |

| $\Delta f_{LO}$ | : | frequency offset due to the local oscillator |

| $\Delta f_S$    | : | frequency offset due to sample clock error   |

The receiver has no means of distinguishing between  $\Delta f_D$ ,  $\Delta f_{LO}$ , and  $\Delta f_S$ . Hence, it is important to minimize local oscillator and sample clock errors in the RF front end and sampling process respectively, so that they do not degrade the Doppler measurement. For this reason, the stable clock reference shown in Figure 3.1 is a critical component of any GPS receiver and influences the accuracy of the overall navigation solution.

The AGC circuit sets the amplitude of the sampled signal such that the dynamic range of the ADC is optimally utilized. Parallel processing is performed on the digital IF by the individual receiver channels. Each channel performs acquisition and tracking of individual satellites under the control of the receiver processor.

The natural measurements of a GPS receiver are the replica code phase, and the replica carrier Doppler frequency (if the receiver is in frequency lock with the incoming carrier signal) or the replica carrier Doppler phase (if the receiver is in phase lock with the incoming carrier signal). The receiver processor takes these measurements and calculates pseudoranges and delta-pseudoranges. In addition, if the receiver is in phase lock, it calculates the accumulated Doppler (AD) phase, which is used for millimeter-level positioning in surveying applications [Kaplan96]. The pseudorange and delta-pseudorange measurements are considered the GPS observables. The navigation processor uses the GPS observables, along with the navigation data to find a position solution. The navigation processor is also the intelligence component of the receiver that contains various algorithms to handle the complex decision making processes involved in a GPS receiver.

The most computation intensive process in the receiver (excluding the graphics processing for the UI) is the correlation operation that is performed within each receiver channel. For the correlation, the channel must perform multiply-and-accumulate (MAC) operations in real time at the digital IF data rate,  $f_s$ . In most modern receivers however,

this is no longer considered an issue owing to the availability of ASICs that integrate all the math-intensive operations of the receiver channel. Such chips are available at relatively low cost due to volume production.

The following sections will describe tracking and acquisition of the GPS signal respectively.

#### **3.2 Tracking Loops**

As described in Section 2.2, the GPS signal must be integrated over time to raise it above the noise floor. The initial process of locating the GPS signal in terms of its code phase and carrier frequency is known as *acquisition*. Following acquisition, the code phase and carrier frequency estimates are fed into code and carrier tracking loops respectively. Provided the initial estimates are within their lock-in range, the tracking loops will keep the signal in lock, i.e. the loops will follow subsequent changes in code and carrier frequency (or phase). This is known as *tracking*. During tracking, if the code phase or carrier frequency suddenly changes value (i.e. steps), or they drift beyond the range of the tracking loops, the tracking operation will fail. This condition is known as *loss-of-lock*. When the receiver loses lock, it must reacquire the signal.

Figure 3.2 shows the simplified architecture within a single receiver channel. As shown in the figure, the carrier and code tracking loops operate together to lock code phase and carrier frequency simultaneously. The following subsections will describe the operation of the carrier and code tracking loops respectively.

Figure 3.2 Block Diagram of a GPS Receiver Channel

### 3.2.1 Carrier Tracking

The digital IF is first mixed in quadrature with the replica carrier to convert it to baseband. A baseband signal is one that has been stripped of its carrier except for the residual,  $\Delta f$ . The purpose of the carrier tracking loop is to keep the carrier synthesizer (local oscillator) locked to the incoming carrier frequency ( $f_{IF} + \Delta f$ ) so that the mixer output has no carrier component. Hence, this operation is known as carrier wipeoff. The signal is then correlated with the aligned replica C/A code (code wipeoff) and integrated using accumulate-and-dump (A&D) circuits. Since the A&D circuits have a low-pass characteristic, the double frequency term generated in the quadrature mixer is filtered out, leaving only the correlation value. The carrier loop discriminator outputs the frequency (or phase) offset magnitude and direction determined from the in-phase and quadrature components of the signal. After low-pass filtering, this error is fed back to the carrier synthesizer. GPS receivers use two types of carrier tracking loops: phase locked loops (PLL) and frequency locked loops (FLL). Both have their own advantages and disadvantages in terms of carrier tracking performance. The loop bandwidth is determined by the integration time (known as the pre-detection integration time, or dwell time,  $T_{DW}$ ) and the characteristics of the filter. The filtered error value used to control the carrier synthesizer gives the replica carrier frequency offset,  $\Delta f$ . The carrier frequency offset is the basis for the delta-pseudorange measurement.

### **3.2.2 Code Tracking**

The operation of the code-tracking loop is similar to the carrier-tracking loop in that the local replica code is compared to that of the incoming signal to produce a code offset that is filtered and used to control the code synthesizer. However, in the case of the code loop the replica code must be accurate to within one chip of the incoming code, since an offset greater than one chip produces zero correlation. By using the early and late correlation envelopes (and optionally the prompt correlation envelope, depending on the discriminator function), the code phase discriminator determines the magnitude and direction of the code phase error relative to that of the incoming signal. The early and late code streams are offset ½ chip relative to the prompt code stream. The noisy code phase error output of the discriminator is smoothed by the code loop filter.

Using the filtered code phase offset, the code synthesizer must advance or retard the replica code to align it with the incoming code. Hence, this type of tracking loop is called a delay locked loop (DLL). The code phase offset is the basis for the pseudorange measurement [Equation 2.2].

The difference in the pseudorange over a measurement time interval gives the SV's relative line-of-sight velocity. However obtaining this information from the code loop gives rise to noisy measurements. Instead, a 1000 times or 100 times less noisy delta-pseudorange measurement can be obtained from the carrier PLL or FLL respectively. Hence, the filtered replica carrier frequency (or phase) offset is used to smooth the error in the code loop. This is known as carrier smoothing (or carrier aiding, shown in Figure 3.2). The carrier smoothing technique is mathematically equivalent to including the second order term of an expansion series. In addition, for high accuracy and reliability, the tracking loops can be externally aided by a positioning system who's principal of operation is not related to GPS, such as an Inertial Measurement Unit (IMU).

The design of tracking loops is a complex subject and only a brief outline was given here. Detailed descriptions of the tracking loops used in GPS can be found in [Parkinson96].

### 3.3 Signal Acquisition

Figure 3.3 shows a block diagram of the acquisition architecture within the receiver channel. Much of the same hardware is used for acquisition, as apparent when comparing Figure 3.2 with Figure 3.3.

Figure 3.3 GPS Acquisition Configuration within a Receiver Channel

During acquisition, the channel operates in an open loop configuration where the acquisition algorithm tests successive code phase and carrier frequency combinations for a correlation peak, given by  $I^2 + Q^2$  (i.e. the correlation energy). A second integration stage is used to sum correlations over multiple code periods to detect signals with low C/N<sub>0</sub>. The preset threshold for determining the presence of a signal is calculated based on the application's required probabilities of false acquisition,  $P_{FA}$ , and missed detection,  $P_{MD}$ .

The receiver detects a correlation peak by comparing the correlation energy amplitude against a preset threshold,  $T_D$ . If this threshold is set too high, the receiver will

not detect weak signals, thus increasing the probability of a missed detection. If the threshold is too low, an increase in the probability of false acquisitions due to noise will result. Figure 3.4 uses Gaussian probability density functions (PDFs) to illustrate the relationship between  $P_{FA}$ ,  $P_{MD}$  and the minimum detectable bias, *MDB*. Based on the statistical distribution of the signal and noise parameters, and the required  $P_{FA}$ , the detection threshold can be calculated [Feng99].

Figure 3.4 Illustration of  $P_{MD}$ ,  $P_{FA}$ , and MDB using Gaussian PDFs

Acquisition is a three-dimensional search process, where the search dimensions are: 1) The CDMA PRN code of the SV, 2) The incoming signal's carrier frequency, and 3) The incoming signal's PRN code phase. If the receiver has knowledge of the approximate satellite orbits (almanac data), it can start searching for a probable SV based on the current time and the receiver's last known position. If this is not possible, the receiver must start by searching for any one of the 24 possible PRN codes. This is known as a "cold start". Assuming the receiver is searching for a given SV, the acquisition search space is shown in Figure 3.5.

Figure 3.5 GPS Acquisition Search Space

Section 2.4 showed that the Doppler frequency offset is approximately  $\pm 8$  kHz for a stationary observer. Indeed, for most typical applications  $\Delta f_D$  is less than  $\pm 10$  kHz. If the receiver cannot estimate the Doppler, it must perform the entire search between  $L_1$ -10 kHz and  $L_1$ +10 kHz in steps of the Doppler frequency search resolution. Since the replica code needs to align within one chip to obtain a correlation peak, the maximum code phase resolution is <sup>1</sup>/<sub>2</sub> chip. Because the GPS C/A code is 1023 chips long, there exists a minimum of 2046 search bins in the code phase dimension. If the receiver cannot estimate the pseudorange to the SV due to lack of a-priory information, it must check all 2046 bins.

Since the receiver must integrate to at least an entire C/A code period, the minimum dwell time for a correlation is 1 ms, which is adequate for high  $C/N_0$  signals. However, during non-coherent acquisition (when the receiver code epoch is not synchronized to the SV code epoch), if a databit transition occurs within the dwell time, the correlation sign changes, effectively nulling the correlation result. Hence, a longer dwell time must be used during a cold start acquisition. Weak signals need longer dwell times per cell. This is accomplished by the second A&D operation in Figure 3.4.

The Doppler search resolution must be fine enough to land within the main lobe of the  $Sinc^2$  correlation function (whose width is a function of the dwell time). The Doppler bin resolution can be estimated by  $2/3T_{DW}$ , where  $T_{DW}$  is the dwell time per cell. The minimum dwell time of 1 ms gives a Doppler bin resolution of 667-Hz. To acquire weak signals,  $T_{DW}$  can be as much as 20 ms, needing a Doppler bin resolution of 33-Hz [Kaplan96]. For example, during a cold start, if a typical sequential receiver searches the  $L_1$ -10 kHz to  $L_1$ +10 kHz carrier frequency interval in 1 kHz steps, it needs to search through 21 combinations in the carrier frequency dimension. Since the minimum codephase dimension is 2046  $\frac{1}{2}$ -chip intervals, the total cold start acquisition search space for the receiver is:

$$2(1023) \times \left( 2 \left( \frac{10 KHz}{1 KHz} \right) + 1 \right) = (2046)(21) \approx 40,000 \ acquisition \ cells$$

Since the minimum dwell time is 1 ms (assuming no databit transitions), this operation will take about 40 seconds to complete in the worst case. Because every acquisition is not done in cold start mode, and the acquisition is performed in parallel in each of the receiver channels for candidate SVs, and because of the efficiency of the acquisition algorithms themselves, the mean time to acquire a signal is considerably smaller than this worst case estimate in a practical receiver. However, due to the inherent processing scheme in a sequential receiver, the mean time to acquisition is still in the order of a few seconds.

When GPS receivers are used in environments where the signal suffers severe attenuation (such as in dense foliage, inside buildings, or urban environments), or in highdynamic environments (such as in fast aircraft or rockets), sequential receivers spend a significant amount of time in the acquisition phase, because under these conditions the receiver will often lose lock. Hence, the long acquisition time of a sequential receiver and its inability to cope with sudden signal steps in its tracking loops is a serious drawback for such applications. In these situations, a block processing architecture becomes a viable alternative to the sequential processing used in current GPS receivers. The next chapter describes the architecture of a block processing GPS receiver.

#### **4 BLOCK PROCESSING GPS RECEIVER**

In the GPS receiver of Chapter 3, the processing was performed sequentially. This method of processing, known as *stream processing* [Ackenhusen99], has inherent disadvantages such as relatively long acquisition times and the receiver constantly having to reacquire the signal following a loss-of-lock condition. Because of these shortcomings, it may not be the optimal architecture for positioning under challenging conditions when the GPS signal is severely attenuated (inside buildings, under dense foliage, etc.), is subject to high dynamics (in fast aircraft or rockets), multipath reflections (in urban environments, canyons, etc.), or interference conditions (during intentional and unintentional jamming). An alternate processing technique, known as *block processing*, has been shown to provide better performance under these conditions as described in [Moeglein98] and [UijtdeHaag99].

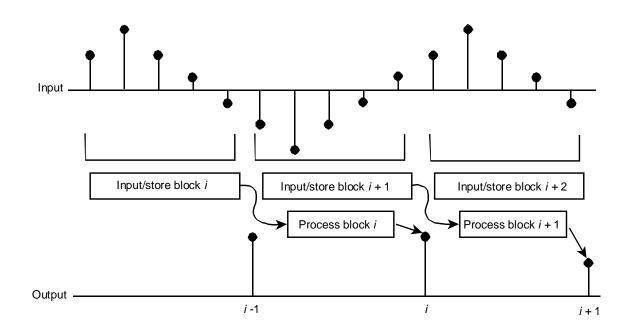

A block-processing scheme stores incoming samples in groups as they arrive. After the arrival of a sufficient number of samples (as set by the nature of the implementation), processing on the group begins. Because all input samples of the group, or block, are available simultaneously, processing can access the samples in a random manner rather than being restricted to sequential access. Figure 4.1 shows blocks of five samples being stored as they arrive. When the final sample of block *i* arrives, processing begins. At this point, two activities proceed together: the processing of block *i*, and the input and storage of block i+1. Block processing can be used when the input sample rate is much greater than the output sample rate [Ackenhusen99]. For a GPS receiver, processing is performed on a block of digital IF data to obtain code phase and Doppler offset values for each of the SVs being received. Since the block must cover at least a whole PRN code period (i.e. several thousand samples), and the output is only two values per SV, the conditions for block processing are satisfied.

Figure 4.1 Illustration of Block Processing for a Block of Five Samples

#### 4.1 GPS Data Collection System

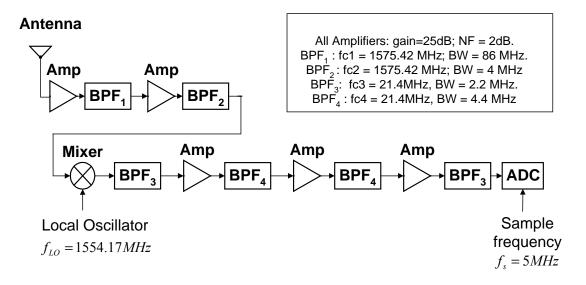

As a precursor towards developing a block-processing GPS/GLONASS receiver, a relatively novel receiver architecture known as a software radio was designed by Akos [Akos97]. Based on this work, and subsequent revisions, a standard GPS data collection

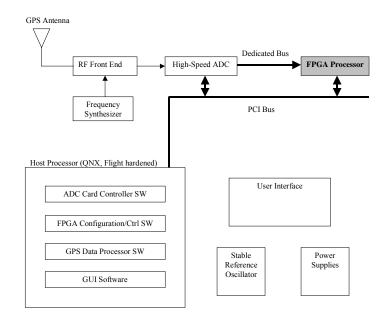

system for developing and testing block-processing algorithms designed by the Ohio University Avionics Engineering Center was used for this work. Figure 4.2 shows the block diagram of this setup.

Figure 4.2 GPS-SPS Data Collection System

Satellite data is collected through a roof-mounted antenna with an integrated 25 dB low noise amplifier (LNA). The first filter has a center frequency of 1575.42 MHz and a 3dB bandwidth of 86 MHz. The signal is amplified and filtered again before being mixed with the local oscillator frequency,  $f_{LO}$ , of 1554.17 MHz, resulting in a first standardized IF of 21.25 MHz. The IF is filtered to remove the double-frequency term followed by three more amplification and bandpass filtering stages to boost the signal to the sampling range of the ADC, while keeping out-of-band noise and spurious responses to a minimum. The signal is then sub-sampled at  $f_S = 5$  MHz, which results in the 21.25 MHz IF aliasing to 1.25 MHz, whilst preserving the 2.2 MHz information bandwidth of the original signal. This intentional undersampling of a bandpass filtered signal is known

as *bandpass sampling*, and results in a digital downconversion to the 1.25 MHz IF. Further details of bandpass sampling can be found in [Vaughan91]. The resulting digital IF data stream is currently stored in the hard disc of the PC housing the ADC card for post-processing [Snyder99]. The ADC has a quantization of 12 bits. Phase-noise due to sampling is kept to a minimum by using a Rubidium-referenced oven compensated crystal oscillator (OCXO).

The GPS-SPS sampled signal model presented in Equation 3.1 for the sequential case is modified for block processing as follows:

$$r_{i,k} = A_i G_{k,\tau_i} D_{i,\tau_i} \sin[2\pi (f_{IF} + \Delta f_i) T_S(m_i + k) + \phi_i] + n_{i,k}$$

(4.1)

Where:

| i             | : | $i^{\text{th}}$ block ( $i = 1, 2, 3,$ )                                               |

|---------------|---|----------------------------------------------------------------------------------------|

| k             | : | $k^{\text{th}}$ sample point starting at the $i^{\text{th}}$ block( $k = 1, 2,, M$ )   |

| $m_i$         | : | total number of samples before the <i>i</i> <sup>th</sup> block $m_i = (i-1) \times M$ |

| M             | : | number of samples per block, $M=5000$                                                  |

| $	au_i$       | : | time delay due to signal transmission for block <i>i</i>                               |

| $A_i$         | : | signal amplitude for block <i>i</i>                                                    |

| $G_{k,	au_i}$ | : | sampled, time delayed C/A code                                                         |

| $D_{i,	au_i}$ | : | navigation databit sign for block <i>i</i>                                             |

| $f_{IF}$      | : | center frequency of the digital IF, $f_{IF} = 1.25$ MHz                                |

| $\Delta f_i$  | : | frequency offset for block <i>i</i>                                                    |

| $T_S$         | : | sampling period (1/f <sub>s</sub> ), $T_s = 0.2 \ \mu s$                               |

| $\phi_i$      | : | phase offset for block <i>i</i>                                                        |

| $n_{i,k}$     | : | sampled noise term                                                                     |

Then, the frequency offset for block *i*,  $\Delta f_i$ , becomes:

$$\Delta f_i = \Delta f_{SV,i} + \Delta f_{D,i} + \Delta f_{LO,i} + \Delta f_{S,i}$$

(4.2)

Where:

| $\Delta f_{SV,i}$ | : | satellite frequency offset for block <i>i</i>        |

|-------------------|---|------------------------------------------------------|

| $\Delta f_{D,i}$  | : | Doppler frequency offset for block <i>i</i>          |

| $\Delta f_{LO,i}$ | : | local oscillator frequency offset for block <i>i</i> |

| $\Delta f_{S,i}$  | : | sample clock error for block I                       |

Since the sampled data must contain at least an entire C/A code period of 1 ms and the sample frequency is 5 MHz, the block size is chosen to be 5000 samples (i.e. M=5000).

A dataset of 1-second duration (i=1,2,3,...I; where I=1000) acquired from the above setup was used throughout this work. A NovAtel<sup>TM</sup> Millennium<sup>TM</sup> GPS Receiver was connected in parallel with the data acquisition system to monitor GPS parameters independently. Table 4.1 shows detectable SVs in the data along with their C/N<sub>0</sub> and Doppler frequencies [Feng99].

| Tuble 1.1 Of 5 Duta Set 1 drameters |                  |                 |          |                        |        |  |  |

|-------------------------------------|------------------|-----------------|----------|------------------------|--------|--|--|

|                                     | C/N <sub>0</sub> | $C/N_0$ (dB-Hz) |          | Doppler frequency (Hz) |        |  |  |