### DYNAMICALLY RECONFIGURABLE ARCHITECTURE FOR THIRD GENERATION MOBILE SYSTEMS

A Dissertation Presented to The Faculty of the Fritz J. and Dolores H. Russ College of Engineering and Technology Ohio University

> In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

> > by Ahmad M. Alsolaim

> > > August, 2002

Copyright © 2002

Ahmad Alsolaim

All rights reserved

#### THIS DISSERTATION ENTITLED

### "DYNAMICALLY RECONFIGURABLE ARCHITECTURE FOR THIRD GENERATION MOBILE SYSTEMS"

by Ahmad Alsolaim

has been approved

for the School of Electrical Engineering and Computer Science and the Russ College of Engineering and Technology

Janusz Starzyk, Professor School of Electrical Engineering and Computer Science

> Dennis Irwin, Dean Fritz J. and Dolores H. Russ College of Engineering and Technology

### Acknowledgement

In the Name of Allah, the Most Beneficent, the Most Merciful. All praise and thanks to Allah, lord of the universe and all that exists. Prayers and peace be upon His prophet Mohammed, the last messenger for all humankind.

First, I thank Allah for His guidance and the completion of this work. I am deeply thankful to my mother. I will never forget her patience and dedication to my brothers, my sister, and me.

I want to express my gratitude to my committee chair, Prof. Janusz Starzyk, for his personal and academic guidance. Dr. Starzyk was more than an academic advisor. He was a friend during the years I have been at Ohio University.

Thank you to my other committee members. Prof. Dennis Irwin, Dr. Jeffrey Dill, Dr. Michael Braasch, Dr. Mehemet Celenk, and Prof. Larry Snyder.

A special thank you to my wife, Thuriya, for her patience especially for the long years of waiting for the completion of this work. My daughters, Shatha and Leen, also receive my heart-felt thanks, without them life has no joy.

I must thank my brothers and sister for their love and support. A special appreciation to my oldest brother, Abdulrahman (Abu Mo'taz). He was and still is filling the place of my father. He believed in me and always expected more of me. His guidance and support in every step of my live is well appreciated.

Thank you to my friends Suliman Altwaijre, Abdulmalik Alhogail, Ahmad Alshumrani, and Bassam Alkharashi in Cleveland, OH when I earned an MS at Case Western Reserve University. I am especially grateful to Suliman for the help and support during the hard days when I was in Cleveland.

I am particularly thankful for my long-time friend, Abdulqadir Alaqeeli. During the years I have known him, he always helped and supported me. Without him this work will never be completed. I want to thank Saleh Alotaiwe. Saleh has been my big brother. His words and actions are so valuable and appreciated. A special thanks to Mohammed Altamimi and Mazyad Almohailb for their valuable friendship. A special thanks to two friends Abdulrahman Alsebail, and Rashed Alsedran who helped me in many ways. I extend my thanks to Mingwei Ding for tireless hours of discussions about the design of the architecture.

Thanks go to Professor Manfred Glesner who is the head of the Institute of Microelectronics System Designs, Darmstadt, Germany, and to Dr. Ing. Jurgen Becker for the opportunity to join the Institute and establish my research. I am indebted to Dr. Becker for showing me how to look forward and think without limitations. I also learned how to write scholarly papers in a professional manner.

My family and I are so grateful to Hamad Al-brathin and his lovely family for being our extended family. Hamad is help and generosity is well appreciated.

I wish to express my deep gratitude to Dr. Zahiah Bin Za'roor, my academic advisor at the Saudi Cultural Mission in Washington, DC. Her support and great personality were major helps factors in the completion of this work.

Many people contributed to this work, either directly or indirectly. Thanking every one by name would take many pages. Therefore, for the people I did not mentioned in this acknowledgment, from my heart THANK YOU.

# **Table of Contents**

| -                                                                                         | iii      |

|-------------------------------------------------------------------------------------------|----------|

| Table of Contents                                                                         | v        |

| List of Tables                                                                            | x        |

| List of Figures                                                                           | xi       |

| List of Symbols and Abbreviations                                                         | xvi      |

| Chapter 1                                                                                 | 1        |

| Introduction                                                                              | 1        |

| 1.1 Motivations                                                                           | 1        |

| 1.2 Related Work                                                                          | 3        |

| 1.3 Project Goals and Objectives                                                          | 13       |

| 1.4 Dissertation Outline                                                                  | 15       |

| Chapter 2                                                                                 | 16       |

|                                                                                           | 16       |

| Third and Future Generations Mobile Systems                                               | 10       |

| Third and Future Generations Mobile Systems         2.1 Introduction                      |          |

| -                                                                                         | 16       |

| 2.1 Introduction                                                                          | 16<br>16 |

| <ul><li>2.1 Introduction</li><li>2.2 Overview of the Third Generation Systems</li></ul>   | 16<br>   |

| <ul> <li>2.1 Introduction</li> <li>2.2 Overview of the Third Generation Systems</li></ul> | 16<br>   |

| <ul> <li>2.1 Introduction</li> <li>2.2 Overview of the Third Generation Systems</li></ul> |          |

| <ul> <li>2.1 Introduction</li></ul>                                                       |          |

| <ul> <li>2.1 Introduction</li></ul>                                                       |          |

| 3.3 Baseb   | and Signal Processing Requirements                       |    |

|-------------|----------------------------------------------------------|----|

| 3.3.1       | Digital Filters                                          | 35 |

| 3.3.2       | Searcher                                                 |    |

| 3.3.3       | RAKE Receiver and Maximal Ratio Combining                | 43 |

| 3.3.4       | Turbo Coding                                             | 50 |

| Chapter 4   |                                                          | 57 |

| Computing A | Architecture Models                                      | 57 |

| 4.1 Introd  | luction                                                  | 57 |

| 4.2 Curren  | nt Computer Architectures                                | 58 |

| 4.3 ASIC    | implementation                                           | 61 |

| 4.4 DSP I   | mplementation                                            | 62 |

| 4.5 FPGA    | Implementation                                           | 63 |

| 4.6 Dynai   | mically Reconfigurable Computing                         | 68 |

| 4.7 IP-bas  | sed Mapping                                              | 72 |

| 4.8 Mode    | ling a Reconfigurable Architecture                       | 74 |

| Chapter 5   |                                                          | 77 |

| Dynamically | Reconfigurable Architecture                              | 77 |

| 5.1 Introd  | luction                                                  | 77 |

| 5.2 The D   | Dynamically Reconfigurable Architecture (DRAW) Model     | 77 |

| 5.3 Dynai   | mically Reconfigurable and Parallel Array Architecture   | 83 |

| 5.3.1       | Regular and Simple Array Structure                       | 85 |

| 5.3.2       | Special Processing Units                                 | 86 |

| 5.          | 3.2.1Configurable Linear Feedback Shift Register (CLFSR) | 87 |

| 5.          | 3.2.2Configurable Spreading Data Path (CSDP)             | 87 |

| 5.3.3       | RAM and FIFO Storage                                     | 90 |

| 5.3.4       | Scale and Delay                                          | 90 |

| 5.3.5       | Communication Network                                    | 91 |

| 5.3.6       | Dedicated I/O                                            | 93 |

| 5.3.7       | Fast Dynamic Reconfiguration                             | 94 |

vi

|              |                                                                   | vii |

|--------------|-------------------------------------------------------------------|-----|

| Chapter 6    |                                                                   | 97  |

| Dynamically  | Reconfigurable Architecture Design                                | 97  |

| 6.1 Introd   | uction                                                            | 97  |

| 6.2 Design   | n Goals                                                           | 97  |

| 6.3 Design   | n Process Flow                                                    | 98  |

| 6.4 Opera    | tion Profile                                                      | 106 |

| 6.5 Hardw    | vare Structure of the DRAW Architecture                           | 112 |

| 6.5.1        | Dynamically Reconfigurable Processing Unit (DRPU)                 | 113 |

| 6.           | 5.1.1Dynamically Reconfigurable Arithmetic Processing unit (DRAP) | 115 |

| 6.           | 5.1.2The DRPU Controller                                          | 117 |

| 6.           | 5.1.3The RAM/FIFO Unit                                            | 120 |

| 6.           | 5.1.4The Configurable Spreading Data Path (CSDP)                  | 120 |

| 6.           | 5.1.5DRPU I/O interfaces.                                         | 122 |

| 6.5.2        | Fast Inter-DRPU local and Global Communication Mechanism          | 123 |

| 6.5.3        | DRPU Configuration Bits                                           | 123 |

| 6.6 Area a   | and Performance Figures                                           | 129 |

| Chaptor 7    |                                                                   | 100 |

| Chapter 7    |                                                                   | 132 |

| Mapping Ex   | amples                                                            | 132 |

| 7.1 Introd   | luction                                                           | 132 |

| 7.2 Mapp     | ing Gold-Code Generator                                           | 133 |

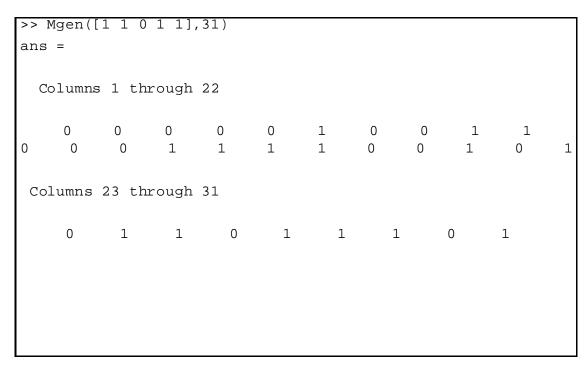

| 7.2.1        | M-sequence Generator Using One DRPU                               | 135 |

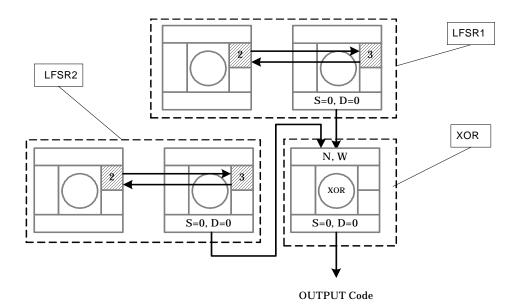

| 7.2.2        | M-sequence Generator Using Two DRPUs (5-Stage LFSR)               | 137 |

| 7.2.3        | Gold code Generator                                               |     |

| 7.3 Mapp     | ing an FIR filter                                                 | 142 |

| Chapter 8    |                                                                   | 147 |

| Conclusion a | and Recommendations                                               | 147 |

| 8.1 Concl    | usion                                                             | 147 |

| 8.2 Recon    | nmendations for Future Work                                       | 150 |

| App | endix A                                                      | 151 |

|-----|--------------------------------------------------------------|-----|

| WCD | MA Matlab Codes                                              | 151 |

| 1   | Data Generation.                                             |     |

| 2   | Code Generation                                              |     |

| 3   | RAKE Receiver                                                |     |

| 4   | Searcher                                                     |     |

| 5   | Channel Estimation                                           | 162 |

| 6   | Maximal Ratio Combining                                      | 164 |

| Арр | endix B                                                      | 165 |

| DRA | W Architecture VHDL Codes                                    | 165 |

| 1   | DRPU Top Level                                               | 165 |

| 2   | Communication and Switching Unit                             |     |

| 3   | Configuration Memory Unit                                    |     |

| 4   | Dedicated I/O Unit                                           |     |

| 5   | Arithmetic and Logical Unit                                  |     |

| 6   | Booth Decoder Unit                                           |     |

| 7   | Barrel shifter                                               |     |

| 8   | RAP configuration control unit                               |     |

| 9   | Configurable Linear Feedback Shift Regester Unit             |     |

| 10  | O Configurable Linear Feedback Shift Regester interface Unit |     |

| 11  | 16-bit Full Adder unit                                       | 236 |

| 12  | 2 DRPU input interface unit                                  |     |

| 13  | 3 DRPU output interface unit                                 |     |

| 14  | Paralle to serial unit                                       |     |

| 15  | 5 RAM/FIFO unit                                              |     |

| 16  | 5 RAM/FIFO Interface                                         |     |

| 17  | 7 Dynamically Reconfigurable Processing Unit (DRAP)          |     |

| 18  | 3 DRAP interface unit                                        |     |

| 19  | Scaling Register                                             |     |

viii

| 20 Serial to Paralle unit                          |  |

|----------------------------------------------------|--|

| 21 Configurable Spreading Data Path Unit (CSDP)    |  |

| 22 Configurable Spreading Data Path Unit Interface |  |

| References                                         |  |

| Abstract                                           |  |

## List of Tables

| Table 2-1. A list of different wireless mobile generations    17               |

|--------------------------------------------------------------------------------|

| Table 2-2. Radio transmission technology proposals for IMT-2000       19       |

| Table 2-3. Standardized Parameters of WCDMA       21                           |

| Table 2-4. Standardized Parameters of cdma2000       26                        |

| Table 3-1. Estimation of signal processing load for 3G baseband @ 384 kbps     |

| Table 3-2. Matlab simulation parameters of the turbo encoder/decoder.       53 |

| Table 6-1. A list of DRAP operations       119                                 |

| Table 6-2. An example of the barrel shifter operation.       119               |

| Table 6-3. Configuration table of the DRPU input interface       122           |

| Table 6-4. DRPU configuration bits structure    127                            |

| Table 6-5. Area consumed by each component of the DRPU                         |

| Table 6-6. Area consumed by one unit design       130                          |

| Table 6-7. Performance of the different operations of the DRPU       131       |

| Table 7-1. Implementation cost of 8-stages 4 taps on DRAW and Virtex       142 |

# **List of Figures**

| Figure 1-1: SoC-Architecture components of a Baseband single chip mobile receiver3                                           |

|------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2: A block model of the mesh-based reconfigurable architectures with local connection to the nearest four neighbors |

| Figure 1-3: 3x3 segment of KressArray architectural structure7                                                               |

| Figure 1-4: Morphosys architecture components                                                                                |

| Figure 1-5: The structure of the Reconfigurable Cell (RC) of the Morphosys system9                                           |

| Figure 1-6: Chameleon CS2000 Reconfigurable Communications Processor and<br>Reconfigurable Processing Fabric (RPF)12         |

| Figure 2-1: The frequency spectrum allocations for UTRA20                                                                    |

| Figure 2-2: The radio frame structure downlink DPCH of the WCDMA FDD system23                                                |

| Figure 2-3: Current and future generations of wireless mobile systems vs. their transmission rates                           |

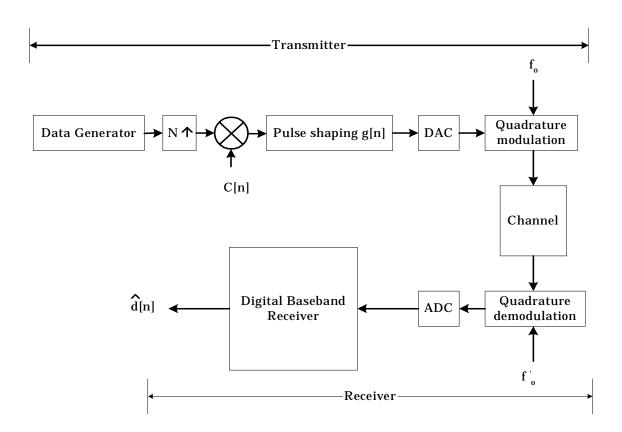

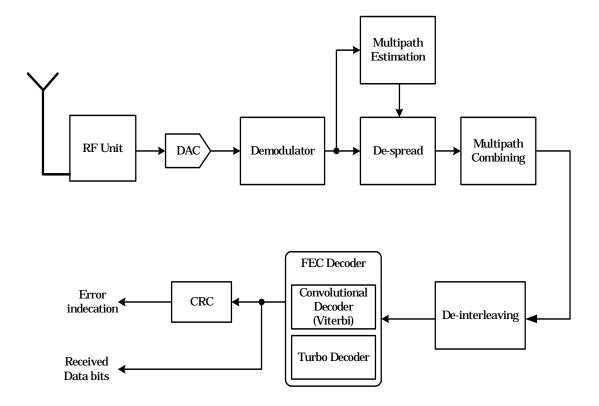

| Figure 3-1: A block diagram of 3G receiver                                                                                   |

| Figure 3-2: The baseband receiver front-end                                                                                  |

| Figure 3-3: Complete block diagram of the receiver front end                                                                 |

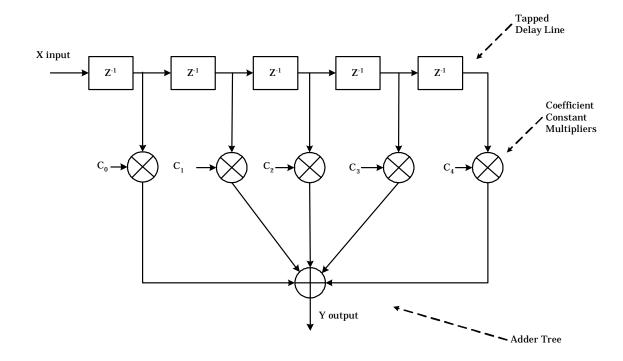

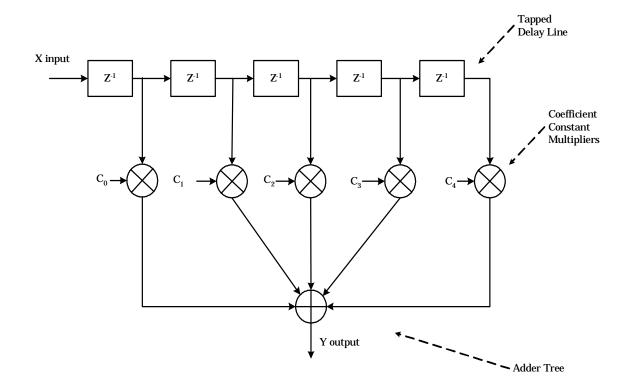

| Figure 3-4: A tapped delay line model of an FIR filter                                                                       |

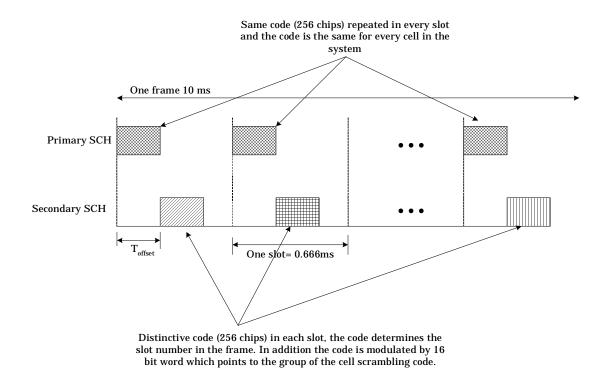

| Figure 3-5: Structure of the synchronization channel (SCH)40                                                                 |

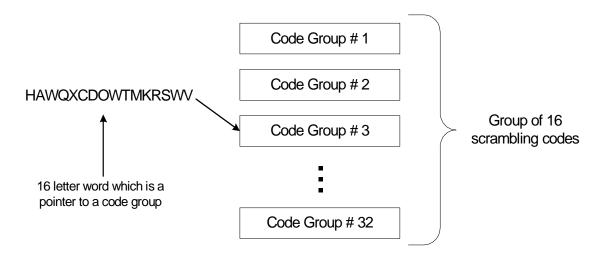

| Figure 3-6: The secondary synchronization groups of codes40                                                                  |

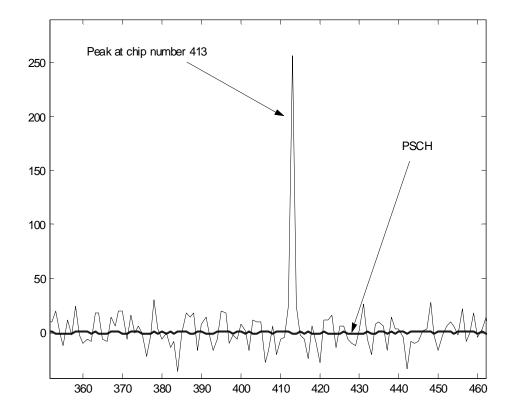

| Figure 3-7: A Matlab code fragment to simulate the Primary Synchronization Channel<br>(PSCH)                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3-8: Matlab simulation of the PSCH search43                                                                                                                                                  |

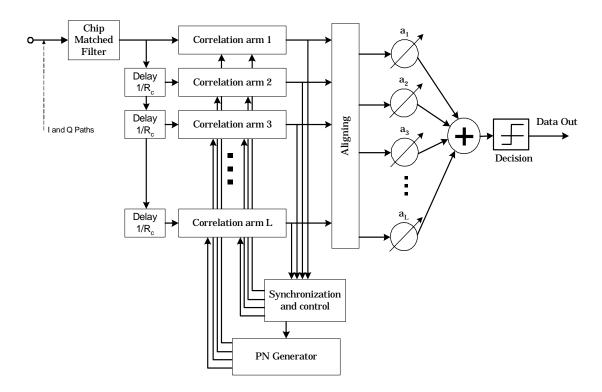

| Figure 3-9: A block diagram of L-arms RAKE receiver45                                                                                                                                               |

| Figure 3-10: Communication-link level model for the RAKE receiver simulation46                                                                                                                      |

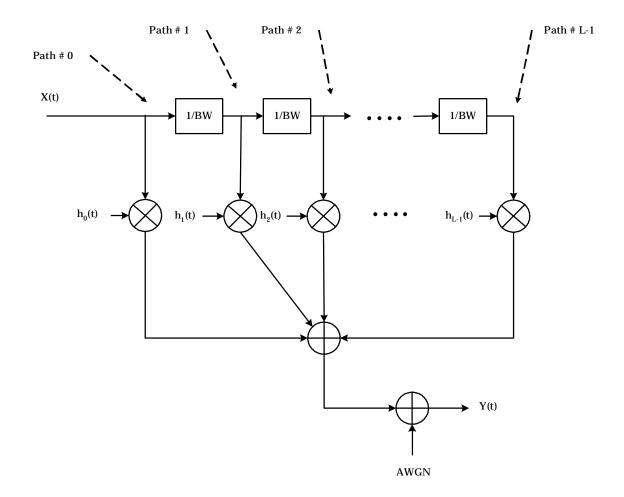

| Figure 3-11: Tapped-Delay channel model47                                                                                                                                                           |

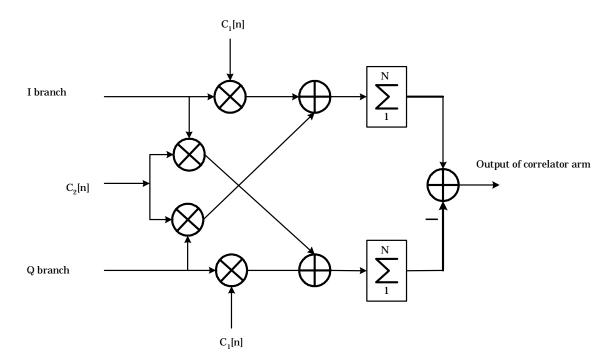

| Figure 3-12: One Rake finger correlation arm                                                                                                                                                        |

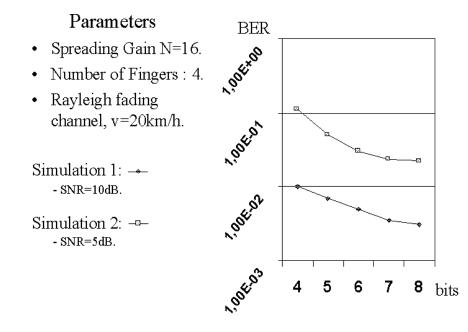

| Figure 3-13: The BER as a function of the number of bits used for the quantization of incoming data                                                                                                 |

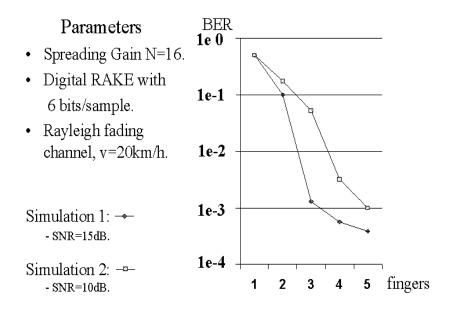

| Figure 3-14: BER as a function of number of RAKE fingers                                                                                                                                            |

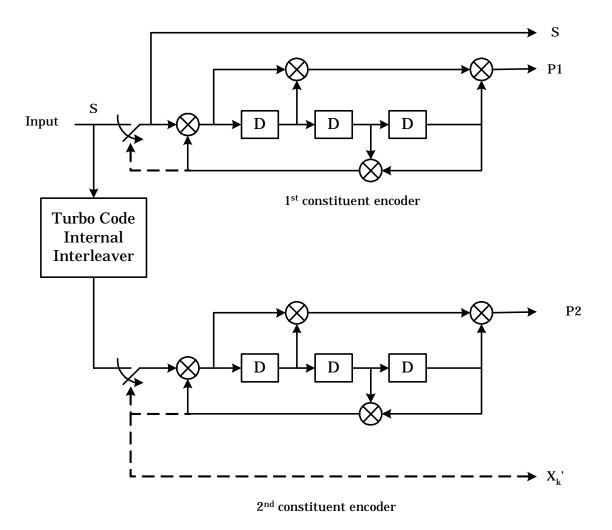

| Figure 3-15: 3GPP proposed structure of the turbo coder for WCDMA52                                                                                                                                 |

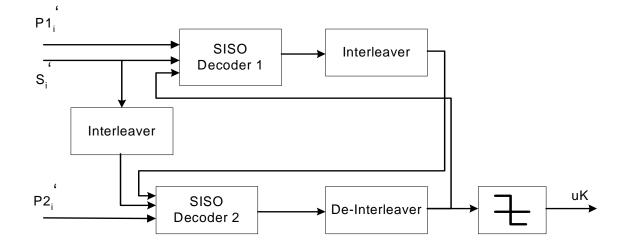

| Figure 3-16: Turbo Decoder structure53                                                                                                                                                              |

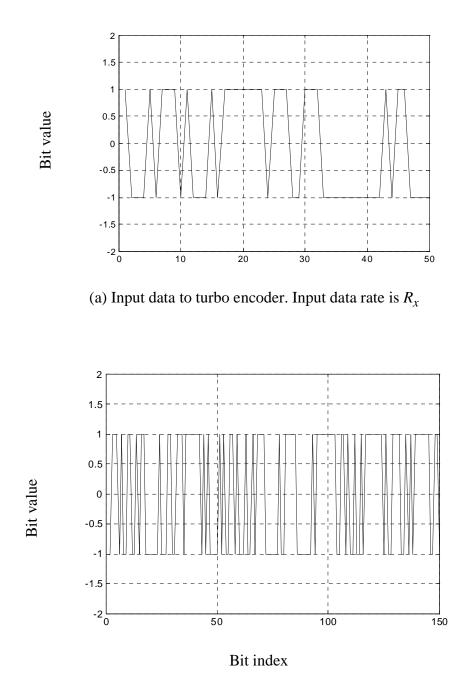

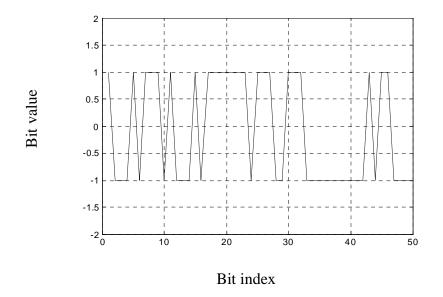

| Figure 3-17: Matlab simulation of turbo encoder: (a) input to the encoder (b) encoded data bits                                                                                                     |

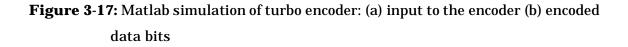

| Figure 3-18: Turbo decoder output data after three iterations                                                                                                                                       |

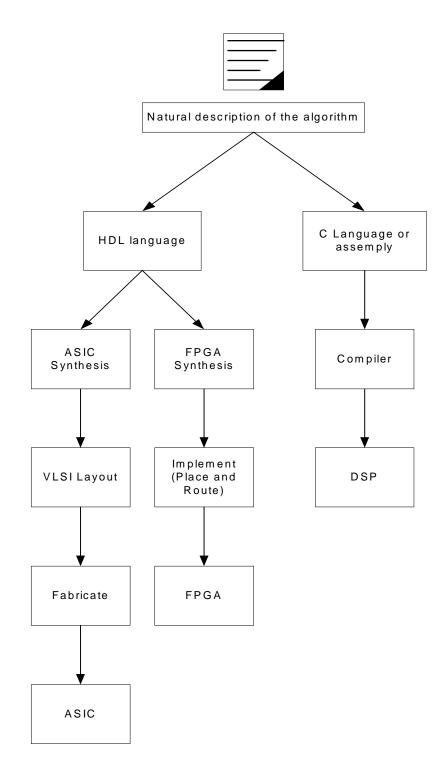

| Figure 4-1: Design process flow of different hardware implementations60                                                                                                                             |

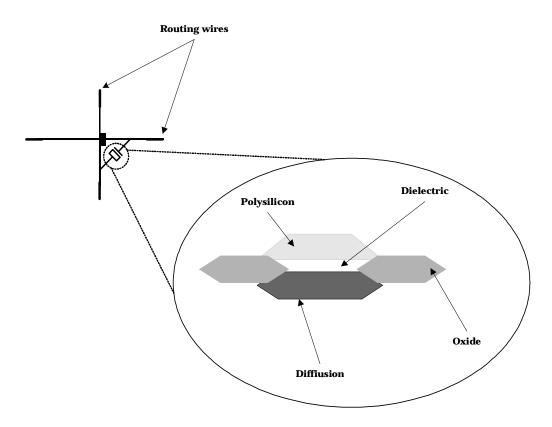

| Figure 4-2: An Anti-fuse switch for non-volatile FPGAs64                                                                                                                                            |

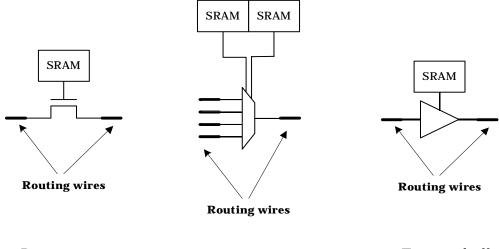

| Figure 4-3: SRAM cell for SRAM based FPGAs65                                                                                                                                                        |

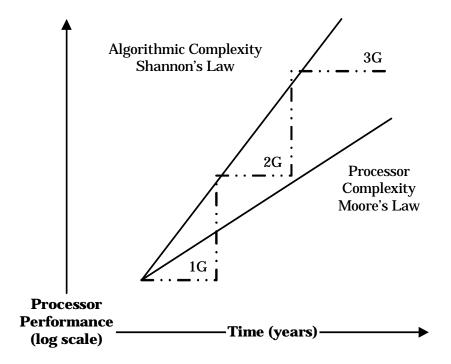

| Figure 4-4: Algorithmic complexity of wireless mobile systems is increasing faster than<br>the increase in the available processing power. Source: Jan Rabaey, Berkeley<br>Wireless Research center |

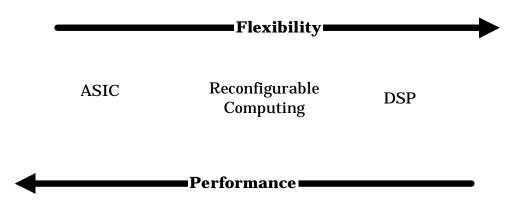

| Figure 4-5: Performance and flexibility for different implementation methods70                                              |

|-----------------------------------------------------------------------------------------------------------------------------|

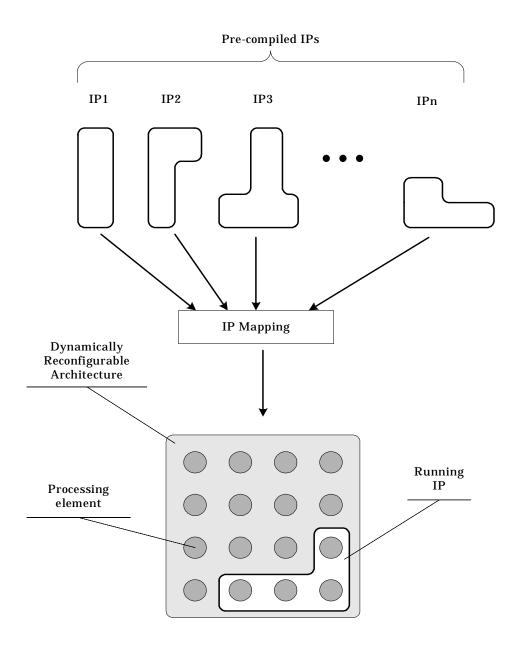

| Figure 4-6: IP-based mapping method73                                                                                       |

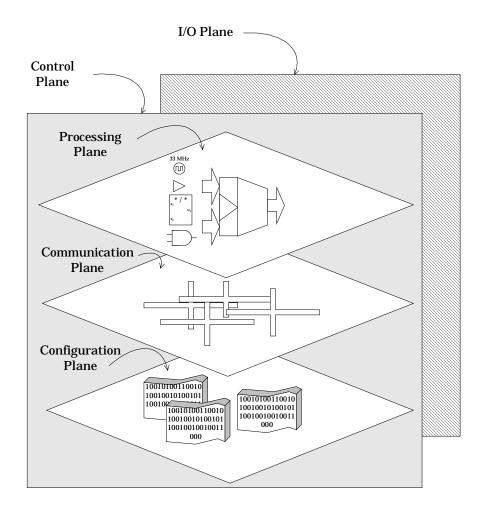

| Figure 5-1: An abstract planar model for the dynamically reconfigurable architecture 79                                     |

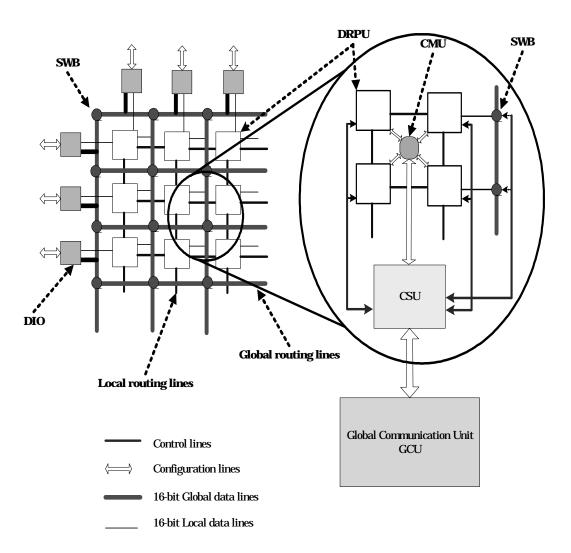

| Figure 5-2: A block diagram of the DRAW architecture84                                                                      |

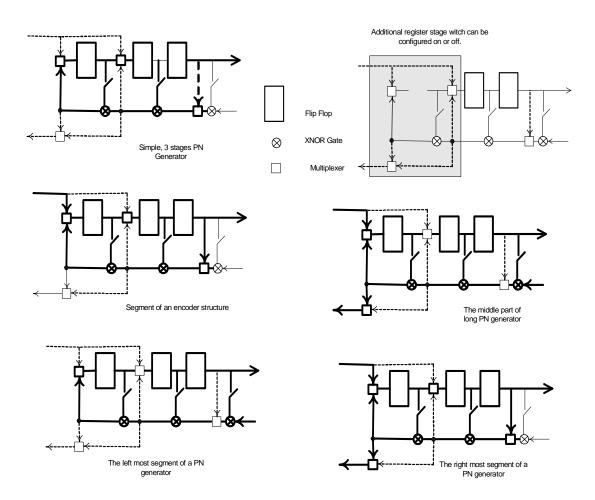

| Figure 5-3: Different possible configurations of the configurable linear feedback shift register                            |

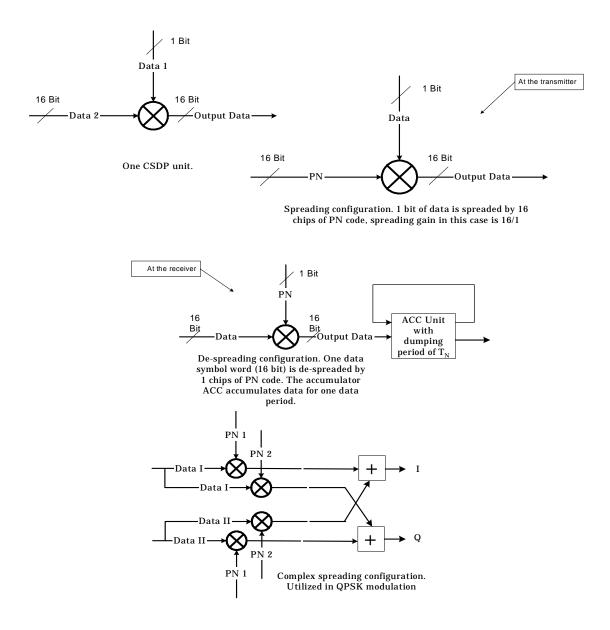

| Figure 5-4: Some configuration structures of the CSDP                                                                       |

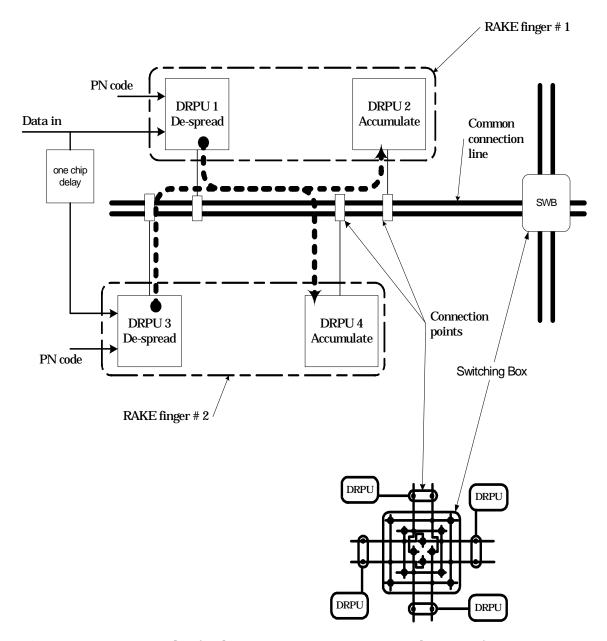

| Figure 5-5: An example of a deterministic communication between four DRPUs92                                                |

| Figure 5-6: A VHDL simulation of the start-hold mechanism of the DRPU93                                                     |

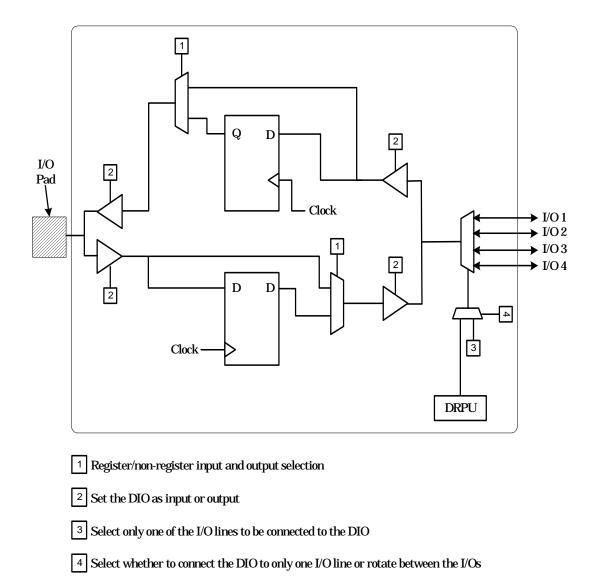

| Figure 5-7: A block diagram of the dedicated I/O unit95                                                                     |

| Figure 5-8: The configuration level structure for fast reconfiguration mechanism96                                          |

| Figure 6-1: Design flow process of the DRAW architecture99                                                                  |

| Figure 6-2: Block diagram of a transmitter which supports 3GPP standard100                                                  |

| Figure 6-3: 3GPP downlink scrambling code generator103                                                                      |

| Figure 6-4: Block diagram of a receiver baseband which supports 3GPP standard104                                            |

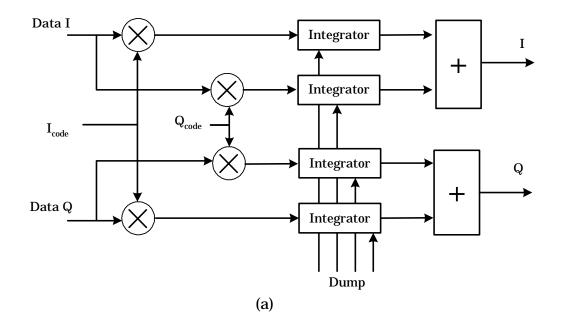

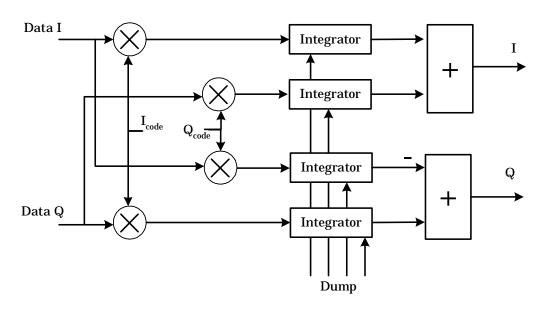

| Figure 6-5: Despreading circuit for QPSK chip modulated signal. (a) Dual-channel despreading and (b) complex despreading105 |

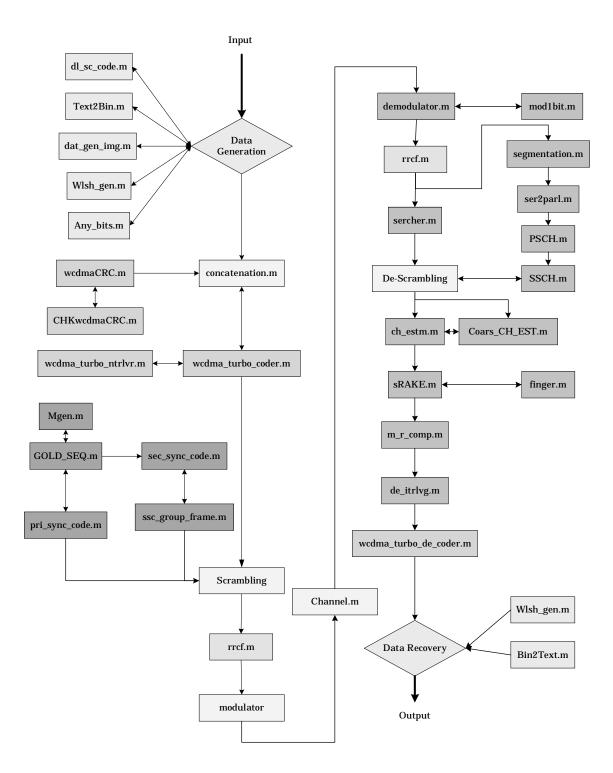

| Figure 6-6: Matlab simulation environment functions108                                                                      |

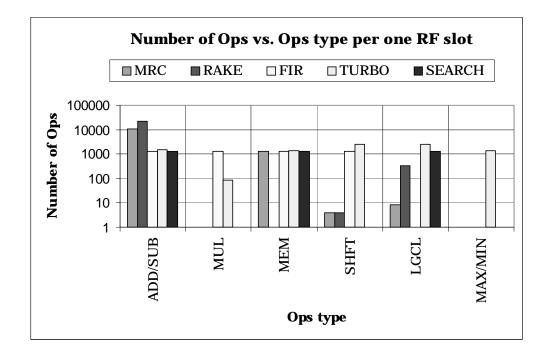

| Figure 6-7: Slot structure of 3GPP standard for WCDMA109                                                                    |

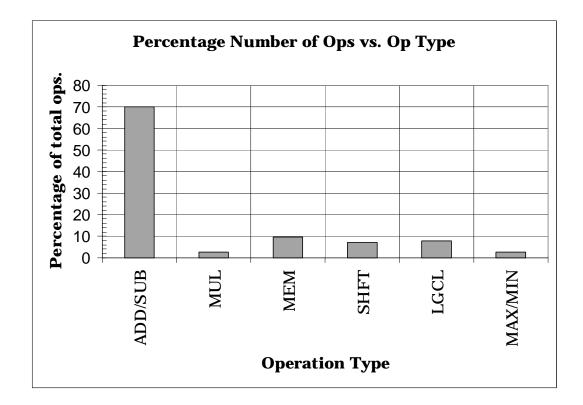

| Figure 6-8: Number of operations vs. operation type for one RF slot (log scale)110                                          |

| Figure 6-9: Percentage of the total number of operations for each operation111                                                     |

|------------------------------------------------------------------------------------------------------------------------------------|

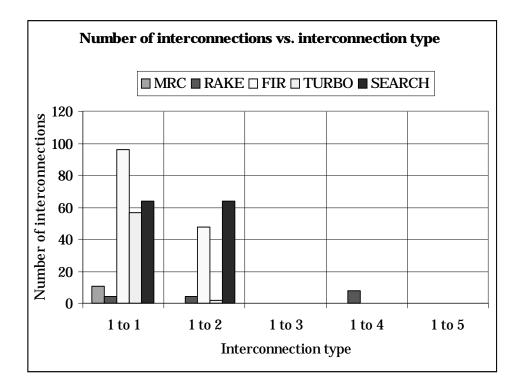

| Figure 6-10: Number of interconnections of each application versus the types of connection                                         |

| Figure 6-11: Percentage of interconnections of each application versus the type of connection                                      |

| Figure 6-12: Dynamically Reconfigurable Processing Unit DRPU114                                                                    |

| Figure 6-13: Dynamically Reconfigurable Processing Unit (DRPU) top level symbol116                                                 |

| Figure 6-14: Dynamically Reconfigurable Arithmetic Processing Unit (DRAP)117                                                       |

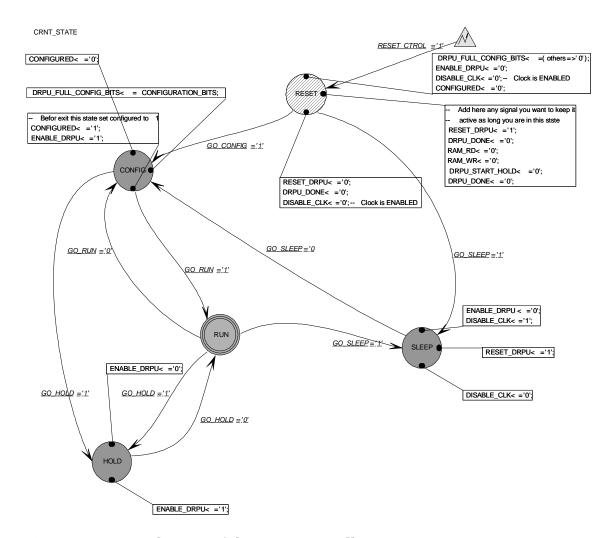

| Figure 6-15: FSM diagram of the DRPU controller118                                                                                 |

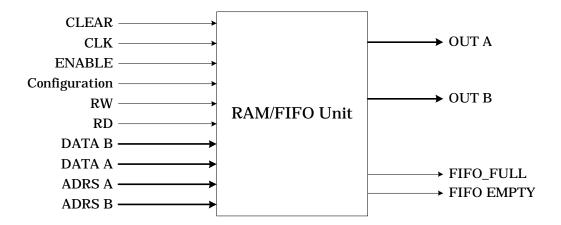

| Figure 6-16: A block diagram of the RAM/FIFO unit showing its signal interface120                                                  |

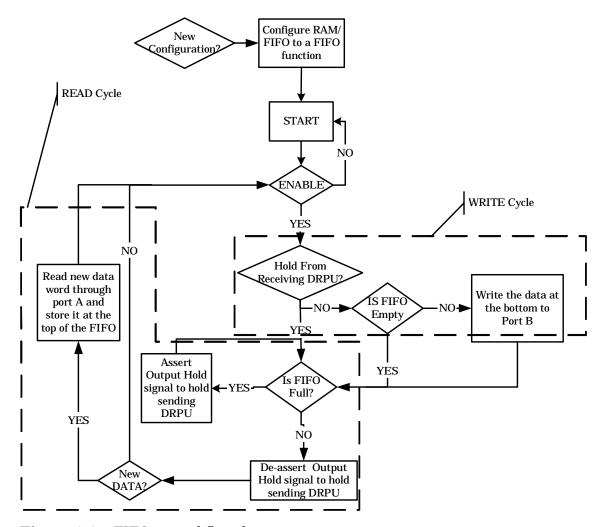

| Figure 6-17: FIFO control flow diagram121                                                                                          |

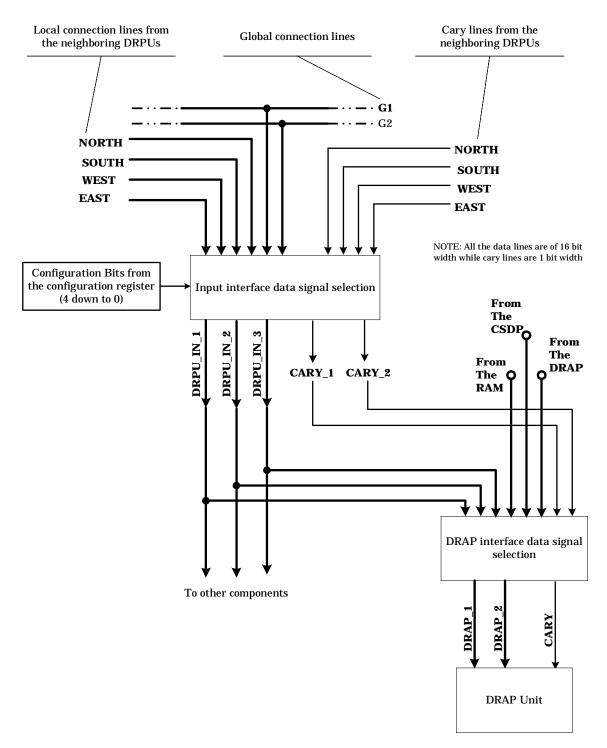

| Figure 6-18: Input and DRAP interfaces selection diagram of the data lines124                                                      |

| Figure 6-19: DRPU Communication structure125                                                                                       |

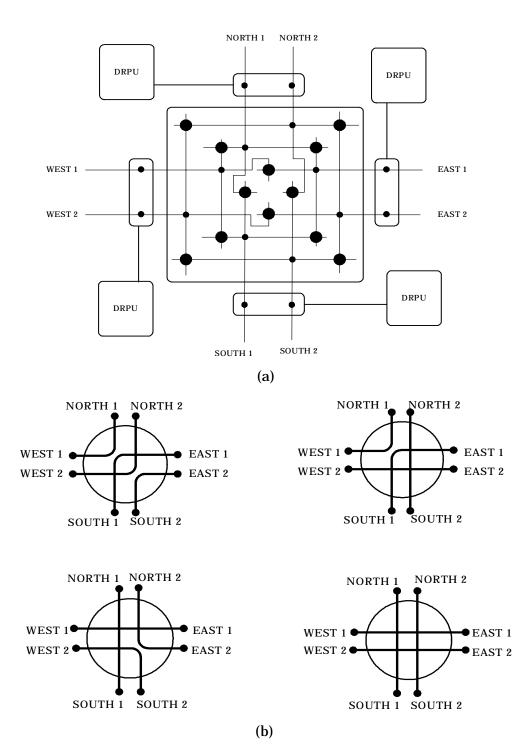

| Figure 6-20: A connection topology for the SWB: (a) Complete connection lines. (b)<br>Example of two lines connected               |

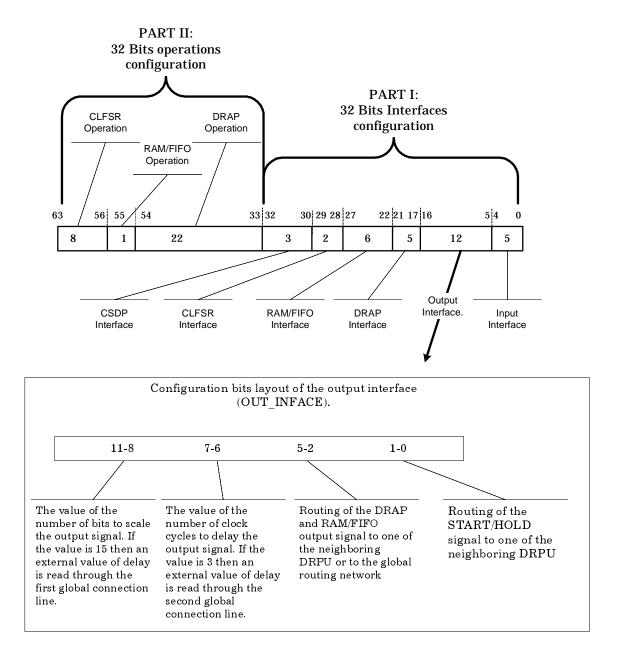

| Figure 6-21: The configuration bits structure of one DRPU (the configuration of the output interface is detailed as an example)128 |

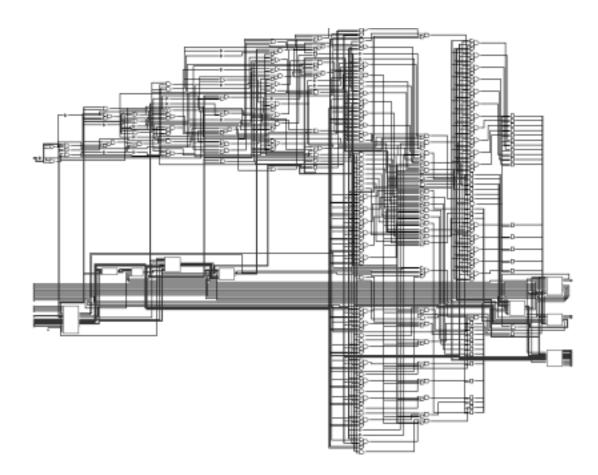

| Figure 6-22: The schematic diagram of the synthesized DRPU using Leonardo Spectrum                                                 |

| Figure 7-1: Symbolic representation of the DRPU to show the general configuration .133                                             |

| Figure 7-2: An example of the use of the DRPU symbolic representation134                                                           |

| Figure 7-3: N-stages linear feedback shift register135                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------|

| Figure 7-5: A symbolic representation of one DRPU configured as a three-stage LFSR                                                    |

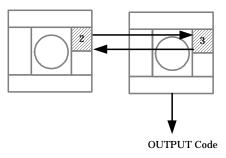

| Figure 7-4: Matlab code fragment of M-sequence generator                                                                              |

| Figure 7-6: CLFSR output for a three-stage M-sequence with polynomial $1+X^2$ 137                                                     |

| Figure 7-7: The symbolic representation of two DRPU configured as a five-stage LFSR                                                   |

| Figure 7-8: Matlab output of the M-gen function generated for the polynomial $1+x+x^2+x^4+x^5$                                        |

| Figure 7-9: The output of an M-sequence generator for the polynomial $1+x+x^2+x^4+x^5$ mapped onto two DRPUs                          |

| Figure 7-10: Symbolic representation of Gold code generator mapped onto five DRPUs                                                    |

| Figure 7-11: MATLAB Code of Gold code generator function and the output run for the two polynomials $1+x^2+x^5$ and $1+x+x^2+x^4+x^5$ |

| Figure 7-12: The output of the mapped Gold code generator onto five DRPUs142                                                          |

| Figure 7-13: Typical implementation of FIR filter143                                                                                  |

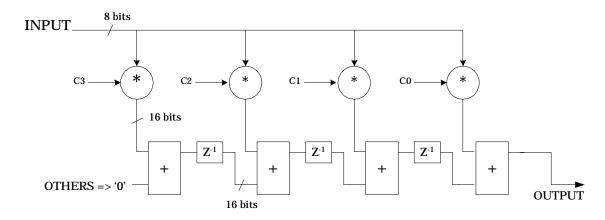

| Figure 7-14: Transposed FIR filter implementation144                                                                                  |

| Figure 7-15: A Matlab code of an FIR filter145                                                                                        |

| Figure 7-16: Symbolic representation of the mapping of 4-taps FIR filter onto DRAW                                                    |

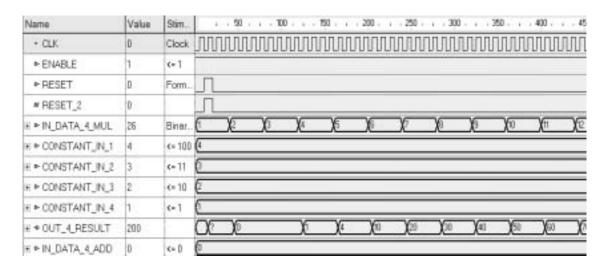

Figure 7-17: Simulation waveform of a four-tap FIR filter mapped onto six DRPUs ...146

## List of Symbols and Abbreviations

- 3GPP: Third Generation Partner Project

- AFC: Automatic Frequency Controller

- AGC: Automatic Gain Controller

- ASIC: Application Specific Integrated Circuits

- BER: Bit Error Rate

- CCM: Custom Computing Machines

- cdma2000: Wideband spread spectrum radio interface standard developed by the TIA

of the USA

- CLFSR: Configurable Linear Feedback Shift Register

- CMU: Configuration Memory Unit

- CSDP: Configurable Spreading Data Path

- CSU: Communication Switching Unit

- DIO: Dedicated I/O unit

- DRAW: Dynamically Reconfigurable Architecture for future generation Wireless mobile systems

- DRPU: Dynamically Reconfigurable Processing Unit

- DS-SS: Direct Sequence-Spread Spectrum

- DSP: Digital Signal Processor

- FDD: Frequency Division Duplex

- FPGA: Field Programmable Gate Array

- GCU: Global Communication Unit

- GPS: Global Positioning System

- HDL: Hardware Description Language

- IIR: Infinite Impulse Response

- IP: Intellectual Propriety

- IS-95: Second generation CDMA standard developed by TIA

- ITU: International Telecommunications Union

- OVSF: Orthogonal Variable Spreading Factor

- PE: Processing Element

- PSCH: Primary Synchronization Channel

- QoS: Quality of Service

- **QPSK:** Quadrature Phase Shift Keying

- rDPU: reconfigurable Data Processing Units

- RRC: Root Raised Cosine

- RSC: Recursive Systematic Convolutional

- SF: Spreading Factor

- SNR: Signal to Noise Ratio

- SoC: System on a Chip

- SSCH: Secondary Synchronization Channel

- SWB: Switching Box

- TIA: Telecommunications Industry Association

- UMTS: Universal Mobile Telecommunications System

- UTRA: UMTS Terrestrial Radio Access

- WCDMA: Wideband Code Division Multiple Accesses

### Chapter 1

### Introduction

#### 1.1 Motivations

The evolving of broadband access techniques into the wireless domain introduces difficult and interesting challenges to the system architecture design. The system designers are faced with a challenging set of problems that stem from access mechanisms, energy conservation, a required low error rate, transmission speed characteristics of the wireless links, and mobility aspects such as small size, light weight, long battery life, and low cost. Currently, most of the hardware solutions for mobile terminal implementation are a combination of application-specific integrated circuits (ASICs) and digital signal processor (DSP) devices.

Future generations of mobile terminals will necessitate integrating reconfigurable architectures with the so-called System-on-a-Chip (SoC) solution. This requirement stems from the increasing variety and Quality of Services (QoS) that must be supported by the mobile terminal with high reliability and strict limitations for power consumption and size.

Reconfigurable architectures, e.g., those based on the Field Programmable Gate Arrays (FPGAs) are being recognized as an alternative solution for DSP processing. "Wireless is in many cases the driver for DSP processing on reconfigurable logic." said Will Strauss, who is the president of Forward Concepts and one of the leading analysts on the DSP marketplace and technology. "The processing power needed for the wireless infrastructure has been increasing, and in many instances is greater than past and most current DSPs could supply. Thus, designers have turned to FPGAs to do the on-the-fly, front-end processing" [1]. The current method of handling complex processing problems is to use more and faster logic gates. Today's leading FPGAs have already passed the 1M logic gates count barrier with internal system clock rates of 200 MHz. The most powerful FPGA architecture at this time is Xilinx Virtex II, which provides up to 10M gates. By exploring tradeoffs between design flexibility, power, and performance, functions can be migrated from ASIC or DSP to the reconfigurable architecture, eliminating a need for the ASIC or releasing the DSP for other tasks [2].

Flexibility of the mobile terminal can be defined on two levels. First at the level of systems operation, flexibility can be defined as the ability of the mobile terminal to support many modes of operation, e. g., voice, audio, video, web browsing, GPS, data transmission, etc. while using the same limited set of hardware. Second, at the communication link level, flexibility can be defined as the ability of the mobile device to operate in two or more different wireless communication standards, e.g., GSM and IS-95.

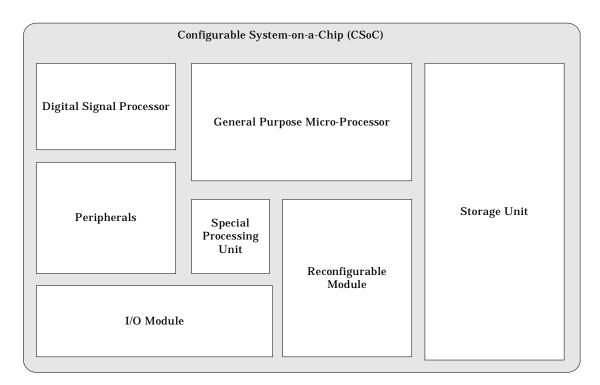

Another important requirement for a mobile terminal is its adaptability. Adaptability is defined as the ability of the mobile terminal to easily and quickly accommodate changes in the standards or the introduction of new services. Flexibility can thus be viewed as a subset of adaptability. An adaptable and flexible hardware/software system-on-a-chip target architecture for digital baseband processing will consist of a mixture of DSP and micro-controller cores, and reconfigurable hardware parts. The system-on-a-chip also includes some glue logic and ASIC parts, as shown in Figure 1-1.

#### 1.2 Related Work

During recent years, a number of research efforts focused on the design of new reconfigurable systems for general purpose and for particular areas of application. The driving force behind such growth in the number of research activities is the potential of reconfigurable computing to greatly accelerate a wide variety of

Figure 1-1: SoC-Architecture components of a Baseband single chip mobile receiver

applications. The work in this area flows in two major directions. The first hardware oriented direction is geared toward designing new hardware architectures or optimizing the current architectures. The second software oriented sub-area of research is focused on the investigation of new placement, routing, and mapping methods that tackle the dynamic reconfiguration challenges.

The work in the area of developing new reconfigurable architectures covers the research on coarse-grained and fine-grained reconfigurable architectures. Additionally, some of these architectures are created of more than one reconfigurable chips (see for example [3], [4], and [5]). These architectures (or rather systems) are called a Custom Computing Machines (CCM). In this section of the dissertation I will focus only on coarse-grained-single-chip architectures, since they are related to this work.

Fine-grain reconfigurable architectures are built around one-bit processing elements, called logic blocks. Commercial FPGAs like Xilinx 4000 FPGA family [6], and Altera Flex 8000 FPGA family [7] are good examples of fine-grain configurable architectures. Fine-grain architectures are useful for bit-level manipulation of data which can be found in data encryption and image processing applications. This type of architecture is not optimized for word-width data manipulation since a large area of the chip will be lost for routing signals. Coarse-grained architectures such as PADDI-2 [8], PipeRench [9], Morphosys [10], Grap [11], and Colt [12] are designed to implement word-width (or larger) data paths. Because the processing elements are optimized for large computations, they perform such operations efficiently in terms of time and area. The authors of [5], [13], [14], [15], and [16] presented a comprehensive survey of available reconfigurable computing platforms in the academic and commercial. In [13] and [15] reconfigurable platforms were presented in more detail. The best references for each platform were given. However, some of the information on these architectures is either incomplete or not disclosed. The most known architectures are presented here.

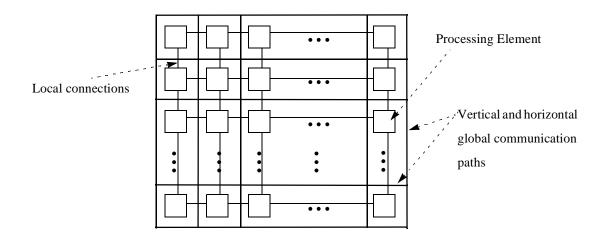

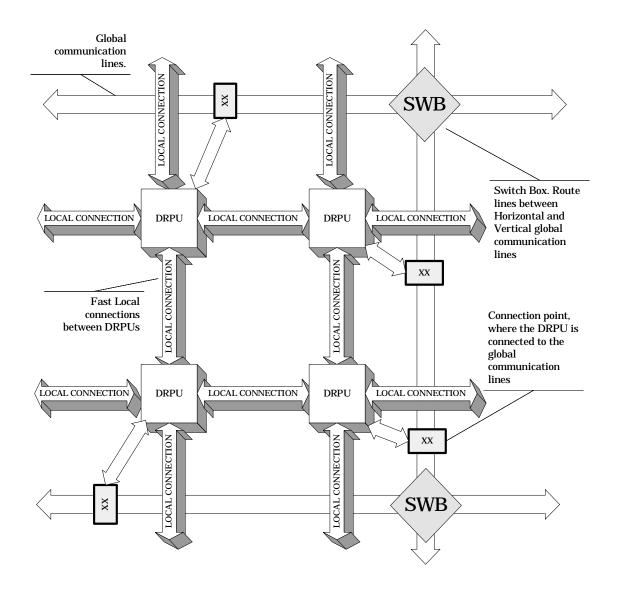

Most of the architectures reported in the literature are mesh-based architectures. Figure 1-2 shows a general-block model of the mesh-based reconfigurable architectures. As their name implies, mesh-based architectures are a two dimensional arrangement of processing elements. Local connections are placed between the nearest four or eight neighbors. Additionally, vertical and horizontal communication paths are placed between the processing elements. Such an arrangement is suitable for stream-based applications or any application that requires simple

**Figure 1-2:** A block model of the mesh-based reconfigurable architectures with local connection to the nearest four neighbors

and regular computations. Examples of mesh-based reconfigurable architectures are KressArray [17], Colt [12], and Morphosys [10] and [18].

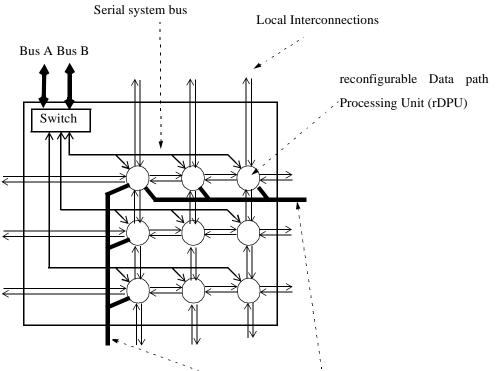

KressArray is a generalization of systolic array. It is a two dimensional array of 32-bit processing elements called reconfigurable Data Processing Units (rDPUs). The rDPU is designed to support all arithmetic operations of the C language. The rDPU is data triggered, i.e. rDPU performs the configured operation once the data is received [17]. Additionally, the rDPU includes a register file that can be used to store the input or output data. This register file enables the KressArray to perform deep pipelined execution of an application.

In KressArray the local connection of the rDPUs at the border of the chip are connected to I/O pins. This type of connections enables KressArry to be extendable, i.e. it can be connected to other KressArry chips to create even larger arrays of rDPUs. As shown in Figure 1-3[17] routing in KressArray is hierarchically divided into three levels. On the lowest level, a local connection to the nearest north, west, east, and south neighbor is implemented. On the second level, full length inner global buses that connect any two rDPU on the same row or same column is implemented. These buses can be segmented to form more than one bus. The third level of routing is provided by a serial system bus. The system bus is also used to transfer configuration bits to the rDPUs.

KressArray is designed for general use and was not designed for specific application. This is the reason that the rDPU is designed to be able to execute all C language operators. However, a specific application may not require all of the C language operations, resulting in a waste of area. KressArray supports partial

Inner global buses. Only one vertical and one horizontal are shown.

Figure 1-3: 3x3 segment of KressArray architectural structure

dynamic reconfiguration. However, no applications have yet been found to take advantage of such features [13].

The use of buses in the system and the use of one bus per row to transport the configuration data may be a limiting factor of the reconfiguration speed. As the number of rDPUs increases, the number of rDPUs per bus increases making the reconfiguration time even longer.

The Colt architecture is a product of work done by the Mobile and Portable Radio Research Group at Virginia Tech. The Colt integrated circuit is designed as

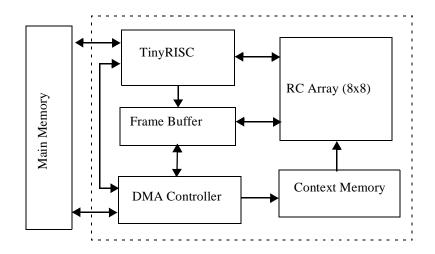

Figure 1-4: Morphosys architecture components

a prototype: the so called Wormhole Run Time Reconfiguration, and it is optimized for DSP-type operations [12].

Morphosys is a parallel reconfigurable SoC designed to speed up general purpose intensive applications. Usually these applications inherent parallelism and are highly regular. It is a combination of a RISC processor with an array of coarse-grain reconfigurable cells [10]. As shown in Figure 1-4 [10], the Morphosys architecture consists of a two dimensional array of reconfigurable cells, called a Reconfigurable Cell Array (RC Array); combined with a RISC control processor called TinyRISC; Context Memory; Frame Buffer; a DMA Controller, and a memory interface.

The TinyRISC processor is a MIPS-like processor. It has a 32-bit ALU, register file and an on-chip data cache memory. The processor is included in the system for controlling the execution of the operations and to control the main memory interface. For this purpose additional instructions which are specific to Morphosys have been added to the standard RISC instruction set.

The reconfigurable component is an array of 64 processing elements. The number of the processing elements in the array and the way they are arranged is influenced by one of the target applications: the image processing. Image processing applications tend to process the data in 8x8 segments [18]. Thus an RC array is arranged in a two dimensional array of 8x8 elements.

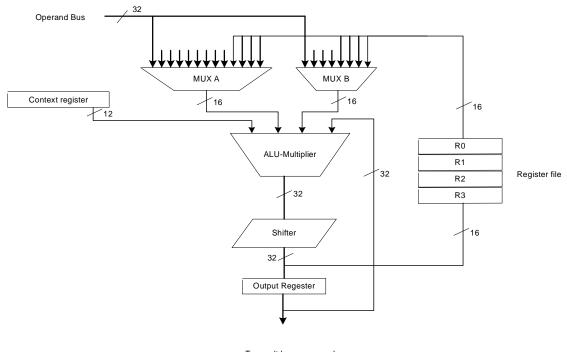

The reconfigurable cell of the Morphosys system is shown in Figure 1-5 [10]. The RC incorporates an ALU-multiplier unit, a shifter unit, input multiplexers

To result bus , express lanes, and other RC

and a register file. The multiplier is included since many target applications require integer multiplication. The multiplier unit can perform integer multiplication and accumulation in one cycle. The multiplexers can select inputs from other RCs, from the operand bus, or from the internal register file.

The processing elements of the array are grouped either row-wise or column-wise for configuration. This reduces the number of configuration context of the array from sixty four to eight. In addition, this grouping of RC implies a SIMD computation model. The routing of the RC array consists of three layers, four nearest neighbor local connections, segments of the distance of two connections, and long global connections.

Morphosys is an efficient implementation system for specific applications, such as image processing or data encryption [10] and [18]. However, the SIMD computation model of the RC array limits the Morphosys from being able to efficiently implement other applications that do not inhabit block size data input or do not require regular execution styles. Additionally, the RC units of the array are very-coarse-grained (32-bit). This leads to few RC units in the array, and a waste of the resources (area) when implementing smaller data paths of 16-bit or less.

Examples of other reconfigurable computing engines that do not follow the two dimensional array topology are: The Pleiades (Ultra-Low-Power Hybrid and Configurable Computing) project at the University of California, Berkeley. This engine is designed to provide low power consumption coupled with high-performance for multimedia computing applications [19] and [20]. Pleiades is a crossbarbased architecture. The PipeRench architecture (Carnegie Mellon University) [9] is a reconfigurable fabric of processing elements for general purpose applications. The PipeRench is specifically designed to speed up the reconfiguration process through a new technique called pipeline reconfiguration. Pipeline reconfiguration allows one stage of the pipeline path to be configured in every cycle, while concurrently executing all other stages.

Finally, the Grap architecture (University of California, Berkeley) [11] is tailored toward accelerating loops for general purpose computations.

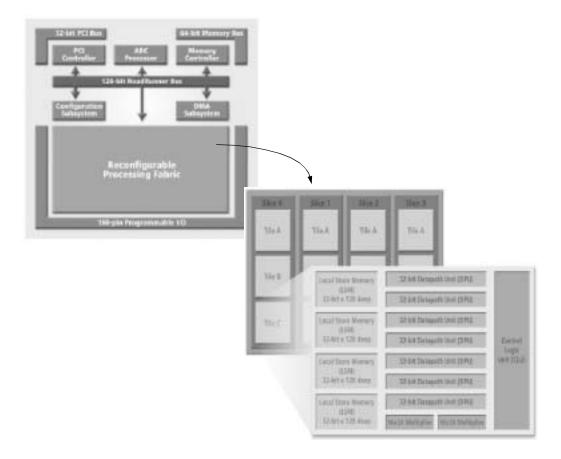

All of the above mentioned architectures are being developed in the academia. Commercial solutions for tele-communication and wireless applications are being developed by Chameleon Systems [21], and MorphICs [22]. Chameleon Systems [23] announced the CS2000 family of multi-protocol multi-application reconfigurable platforms for tele-communication and data communication. Figure 1-6 [21] shows a block diagram of the SC2000 family. The CS2000 family incorporates a 32-bit RISC core, full memory controller, PCI controller, and a reconfigurable array. The reconfigurable array sizes come in 6, 9, and 12 tiles. The tile consists of seven 32-bit processing elements, four local memories of 128x32 bits, and two 16x24-bit multipliers. Every three tiles are grouped as a slice. Dynamic configuration is supported and can be accomplished in one cycle.

Although MorphICs announced its own version of reconfigurable chips targeting the next generation of wireless application, it never disclosed any information about the inner design of its solution.

Chameleon CS2000 can be considered as a general solution for the wireless application. However, it was not meant to be an implementation solution for the

Figure 1-6: Chameleon CS2000 Reconfigurable Communications Processor and Reconfigurable Processing Fabric (RPF)

baseband processing of the handheld terminals. The CS2000 family's very sophisticated and in-homogenous array makes an IP-based mapping difficult.

Based upon all of the published work, no architecture was designed specifically for the wireless application. Additionally, general architecture that could perform well for all applications is very hard (if not impossible) to be designed [24]. Therefore, tailored architectures for different areas of application are a must. Presently, no formal methods or guidelines have been devised for a reconfigurable architecture design and specifically no methods exist for mobile communication. Today mobile communication applications are of critical importance. Therefore, it is important to develop models and rules to design the reconfigurable architectures for these applications.

#### 1.3 Project Goals and Objectives

The goal of this dissertation is to develop an array of coarse-grained Dynamically Reconfigurable Processing Units (DRPUs), which are internally connected with optimized and reconfigurable communication structures. The architecture provides efficient and fast dynamic reconfiguration possibilities (e.g., only partial and during run-time) while other parts of the reconfigurable architecture are active [25] and [26].

The choice of implementing algorithms depends upon the design of the hardware flexibility, speed, and power consumption requirements. Traditionally, algorithms that handle chip-rate signal processing (3.84M chip-per-second over sampled 4 or 8 times) are implemented on an ASIC. Whereas algorithms that handle symbol-rate signal processing (maximum of 2M samples-per-second) are implemented on a DSP. An ASIC generally runs faster and consumes less power when compared with the general purpose Digital Signal Processor DSP [27]. The developed architecture is to be able to handle both signal rates with performance and power consumption equivalent to or better than dedicated ASIC or DSP devices.

Modern communication systems operate with fixed, detailed execution formats that impose frequent deadlines. As a result, it is essential to know the execution times of various signal-processing algorithms. This is difficult with generalpurpose processors, because they manipulate the flow of data and the instruction sequence to balance loading. Therefore, the reconfigurable computing architecture must provide hard timing limits for well-known execution times of intended functions [28].

The primary objective of this work is to design and simulate a new architecture for the mobile station for third generation (3G) systems. The design and simulation will be based on the principles and methods of Dynamically Reconfigurable Computing. The design of such architecture will cover broad disciplines. A low power design, hardware/software codesign, reconfigurable computing simulation, and computer programming are a few examples of these disciplines.

The design processes incorporate new design algorithms specially developed for third generation mobile systems. Such algorithms will be adaptable to channel changes, will be efficient, and will take advantage of the dynamic and parallel nature of the architecture. The final system will provide a better solution for mobile stations. The system will reflect the low cost requirement of the future systems and at the same time it will combine low power consumption with a powerful performance. Another important goal of this work is to develop the bases of a set of methods and rules for designing reconfigurable architectures for a specific area of applications.

#### 1.4 Dissertation Outline

This dissertation is organized as follows: Chapter 2 introduces the up coming third and future generation mobile systems in general. Chapter 3 examines some of the most demanding applications at the receiver baseband processing of the mobile terminal. Chapter 4 discusses different platforms available for the targeted application and compares their pros and cons. A more detailed discussion about the dynamically reconfigurable architectures is presented in depth in this chapter. Chapter 5 introduces the Dynamically Reconfigurable Architecture for future generation Wireless mobile systems (DRAW). An abstract planar model of the architecture and a detailed description of the new features and aspects of the architecture are also presented in Chapter 5. Chapter 6 presents the design flow of the DRAW architecture. Many new concepts that emerge from the design of DRAW are also introduced and discussed. The architecture is composed of an array of processing elements dubbed DRPUs and dynamically reconfigurable communication resources. In order to demonstrate the new concepts introduced through DRAW, two applications an FIR filter and a Gold code generator were mapped into DRAW. Along with a discussion of the mapping process, simulation results are presented in Chapter 7. Chapter 8 provides a general conclusion and recommendations for future research in this area.

### Chapter 2

# Third and Future Generations Mobile Systems

### 2.1 Introduction

This chapter briefly presents the new evolving Wideband Code Division Multiple Accesses (WCDMA). Presently this is a standard of the third generation mobile systems developed by the third-generation partnership project (3GPP). 3GPP was established to harmonize and standardize many similar proposals from different parts of the world [29]. In addition, a brief look at the future wireless communication systems will be provided.

#### 2.2 Overview of the Third Generation Systems

The first generation mobile systems in the 1970s were based on analog transmission schemes. They supported only the voice service. The second generation mobile systems in the 1980s were based on digital transmission scheme. The second generation was designed for circuit switched services. In addition to voice service, the second generation mobile systems supported low to medium packet based services. Third generation systems are designed for both circuit switched and packet based services. They will provide very high data rates that enable many new and interesting services [30], [31], [32], and [33]. Table 2-1 [34] lists the different mobile cellular radio systems, the services they offer, and their maximum data rates [34].

| Mobile Generation    | Services                                                      | Data rate                         |

|----------------------|---------------------------------------------------------------|-----------------------------------|

| Old (1G)             | Voice                                                         | 13.3 kbps                         |

| Current systems (2G) | Voice, Text, Static<br>Images, Data                           | 9.6 - 41.4 Kbps                   |

| Emerging (2.5G)      | Web based connection<br>and Blue tooth                        | 115 Kbps,<br>Blue tooth 721 Kbps. |

| 3G                   | Entertainment<br>Education<br>MP3<br>MPEG4<br>Games<br>Videos | Up to 2 Mbps                      |

Table 2-1. A list of different wireless mobile generations

The International Mobile Tele-communication 2000 (IMT-2000) is a family of systems for the third generation mobile telecommunications. This family of systems will provide wireless access any time and any where. IMT-2000 is one of the most exciting developments in mobile communication since the introduction of digital mobile systems in the early 1990s. IMT-2000 is developed by the International Telecommunication Union (ITU) [30]. The third generation systems are required to fulfill many objectives, the most important goals are high speed data services, flexibility, compatibility, and low cost. High data rate services are also known as broadband services. Current examples of an application that utilizes such services are high speed internet access and multimedia type applications. A flexible wireless mobile system is one that can easily support new services after the system has been deployed. As would be expected, once the system is full and running, new services that are presently beyond one's imagination will be demanded by the end user. A successful system must be able to accommodate these future services. Backward compatibility with second generation systems is a vital requirement for the success of the system. In addition to all the new high data rates services that are provided by the third generation system, the cost for the end user must be kept as it is today if not reduced [30], [31], and [35].

Third-generation mobile radio systems have been under intense research and discussion and will emerge around the end of 2002. The system is called the International Mobile Telecommunications-2000 in the International Telecommunications Union. Whereas in Europe, the system is called the Universal Mobile Telecommunications System (UMTS) [32]. The standardization process was long and went through many disputes, discussions, and harmonization. Toward the end of 1998 two new organizations were established: the 3rd Generation Partnership Project (3GPP) and 3GPP2. The goal of 3GPP and also 3GPP2 was to harmonize the large number of the WCDMA based proposals submitted by different bodies into one system [29], and [36]. Table 2-1 lists some of the proposed standards for the third generation mobile system to the ITU. Both the UTRA developed by 3GPP and cdma2000 developed by 3GPP2 are based on WCDMA technology. Since the UTRA was developed earlier than the cdma2000, this dissertation was developed around the WCDMA specification published by 3GPP [29], [37], [38], [39], [40], [41], and [42]. Table 2-2 [45] lists the main parameters of WCDMA [46], and [66].

| Proposal    | Description                                                 | Source            |

|-------------|-------------------------------------------------------------|-------------------|

| DECT        | Digital Enhanced Cordless<br>Telecommunications             | ETSI Project DECT |

| UWC-136     | Universal Wireless Communications                           | USA TIA TR45.3    |

| WIMS W-CDMA | Wireless Multimedia and Messaging<br>Services Wideband CDMA | USA TIA TR46.1    |

| TD-SCDMA    | Time-division synchronous CDMA                              | China CATT        |

| W-CDMA      | Wideband CDMA                                               | Japan ARIB        |

| CDMA II     | Asynchronous DS-CDMA                                        | S. Korea TTA      |

| UTRA        | UMTS Terrestrial Radio Access                               | ETSI SMG2         |

| NA: W-CDMA  | North American: Wideband CDMA                               | USA T1P1-ATIS     |

| cdma2000    | Wideband CDMA (IS-95)                                       | USA TIA TR45.5    |

| CDMA I      | Multi band synchronous DS-CDMA                              | S. Korea TTA      |

Table 2-2.

Radio transmission technology proposals for IMT-2000

#### 2.2.1 Characteristics of UTRA (WCDMA)

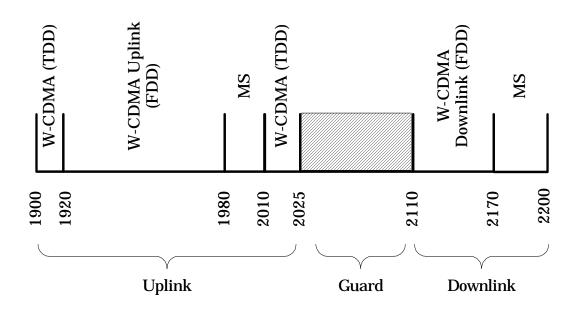

The WCDMA standard has two modes for the duplex method. A Frequency Division Duplex (FDD) and Time Division Duplex (TDD). The frequency bands allocated for UTRA are shown in Figure 2-1 [35]. In UTRA there is one paired fre-

Figure 2-1: The frequency spectrum allocations for UTRA

quency band in the range 1920 –1980 MHz and 2110 –2170 MHz to be used for UTRA FDD. There are two unpaired bands from 1900 –1920 MHz and 2010 – 2025 MHz intended for the operation of UTRA TDD [31].

At the time when this work was developed, only the standard of the FDD mode developed by ITU were at an advanced stage of standardization. The TDD mode standard started later. For this reason this work assumes the FDD mode of operation for the receiver. Table 2-3 [45] lists the most important parameters of the UTRA FDD.

As can be seen in Table 2-3, the chip rate for the WCDMA standard is 3.84 Mcps [37], and [38]. Spreading consists of two operations. The first operation is the channelization operation where the spreading code is applied to every symbol in the transmitted data. Thus the bandwidth of the data signal is increased. In this

| Channel bandwidth                   | 5 MHz                                                                                                                         |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Duplex mode                         | FDD and TDD                                                                                                                   |

| Downlink RF channel                 | Direct Spread                                                                                                                 |

| Chip rate                           | 3.84 Mcps                                                                                                                     |

| Frame length                        | 10 ms                                                                                                                         |

| Spreading modulation                | Balanced QPSK (downlink) Dual-channel<br>QPSK (uplink) Complex spreading circuit                                              |

| Data modulation                     | QPSK (downlink) BPSK (uplink)                                                                                                 |

| Channel coding                      | Convolutional and turbo codes                                                                                                 |

| Coherent detection                  | User dedicated time multiplexed pilot<br>(downlink and uplink), common pilot in the<br>downlink                               |

| Channel multiplexing in<br>downlink | Data and control channels time multiplexed                                                                                    |

| Channel multiplexing in uplink      | Control and pilot channel time multiplexed<br>I&Q multiplexing for data and control<br>channel                                |

| Multirate                           | Variable spreading and multi-code                                                                                             |

| Spreading factors                   | 4–256 (uplink), 4–512 (downlink)                                                                                              |

| Power control                       | Open and fast closed loop (1.6 KHz)                                                                                           |

| Spreading (downlink)                | OVSF sequences for channel separation<br>Gold sequences 218-1 for cell and user<br>separation (truncated cycle 10 ms)         |

| Spreading (uplink)                  | OVSF sequences, Gold sequence 241 for user<br>separation (different time shifts in I and Q<br>channel, truncated cycle 10 ms) |

| Handover                            | Soft handover<br>Interfrequency handover                                                                                      |

channelization operation, the number of chips per data symbol is called the Spreading Factor (SF). The second spreading operation is the scrambling operation, where a scrambling code is applied to the already spreaded signal. Both of the spreading operations are applied to the so called In-phase (I) and Quadraturephase (Q) branches of the data signal. In the channelization operation, the Orthogonal Variable Spreading Factor (OVSF) codes are independently applied to the I and Q branches [37], and [39]. The resultant signals on the I and Q branches are then multiplied by a complex-valued scrambling code, where I and Q correspond to the real and imaginary parts respectively.

For the channel coding, the standard suggests three options of coding for different Quality-of-Services (QoS) requirements [40]. The three coding options are: Convolutional coding, Turbo coding, or no coding. The selection of one of the three options is done by the upper layers. In addition, bit interleaving is used to improve the Bit Error Rate (BER). The modulation scheme selected in 3GPP WCDMA standard is QPSK [37].

An important characteristic of the WCDMA system is that it is an asynchronous system, i. e. there is no global synchronization between base stations in the system. This means that each user can transmit independently of other users or base stations transmissions [35]. This eliminates the need for global clock similar to the IS-95 system proposed by the USA. IS-95 uses the Global Positioning System (GPS) clock as a global clock for synchronization between base stations.

Since this dissertation deals with the baseband of the mobile terminal's receiver, I will only explain the structure of the downlink. The downlink is the communication path from the base station to the mobile terminal. The physical chan-

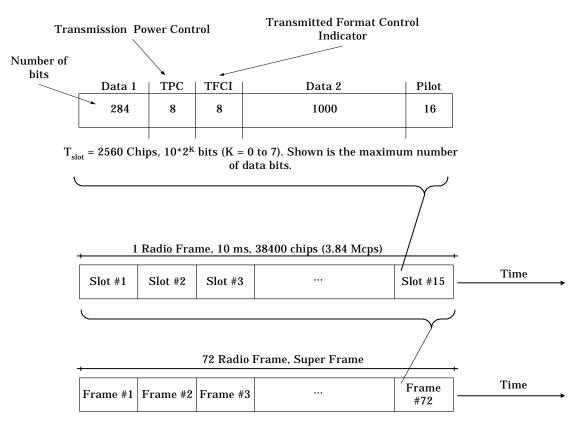

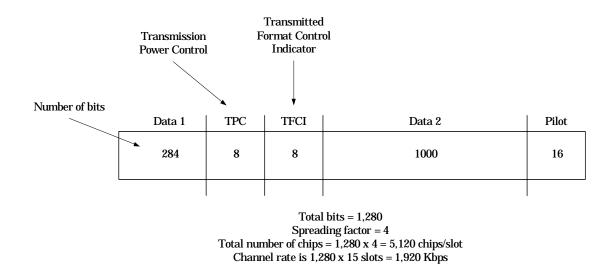

Figure 2-2: The radio frame structure downlink DPCH of the WCDMA

nels of the WCDMA systems are structured in layers of radio frames and time slots. There is only one type of downlink dedicated physical channel, the downlink Dedicated Physical CHannel (downlink-DPCH) [39]. The structure layout of the downlink dedicated physical channel (DPCH) of the WCDMA signal can be seen in Figure 2-2 [39]. As shown in the Figure, the time line of the signal is divided into frames of 10 ms each. Each frame is then divided into 15 slots, i.e. 2560 chips/slot at the chip rate of 3.84 Mcps. In addition, every 72 frames constitute one super frame. The frame is a time multiplexed data and control bits from the Dedicated Physical Data Channel (DPDCH) and Dedicated Physical Control Channel (DPCCH)<sup>1</sup>. The DATA 1 and DATA 2 are data bits that belong to DPDCH, while bits of Transmit Power Control (TPC), Transport Format Combination Indicator (TFCI), and Pilot belongs to the DPCCH. The number of bits in each field vary with the channel bit rate. The exact number of bits in each field is shown in [40]. The TPC bits are used by the base station to command the mobile transceiver to increase or decrease the transmission power. TFCI bits are the indicators of slot format.

The bit count shown in Figure 2-2 is the maximum possible number of data bits that can be transmitted in one slot. In a frame  $15 \times 10 \times 2^k$  bits can be transmitted in every slot, where k is an integer in the range from 0 to 7. The parameter k is related to the Spreading Factor (SF):

$$SF = \frac{512}{2^k}$$

**2-1.**

Thus the spreading factor SF may range from 512 down to 4 see [41], and [42].

#### 2.3 Characteristics of cdma2000 system

The cdma2000 is a wideband spread spectrum radio interface standard developed by the Telecommunications Industry Association (TIA) of the USA. The cdma2000 meets all the requirements set by the ITU for the IMT-2000. The second generation CDMA standard developed by the TIA is called IS-95. The latest version of this standard is IS-95B. Since IS-95 based systems are deployed mainly in

<sup>1.</sup> Abbreviations used here are the standard abbreviations used by 3GPP in the 3G-TS technical documents.

USA and in some countries around the world, the cdma2000 system is designed to be back compatible with IS-95. The backward compatibility feature of the cdma2000 (with the second generation system IS-95) reduces the cost of deploying cdma2000 by reusing the infrastructure of the IS-95. This will also insure a smooth and successful migration from 2G to 3G system [43] and [44].

The cdma2000 radio access is based on narrowband DS-CDMA with a chip rate of 3.6864 Mcps. This chip rate is three times the chip rate of the IS-95 system which is 1.2288 Mcps. The cdma2000 standard also supports higher data rates of N\*1.2288 Mcps, where N is 1,3,6,9, and 12. Similar to UTRA, cdma2000 also supports FDD and TDD mode of operations.[35]

Table 2-4 lists some of the main parameters of the cdma2000 standard. The most noticeable departure from UTRA standard is the base station synchronization and the frame length. In cdma2000, the base station uses the GPS time as a reference timing for the shift in the cell scrambling code. This feature simplifies the cell search since only one code with different shifts are used to identify all cells in the system. The frame length is two times the frame length of the UTRA/WCDMA system.

#### 2.4 Future Generation Mobile Systems

The introduction of the third generation mobile system next year will revolutionize the world as we know it. The impact of the system on our lives is every thing but predictable. Despite this fact, forth and fifth generations are already

| Channel bandwidth            | 5 MHz                                                                                                   |

|------------------------------|---------------------------------------------------------------------------------------------------------|

| Base station synchronization | Asynchronous, GPS time reference                                                                        |

| Duplex mode                  | FDD and TDD                                                                                             |

| Downlink RF channel          | Multicarrier Spreading and Direct Spread                                                                |

| Chip rate                    | 3.6864 Mcps                                                                                             |

| Frame length                 | 20 ms                                                                                                   |

| Modulation                   | QPSK (downlink), and Hybrid Phase Shift<br>Keying HPSK (uplink)                                         |

| Channel coding               | Convolutional and turbo codes                                                                           |

| Coherent detection           | Pilot time multiplexed PC (uplink), Common<br>continues pilot channel and auxiliary pilot<br>(downlink) |

| Multirate                    | Variable spreading and multi-code                                                                       |

| Spreading factors            | 4–256 (uplink)                                                                                          |

| Spreading codes              | Walsh code<br>Pseudo noise code                                                                         |

| Power control                | Open and closed loop                                                                                    |

| Handover                     | Soft handover<br>Interfrequency handover                                                                |

Table 2-4. Standardized Parameters of cdma2000

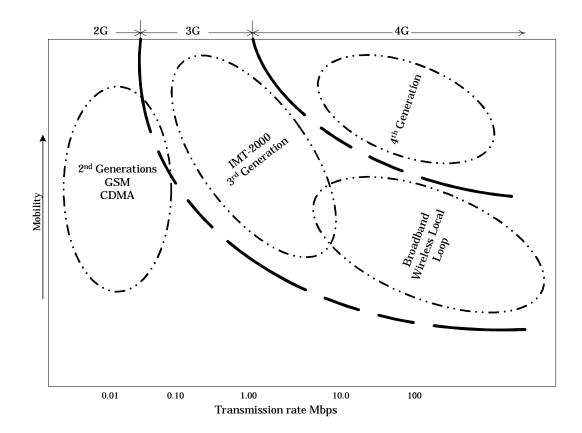

being discussed. Figure 2-3 [34] outlines some of the current, emerging, and future mobile systems along with their supported data rates [34].

The term fourth generation is used to include several systems not only cellular systems, as well as many wireless communication systems [47], and [34]. It is well expected that the future systems will provide very high data rates in the tens and even hundreds of MB/S. It is even expected that these extremely high data rates will be provided with full mobility support. However, it is very hard to envision these systems beyond these two expectations. It is very difficult to implement such systems with such high data rate and mobility [34].

**Figure 2-3:** Current and future generations of wireless mobile systems vs. their transmission rates

## Chapter 3

# WCDMA Baseband Signal Processing

### 3.1 Introduction

This chapter examines the most demanding functions in the 3G baseband processing unit. The computation requirements which are the basis for the design of the reconfigurable architecture are determined. To design a good reconfigurable architecture for a specific application, some understanding of the most demanding functions of the baseband receiver are required. The target application must be well understood in terms of its:

- Performance requirements

- Routing behavior

- Input/Output requirements

- Memory requirements

The performance requirements of the target application are the first general characteristics that must be known and understood for the designer prior to designing the architecture. This requires determining rough answers to the following questions: 1) Is this a real time application or not? 2) What is the required execution time? 3) What are the required operations? 4) What are the data path width requirements? 5) What is the required throughput? 6) Is this a regular or irregular execution flow?

For routing we would like to know how different blocks of the applications are connected, i.e. is the algorithm locally or globally connected? How frequently the target application do use the routing channels? We also need to know the appropriate path-width for the routing channels of this application.

I/O requirements are usually the bottleneck of most applications. Therefore, it is very important to know in detail the required number of inputs and outputs. Simultaneously, we also need to know what are the surrounding interfaces that need to be addressed.

As important as the performance requirement is, the memory requirements also play an important role in directing the final design of the architecture. The knowledge necessary regarding memory requirements includes the type of memory that is required, and is it a one-port, dual-ports, or FIFO type of storage system? We also need to ascertain how large the required memory must be.

#### 3.2 WCDMA Baseband Mobile Receiver

The work in this dissertation considers the Frequency Division Duplex (FDD) of the 3GPP WCDMA as a standard. In this section, I will examine the mobile baseband processing unit of the receiver. The reason behind selecting the

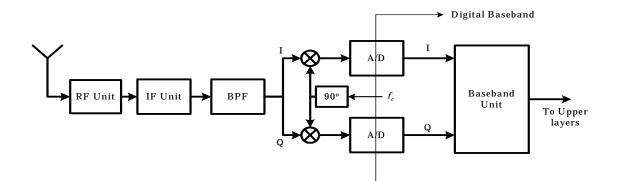

Figure 3-1: A block diagram of 3G receiver

receiver's baseband processing unit to perform the analysis rather than selecting the transmitter, is that the receiver is usually more complex and requires more processing power than the transmitter baseband unit. This is due to the fact that the receiver deals with signals that contain high levels of noise because of the nature of the channel. The mobile channel is a dynamic one, this behavior gets aggravated for communication at higher data rates and worsens when communicating with a moving mobile terminal at higher speeds. [48], [49], and [50]

Figure 3-1 outlines the block diagram of the complete receiver [51]. As can be seen in the figure, after the signal has been received by the radio frequency unit with a frequency in the range of 2110-2170 MHz, the signal is then down converted to an Intermediate Frequency (IF) level of 270 MHz. The desired 5MHz channel is filtered by an IF band-pass filter. The IF signal is fed to the demodulator circuit where it is mixed with the fixed local oscillator frequency to produce the zero IF baseband in-phase and quadrature (I and Q) signals, these are then fed to the

Figure 3-2: The baseband receiver front-end

analog-to-digital converter. The output of the A/D converter is then fed to the baseband unit for processing [30], and [33].

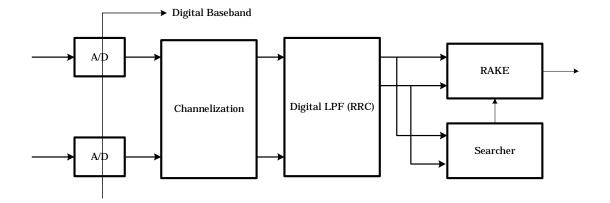

Figure 3-2 shows the block model of the receiver's baseband processing unit. The Figure shows more detail of the inner signal path in the front end of the baseband receiver. The analog signal is converted into a digital signal using wideband analogue to digital converter typically running at 8 times the chip rate and producing 8 bit resolution [35]. The signal is then filtered using a Root Raised Cosine (RRC) filter with a roll-off factor of 0.22. The purpose of the root raised cosine filter is to reduce the inter-symbol interference. Subsequently the signal is fed to the RAKE receiver and to the searcher.

Figure 3-3, shows a block diagram of the additional processing steps at the baseband of the WCDMA receiver. As shown in the figure, the incoming chips from the A/D converter are introduced to the RAKE receiver and to the searcher. The

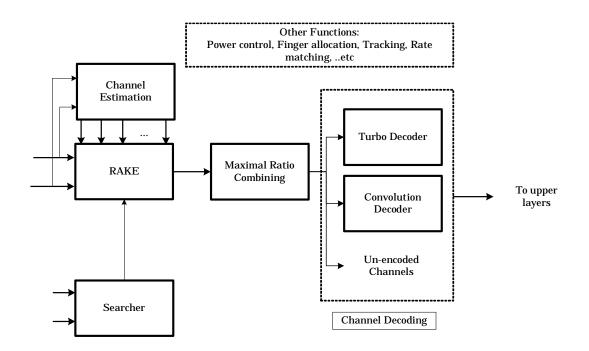

Figure 3-3: Complete block diagram of the receiver front end

searcher provides an estimation of the multipaths delays which are used by the RAKE receiver to resolve different paths signals. The maximal ratio combiner then weights the signals and sums them together [52]. In addition, the searcher provides signals for the Automatic Gain Controller (AGC), Automatic Frequency Controller (AFC), and Power Control Loop (PCL) (not shown in figure). Depending upon which signal quality is chosen, the signal is then routed to a Turbo coder, Convolutional decoder, or pass-over the decoding unit completely as in the case of un-coded channels. The selection of the type of decoding depends upon the quality of service required. Additional processing is then performed by the channel processing unit. Such additional operations may include viterbi decoding, de-interleaving, reed Solomon decoding etc. [40].

#### 3.3 Baseband Signal Processing Requirements

Baseband signal processing in a system based on WCDMA is so complex due to the fact that a wide variety of services are offered. Services such as high-quality voice and high-quality videos are provided through high data-rate wireless channels [53]. At the same time the hand-held mobile terminal is expected to be similar to the 2nd generation mobile terminals in terms of cost, power consumption and size. In addition, the mobile terminal solution must accommodate the changes in the standard as the standard solidifies, and also accommodate other 3rd generation systems such as cdma2000. The mobile terminal solution must also be flexible and have the capacity to implement any new services envisioned in the future many of which are not fully yet understood [51]. When 3G systems come to market, first and second generation systems will be still widely used. Thus 3G mobile terminals must have a backward compatibility with previous wireless mobile systems.

Currently, there are two primary hardware realizations for the baseband processing in the 3G mobile terminal, ASIC, and Digital Signal Processor. A comparison of the two solutions' strengths and weaknesses will be fully explored.

According to J. Rabay [64] high signal processing demands of the baseband processing unit in the 3G mobile terminal are mostly concentrated in five sub-functions of the baseband. As seen in Table 3-1 the five functions are:

- Digital FIR filtering

- Searchers (frame, slot, delay path, etc.)

- RAKE reception

- Maximal Ratio Combining

- Turbo Decoding

| Function                                 | Number of Million Instructions per Second<br>(MIPS) @ 384 Kbps |

|------------------------------------------|----------------------------------------------------------------|

| Digital Filters (RRC, Channelization)    | ~3600 MIPS                                                     |

| Searcher (Frame, slot, delay path, etc.) | ~1500                                                          |

| RAKE Receiver                            | ~650                                                           |

| Turbo coding                             | ~52                                                            |

| Maximal Ratio Combiner (MRC)             | ~24                                                            |

| Channel estimation                       | ~12                                                            |

| AGC, AFC                                 | ~10                                                            |

| De-interleaving, rate matching           | ~14                                                            |

| TOTAL                                    | ~5860                                                          |

Table 3-1. Estimation of signal processing load for 3G baseband @ 384 kbps

By speeding up the execution of these functions, an overall speed-up of the baseband processing will be obtained. Each one of these functions will be discussed in detail.

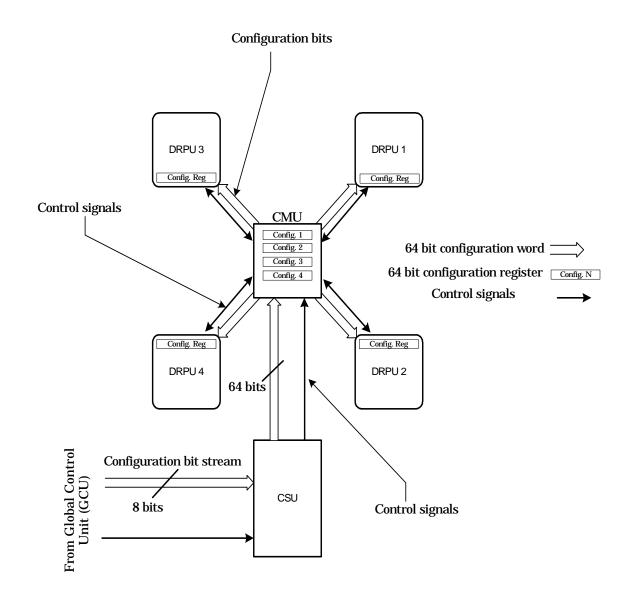

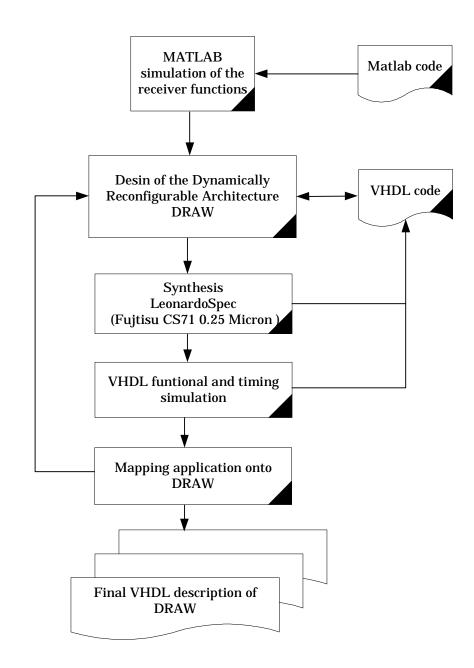

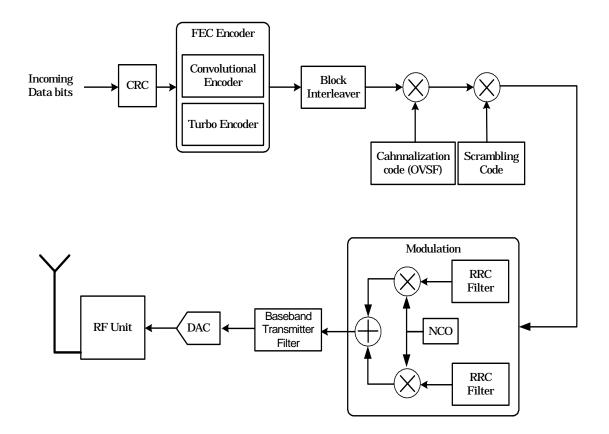

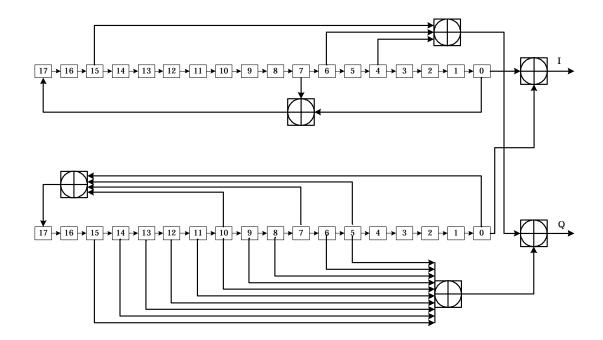

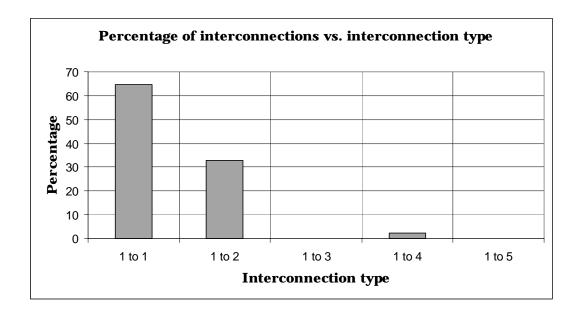

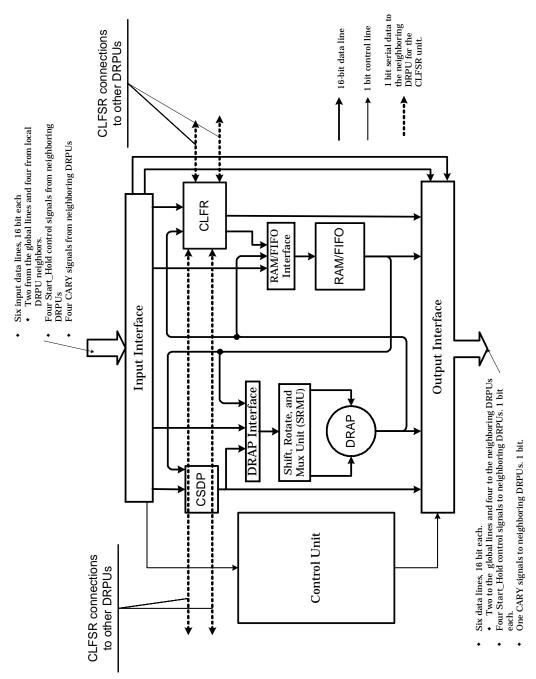

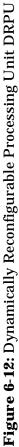

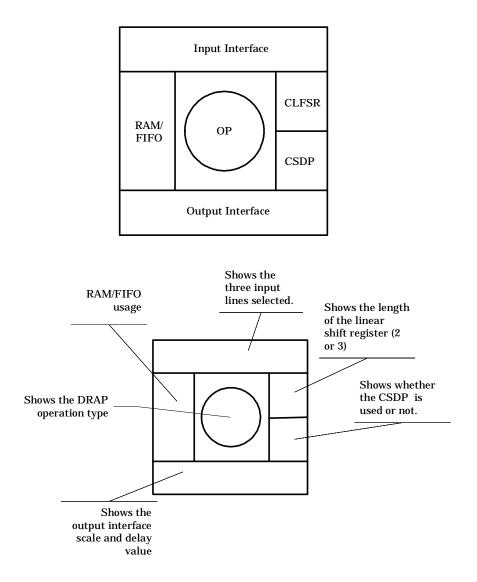

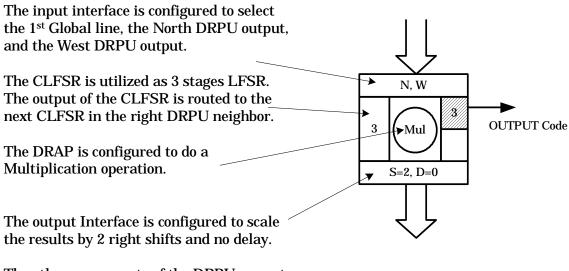

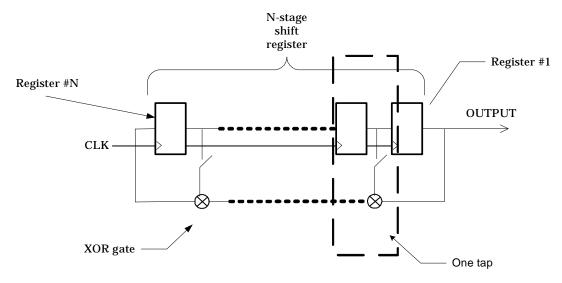

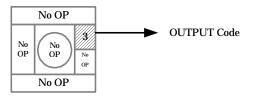

The implementation of the baseband unit on a reconfigurable hardware can benefit from the fact that each part of the baseband unit performs a set of fixed operations on a block of data. The block of data can be one frame data or one slot data. As a result, if the hardware can perform all the required operations before a new block of data arrives then, one can configure the different parts of the baseband unit on the reconfigurable hardware sequentially. In addition, if the hardware is capable of executing all the operations fast enough, then it can be turned off to save power until the new block of data arrives [50], and [55]. The selection of the size of the data block affects the final performance in different ways. For example, setting the block size to a small size like the data in one Slot (0.66 ms), will reduce the area for storing the incoming data and reduce the area of the executing hardware of each part of the baseband unit.