### DIRECT GLOBAL POSITIONING SYSTEM P-CODE ACQUISITION FIELD PROGRAMMABLE GATE ARRAY PROTOTYPING

A Dissertation Presented to the Faculty of the Fritz J. and Dolores H. Russ College of Engineering and Technology Ohio University

> In Partial Fulfillment of the Requirement for the Degree Doctor of Philosophy

> > by

Jing Pang

August, 2003

#### THIS DISSERTATION ENTITLED

## **"DIRECT GLOBAL POSITIONING SYSTEM P-CODE ACQUISITION FIELD PROGRAMMABLE GATE ARRAY PROTOTYPING"**

by Jing Pang

has been approved

for the School of Electrical Engineering and Computer Science and the Russ College of Engineering and Technology

Janusz Starzyk, Professor School of Electrical Engineering and Computer Science

> Dennis Irwin, Dean Fritz J. and Dolores H. Russ College of Engineering and Technology

### ACKOWLEDGEMENTS

First of all, I would like to express my gratitude to my advisor, Dr. Janusz Starzyk, for his support, patience, encouragement throughout my graduate studies, and his invaluable advice during the whole work with this dissertation. He also has taught me innumerable lessons and insights on the workings of academic research in general.

Special thanks to Dr. Frank Van Graas, for his financial support of my graduate study, his inspiring and encouraging way to guide me to a deeper understanding of GPS research.

I would like to thank the rest of my dissertation committee: Dr. Chris G. Bartone offered much-appreciated advice to start this dissertation research work. Dr. Robert Curtis helped me on electronics when I worked on interfacing FPGA with other hardware. Dr. Surender Jain spent his valuable time to attend my presentation, read my dissertation draft, and gave valuable comments.

I am very grateful to all students in VLSI and software radio research groups. I appreciate all their friendships and their collective encouragement to finish this dissertation. I specially thank Abdulqadir A. Alaqeeli and Sanjeev Gunawardena for sharing their technical wisdom and research ideas.

Furthermore, I would like to acknowledge the rich blessings of my sister, and my parents. Their love is instrumental for me to complete this dissertation.

# TABLE OF CONTENTS

| Ackr    | nowledgeme   | ent                        | iii  |

|---------|--------------|----------------------------|------|

| Table   | e of Content | ts                         | iv   |

| List    | of Tables    |                            | viii |

| List    | of Figures   |                            | X    |

| List    | of Abbrevia  | tions                      | XV   |

|         |              |                            |      |

| Chapter | 1            |                            | 1    |

| Intro   | duction      |                            | 1    |

| ~1      |              |                            |      |

| Chapter | 2            |                            | 9    |

| GPS     | Background   | d                          | 9    |

| 2.      | 1 GPS Si     | gnal Structure             | 9    |

| 2.      | 2 GPS Cl     | DMA Principle              | 12   |

| 2.      | 3 GPS Re     | eceiver Front Ends         | 14   |

| 2.4     | 4 GPS P-     | code Acquisition           | 15   |

|         | 2.4.1        | Sequential Search          | 17   |

|         | 2.4.2        | Parallel Code Phase Search | 18   |

| 2.      | 5 Softwa     | re and Hardware Receiver   | 19   |

| Chapter | 3            |                            | 21   |

| Chapter | 5            |                            |      |

| Direc   | ct GPS P-co  | de Acquisition Modeling    |      |

| 3.      | 1 Introdu    | ction                      |      |

| 3.      | 2 P-code     | Property                   | 22   |

| 3.3       | FFT Se   | earch and Zero Padding                            | 26  |

|-----------|----------|---------------------------------------------------|-----|

| 3.4       | Compa    | arison of Different Acquisition Methods           | 27  |

| 3.5       | Direct   | Average Method                                    |     |

| 3.6       | Effect   | of Code Phase Shift                               |     |

| 3.7       | Overla   | ap Average Method                                 |     |

| 3.8       | Noise    | Effect                                            | 49  |

| 3.9       | Examp    | ple                                               | 63  |

| 3.10      | Conclu   | usion                                             | 65  |

| Chapter 4 |          |                                                   | 67  |

| GPS P-c   | code Ge  | nerator Architecture                              | 67  |

| 4.1       | P-code   | e Generator Architecture                          | 69  |

| 4.2       | GPS P    | P-code Generator Tuning Model                     | 71  |

| 4.3       | P-code   | e Generator Design Verification                   | 76  |

| Chapter 5 |          |                                                   | 84  |

| Direct C  | GPS P-co | ode Acquisition Design                            | 84  |

| 5.1       | Introdu  | uction                                            | 84  |

| 5.2       | Archit   | ecture of Direct GPS P-code Acquisition Processor | 85  |

| 5.3       | Local    | Reference Generation Unit                         | 87  |

| 5.4       | Local    | Reference FFT Processor                           | 90  |

|           | 5.4.1    | Xilinx 1024-Point FFT/IFFT Core                   | 93  |

|           | 5.4.2    | Controller FFT_MACH                               | 95  |

|           | 5.4.3    | Loop Counter                                      | 97  |

|           | 5.4.4    | RAM2 and RAM_FFT                                  | 98  |

|           | 5.4.5    | Debug Setup                                       | 98  |

| 5.5       | Compl    | lex Conjugate Multiplication Processor            | 100 |

v

| 5.6       | IFFT Pr   | ocessor                                      | 105 |  |

|-----------|-----------|----------------------------------------------|-----|--|

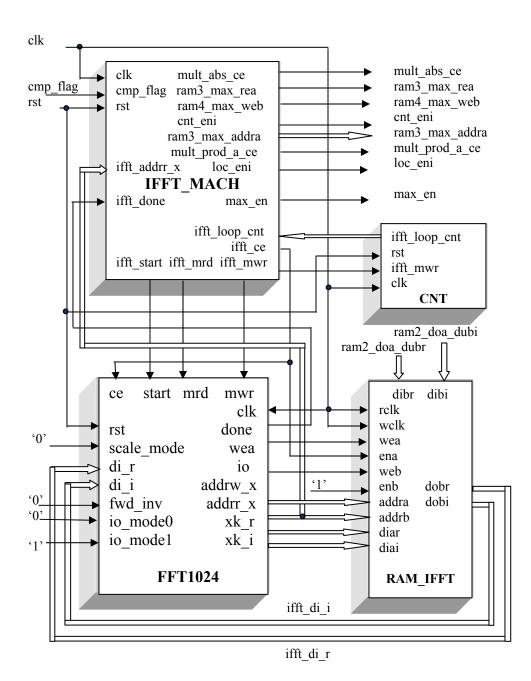

|           | 5.6.1     | Controller IFFT_MACH                         | 108 |  |

| 5.7       | Correlat  | tion Amplitude Square Unit                   | 111 |  |

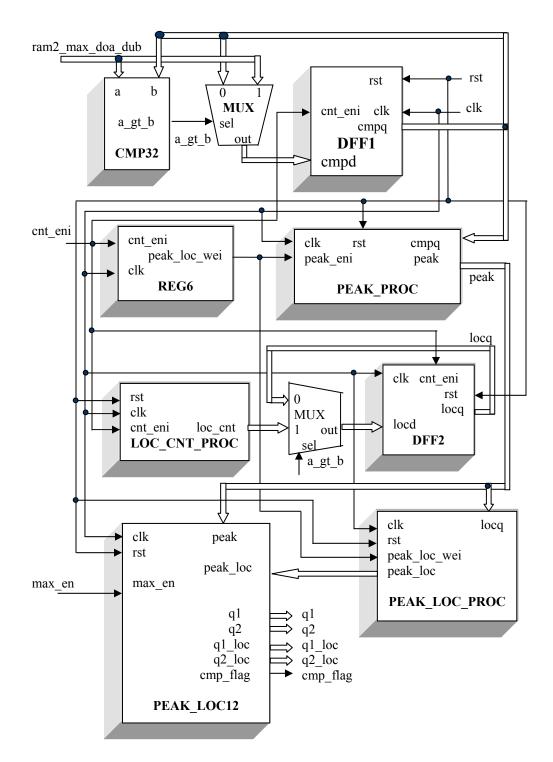

| 5.8       | Correlat  | Correlation Peak and Peak Location Processor |     |  |

|           | 5.8.1     | Correlation Peak Processor                   | 114 |  |

|           | 5.8.2     | Correlation Peak Location Processor          | 114 |  |

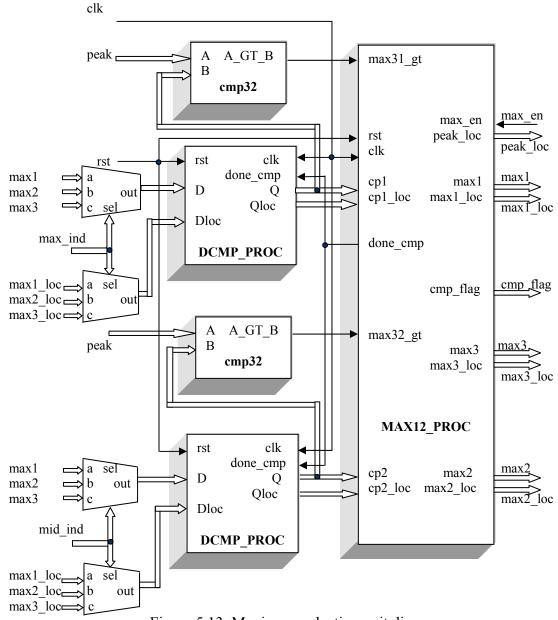

| 5.9       | Maximu    | am Selection Unit                            | 116 |  |

| 5.10      | Hardwa    | re Design Cost                               | 118 |  |

| 5.11      | Conclus   | sion                                         | 119 |  |

|           |           |                                              |     |  |

| Chapter 6 |           |                                              | 121 |  |

| FPGA I    | Design Ve | erification                                  | 121 |  |

| 6.1       | Introduc  | ction                                        | 121 |  |

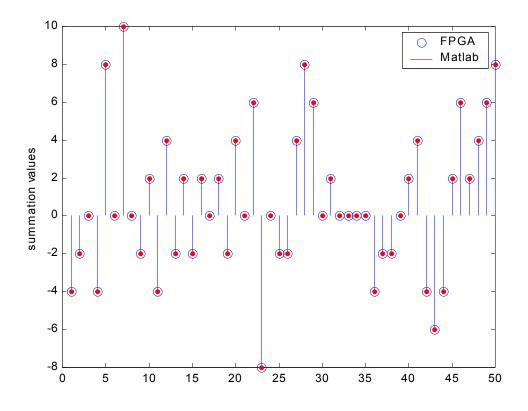

| 6.2       | Verifica  | tion of P-code Average With Scaling          | 122 |  |

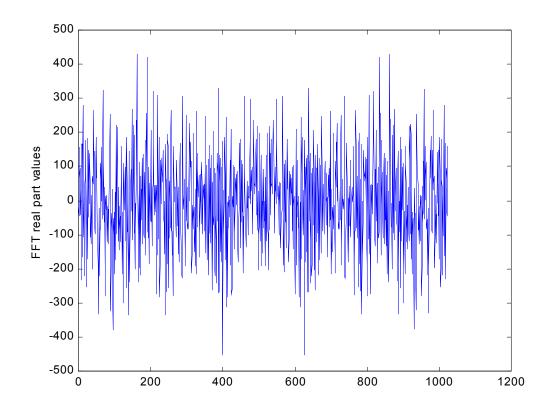

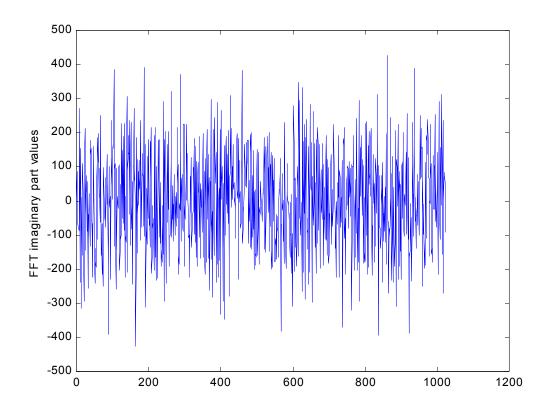

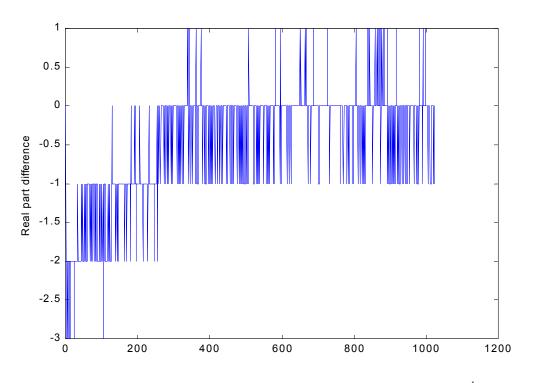

| 6.3       | Verifica  | tion of FFT                                  | 123 |  |

| 6.4       | Verifica  | tion of Complex Conjugate Multiplication     |     |  |

| 6.5       | Verifica  | tion of IFFT                                 | 130 |  |

| 6.6       | Verifica  | tion of Correlation Square                   | 134 |  |

| 6.7       | Final V   | erification Results                          | 135 |  |

| 6.8       | Conclus   | sion                                         |     |  |

| Chapter 7 |           |                                              | 140 |  |

| Summar    | ry and Fu | ture Work                                    | 140 |  |

| 7.1 \$    | Summary   |                                              | 140 |  |

| 7.2       | Future W  | ork                                          | 143 |  |

| References          | 144 |

|---------------------|-----|

|                     |     |

| Appendix A          |     |

| The Strathnuey Card | 154 |

| Abstract            | 156 |

vii

# LIST OF TABLES

| Table 3.1 Performance comparison of different acquisition methods                    |

|--------------------------------------------------------------------------------------|

| Table 3.2 C/No ratio for different acquisition methods with acquisition detection    |

| probability of around 90%                                                            |

| Table 3.3 Correlation and acquisition margin characteristics using different schemes |

| without noise                                                                        |

| Table 3.4 Correlation and acquisition margin characteristic using different schemes  |

| with added noise                                                                     |

| Table 4.1 Solution table for example 1                                               |

| Table 4.2 P-code Vector States [ICD-GPS-200]                                         |

| Table 4.3 Case 1 P-code generator initialization table                               |

| Table 4.4 Case 2 P-code generator initialization table                               |

| Table 4.5 P-code Reset Timing at the end of a week.    83                            |

| Table 5.1 VirtexE FPGA design cost.    118                                           |

| Table 6.1 Correlation square peak and code phase shift over 10 ms in verification    |

| of case 1                                                                            |

| Table 6.2 Correlation square peak and code phase shift over 10 ms in verification    |

| of case 2                                                                            |

| Table 6.3 | Correlation square peak and code phase shift over 10 ms in verification of |

|-----------|----------------------------------------------------------------------------|

|           | case 3                                                                     |

| Table 6.4 | Correlation square peak and code phase shift over 10 ms in verification of |

|           | case 4                                                                     |

ix

# LIST OF FIGURES

| Figure 2.1  | BPSK diagram10                                                           |

|-------------|--------------------------------------------------------------------------|

| Figure 2.2  | GPS signal structure                                                     |

| Figure 2.3  | GPS signal acquisition two-dimensional searching area16                  |

| Figure 2.4  | Sequential search direct GPS P-code acquisition diagram17                |

| Figure 2.5  | Parallel code phase search direct GPS P-code acquisition diagram19       |

| Figure 3.1  | Autocorrelation of P-code over 50 ms                                     |

| Figure 3.2  | Direct acquisition autocorrelation in 1ms24                              |

| Figure 3.3  | Direct acquisition: acquisition margin distribution over 1s25            |

| Figure 3.4  | Direct average autocorrelation result                                    |

| Figure 3.5  | Direct average method: acquisition margin distribution over 1s32         |

| Figure 3.6  | Direct average acquisition example                                       |

| Figure 3.7  | Correlation resolution improvement                                       |

| Figure 3.8  | Direct average method: correlation results with a code phase shift of 64 |

|             | samples                                                                  |

| Figure 3.9  | Direct average method: acquisition margin distribution over 1s with a    |

|             | code phase shift of 64 samples                                           |

| Figure 3.10 | Direct average method: detected correlation peak value change, case 138  |

| Figure 3.11 | Direct average method: detected correlation peak value change, case 139  |

| Figure 3.12 | Correlation result using overlap average method                          | 40  |

|-------------|--------------------------------------------------------------------------|-----|

| Figure 3.13 | Statistical acquisition margin result for overlap average method         | 41  |

| Figure 3.14 | Correlation result for overlap average method with a code phase shift of |     |

|             | 64 samples                                                               | 42  |

| Figure 3.15 | Statistical acquisition margin result for overlap average method with a  |     |

|             | code phase shift of 64 samples                                           | 43  |

| Figure 3.16 | Overlap average method: two reference overlap, case 1                    | .44 |

| Figure 3.17 | Overlap average method: two reference overlap, case 2                    | .44 |

| Figure 3.18 | Peak correlation location detection difference using two different       |     |

|             | references                                                               | 45  |

| Figure 3.19 | Peak correlation location detection pattern change                       | 46  |

| Figure 3.20 | Overlap average method: two reference overlap, case 3                    | 47  |

| Figure 3.21 | Overlap average method by using three references                         | .48 |

| Figure 3.22 | Noise effect on direct autocorrelation result of p-code up samples over  |     |

|             | 1 ms                                                                     | 51  |

| Figure 3.23 | Direct acquisition: noise effect on acquisition margin result            | 52  |

| Figure 3.24 | Direct average method: correlation result with added Gaussian noise      | .53 |

| Figure 3.25 | Direct average method: noise effect on acquisition margin                | .54 |

| Figure 3.26 Direct average method: noise effect on detected correlation peak change  |

|--------------------------------------------------------------------------------------|

| with code phase shift55                                                              |

| Figure 3.27 Overlap average method: correlation result with added Gaussian noise56   |

| Figure 3.28 Overlap average method: noise effect on acquisition margin               |

| Figure 3.29 Overlap average method: noise effect on detected correlation peak change |

| with code phase shift57                                                              |

| Figure 3.30 Direct average method: misdetection probability with different carrier   |

| to noise ratio when signal code phase shift is 64 samples                            |

| Figure 3.31 Overlap average method: misdetection probability with different carrier  |

| to noise ratio when signal code phase shift is 64 samples60                          |

| Figure 3.32 Direct average method misdetection probability distribution in 1 s with  |

| carrier to noise ratio equal to 39 dB61                                              |

| Figure 3.33 Overlap average method misdetection probability distribution in 1 s with |

| carrier to noise ratio equal to 39 dB62                                              |

| Figure 3.34 Acquisition by direct average method                                     |

| Figure 3.35 Acquisition by overlap average method                                    |

| Figure 3.36 Resolution improvement by correlating 128 samples                        |

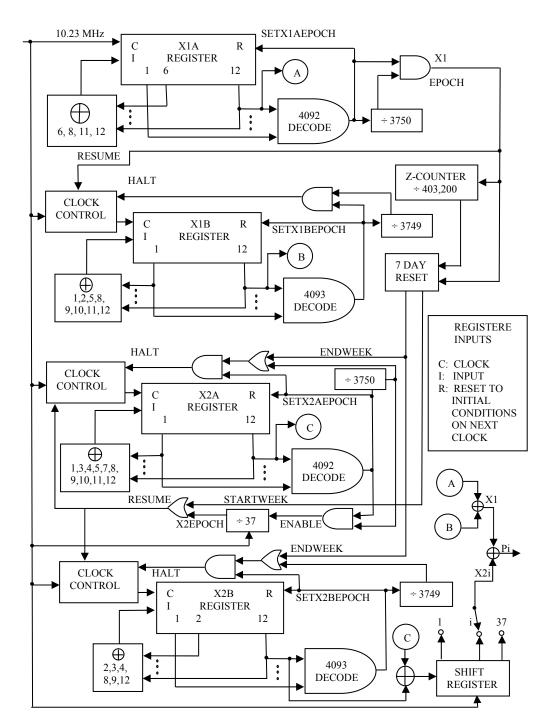

| Figure 4.1  | GPS P-code Signal Generator                                       | 68  |

|-------------|-------------------------------------------------------------------|-----|

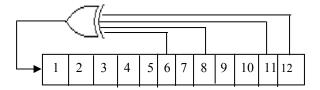

| Figure 4.2  | X1A LFSR Diagram                                                  | 70  |

| Figure 4.3  | X1B LFSR Diagram                                                  | 70  |

| Figure 4.4  | X2A LFSR Diagram                                                  | 71  |

| Figure 4.5  | X2B LFSR Diagram                                                  | 71  |

| Figure 4.6  | Case 2 simulation waveform                                        | 80  |

| Figure 4.7  | The final X2AQ chip generation at the end of a week               | 81  |

| Figure 4.8  | The final X1BQ chip generation at the end of a week               | 81  |

| Figure 4.9  | Resume of X1AQ, X1BQ, X2AQ and X2BQ at the start of week          | 82  |

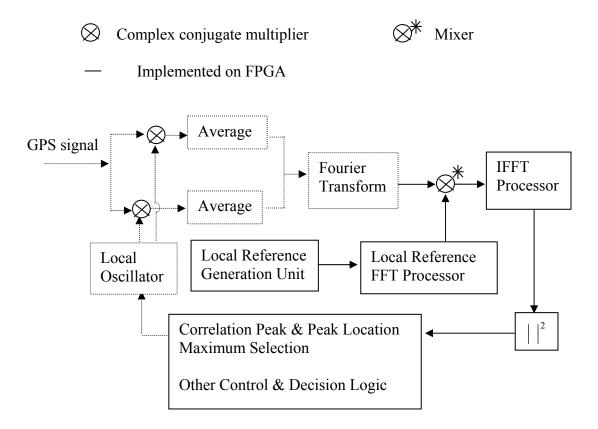

| Figure 5.1  | Direct GPS P-code Acquisition Processor                           | 86  |

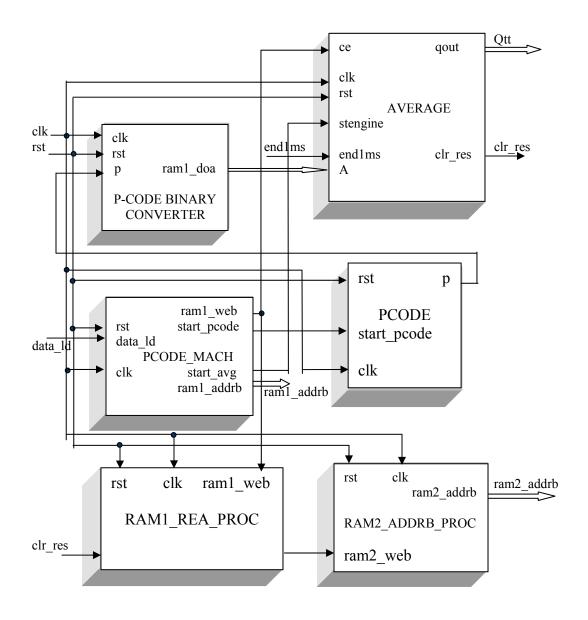

| Figure 5.2  | Local Reference generation unit diagram                           | 88  |

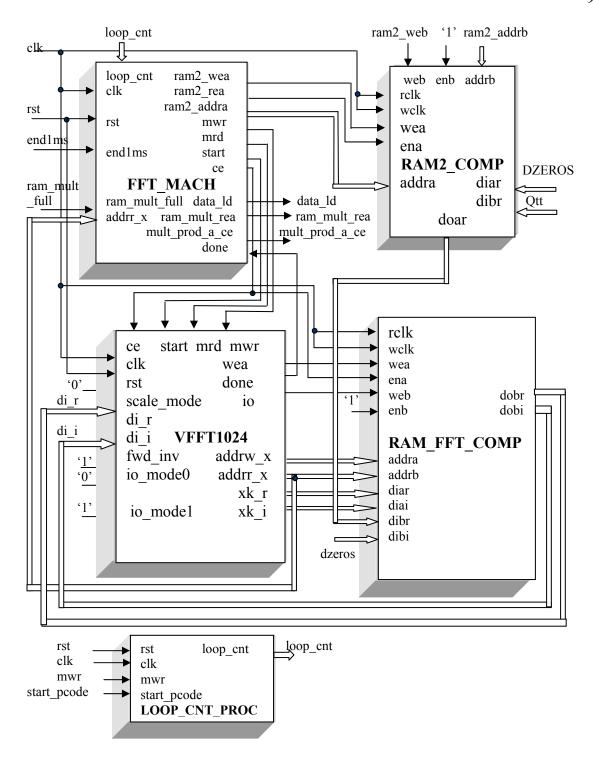

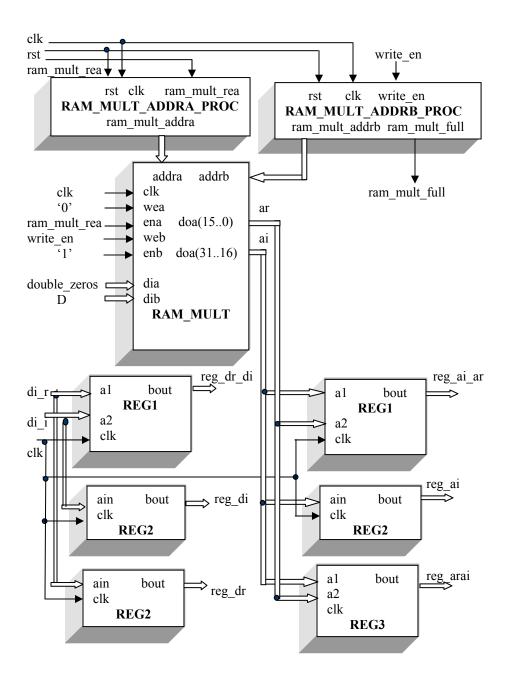

| Figure 5.3  | Local reference FFT processor diagram                             | 91  |

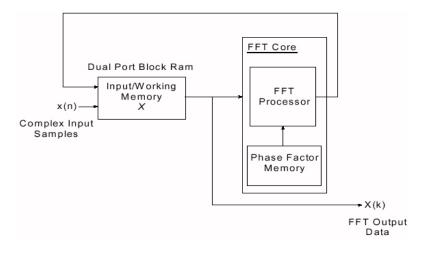

| Figure 5.4  | Xilinx 1024-point FFT/IFFT core single memory space configuration | 94  |

| Figure 5.5  | Debug Use Block RAM diagram                                       | 100 |

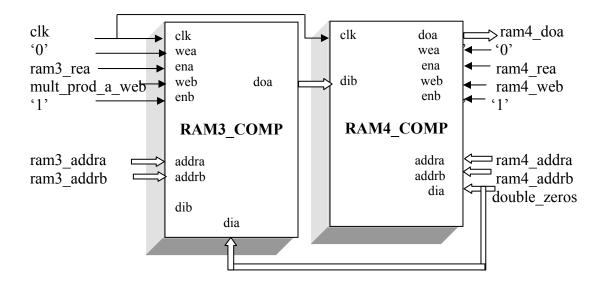

| Figure 5.6  | Complex conjugate multiplication processor (part 1)               | 102 |

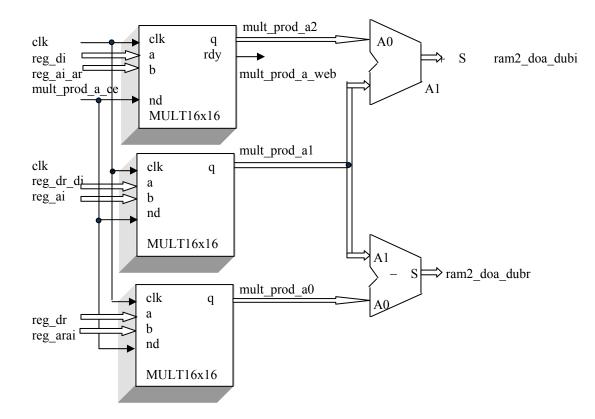

| Figure 5.7  | Complex conjugate multiplication processor (part 2)               | 103 |

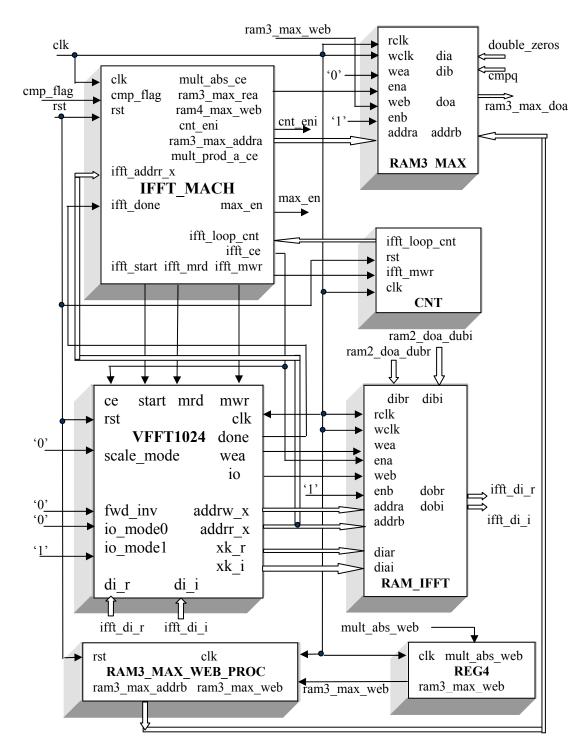

| Figure 5.8  | IFFT processor diagram                                            | 106 |

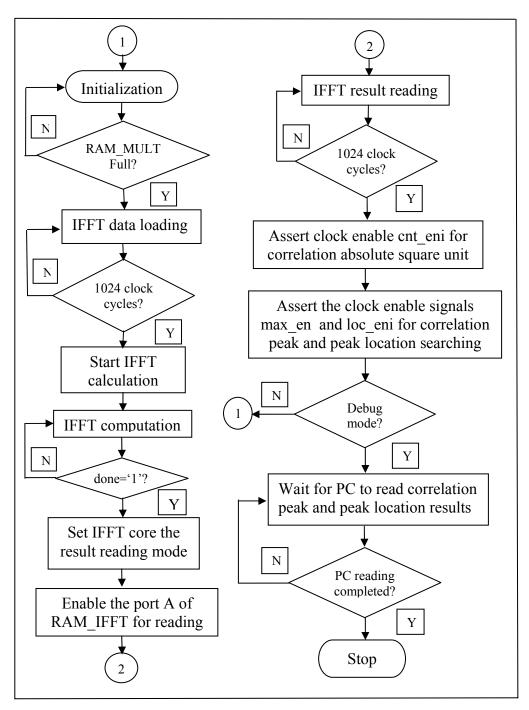

| Figure 5.9  | The controller IFFT_MACH flow chart                               | 109 |

| Figure 5.10 | 0 Controller IFFT_MACH interface FFT/IFFT core diagram            | 110 |

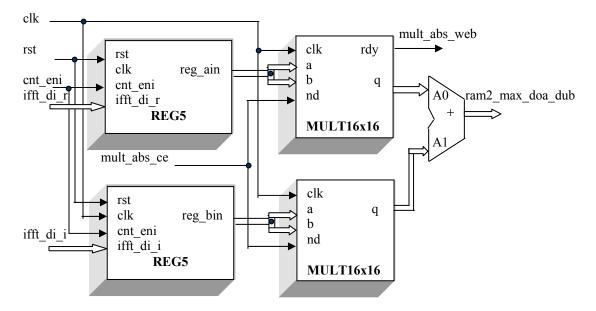

| Figure 5.1  | 1 Correlation amplitude square unit diagram                       | 111 |

| Figure 5.12 | 2 Correlation peak and peak location processor diagram            | 113 |

xiii

| Figure 5.13 Maximum selection unit diagram                                           | 117 |

|--------------------------------------------------------------------------------------|-----|

| Figure 6.1 2nd ms GPS binary P-code average result                                   | 123 |

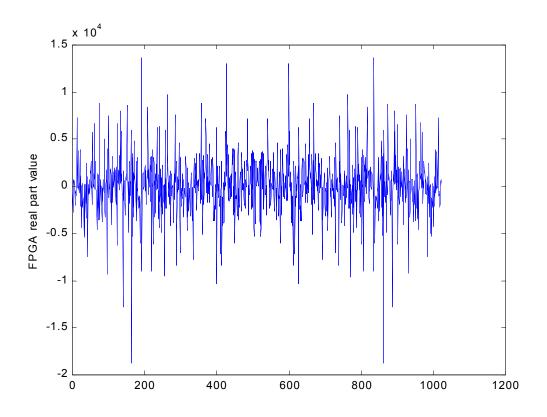

| Figure 6.2 FPGA FFT real part values in the 2 <sup>nd</sup> ms                       | 124 |

| Figure 6.3 FPGA FFT imaginary part values in the 2 <sup>nd</sup> ms                  | 125 |

| Figure 6.4 FPGA and Matlab FFT real part difference in the 2 <sup>nd</sup> ms        | 126 |

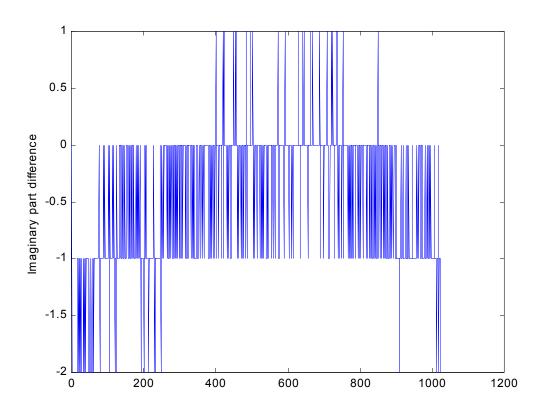

| Figure 6.5 FPGA and Matlab FFT imaginary part difference in the 2 <sup>nd</sup> ms   | 127 |

| Figure 6.6 FPGA complex multiplication real part in the 2 <sup>nd</sup> ms           | 128 |

| Figure 6.7 FPGA complex multiplication imaginary part in the 2 <sup>nd</sup> ms      | 129 |

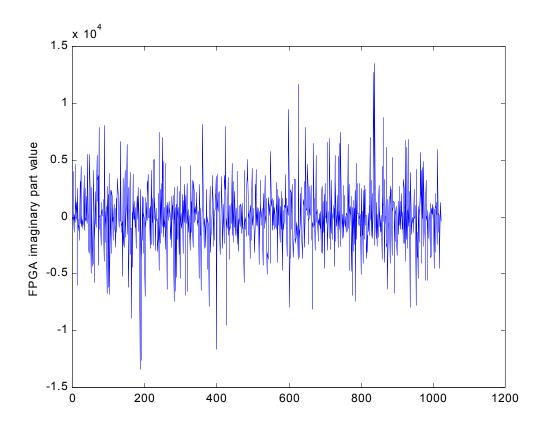

| Figure 6.8 FPGA IFFT real part in the 2 <sup>nd</sup> ms                             | 130 |

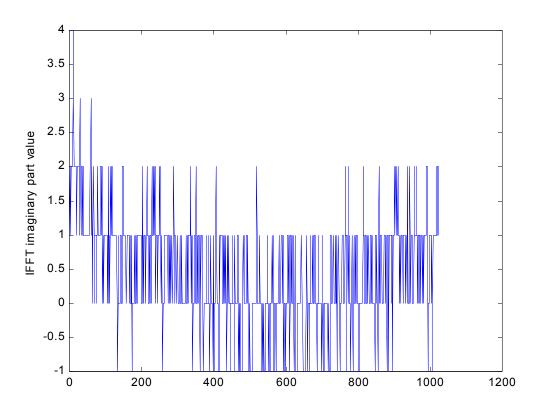

| Figure 6.9 FPGA IFFT imaginary part in the 2 <sup>nd</sup> ms                        | 131 |

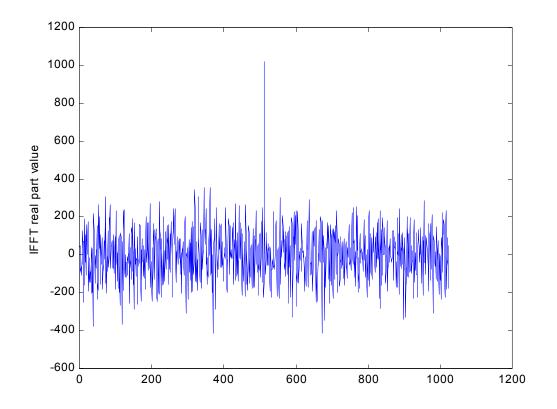

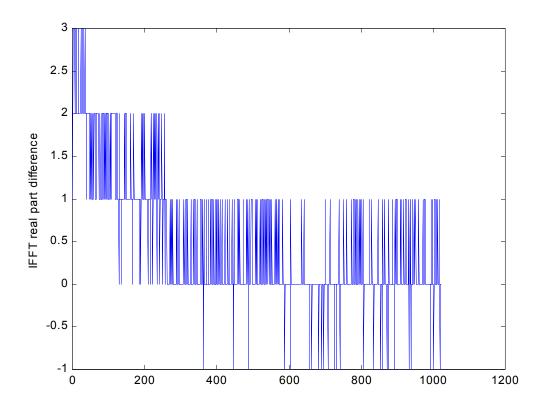

| Figure 6.10 FPGA and Matlab IFFT real part difference in the 2 <sup>nd</sup> ms      | 132 |

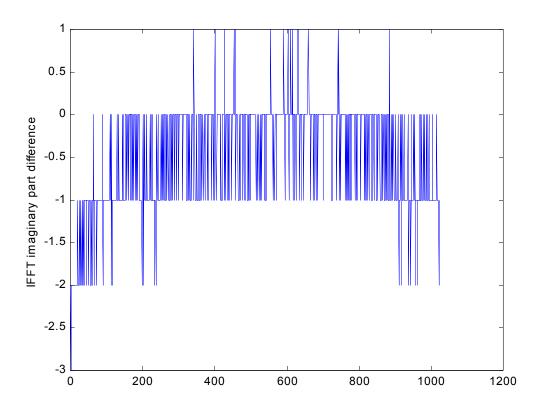

| Figure 6.11 FPGA and Matlab IFFT imaginary part difference in the 2 <sup>nd</sup> ms | 133 |

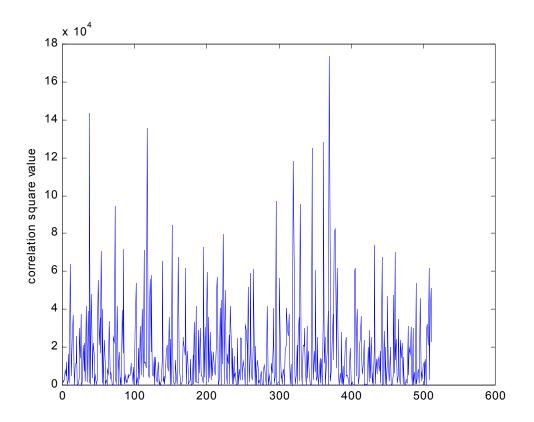

| Figure 6.12 FPGA correlation square values in the 2 <sup>nd</sup> ms                 | 134 |

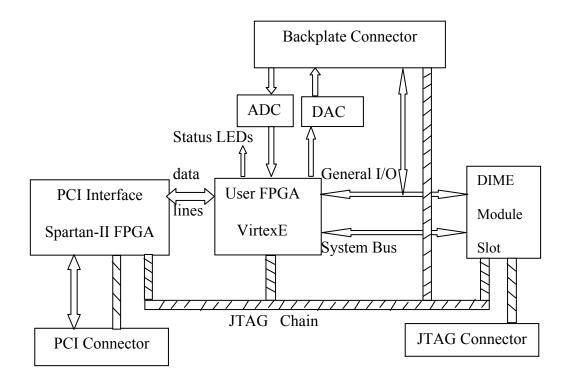

| Figure A-1 Strathnuey FPGA board architecture                                        | 155 |

## LIST OF ABBREVIATIONS

- ADC: Analog to Digital Converter

- AS: Anti-Spoofing

- ASIC: Application Specific Integrated Circuits

- BPSK: Binary Phase Shift Keying

- C/A: Coarse Acquisition

- CDMA: Code Division Multiple Access

- CLB: Configurable Logic Block

- C/No: Carrier-to-Noise Density Ratio

- DFT: Discrete Fourier Transform

- DIF: Decimation-In-Frequency

- DOD: Department of Defense

- DSP: Digital Signal Processing

- DSSS: Direct Sequence Spread Spectrum

- FFT: Fast Fourier Transform

- FPGA: Field Programmable Gate Array

- GPS: Global Position System

- GRM: Generic Routing Matrix

- HDL: Hardware Description Language

- HOW: Hand-Over-Word

- IDFT: Inverse Discrete Fourier Transform

- IF: Intermediate Frequency

- IFFT: Inverse Fast Fourier Transform

- IOB: Input/Output Block

- IP: Intellectual Property

- LFSR: Linear Feedback Shift Registers

- LNA: Low Noise Amplifier

- NF: Noise Figure

- NCO: Numerically Controlled Oscillator

- P-code: Precision Code

- PPS: Precise Positioning Service

- PRN: Pseudorandom Noise

- RF: Radio Frequency

- RTL: Register-Transfer-Level

- SNR: Signal-to-Noise Ratio

- SPS: Standard Positioning Service

- Y-code: Encrypted P-code

## Chapter 1

### Introduction

The Global Positioning System (GPS) is a worldwide, satellite-based navigation system. It is being funded and operated by the U.S. Department of Defense (DOD). The concept of GPS started in the early 1970's, and it was originally intended for military applications. Later, the U.S. government made the system available for civilian use. The increased performance of GPS has fuelled the continued growth of the GPS market (El-Rabbany, 2002 and Pace, 1995). It has been used in agriculture (Bauer, 1994), mining (Flinn, 1999 and Jensen, 1992), transportation (Drane, 1998), surveying (Leick, 1995), land (Hada, 2000), marine (Trimble, 1998), airborne navigation (Hayward, 1998) and many other applications (Parkinson, vol. II, 1996).

GPS provides specially coded satellite signals that can be processed in a GPS receiver. A receiver measures the elapsed time between the emission and the reception of the GPS signal. This time is then multiplied by the speed of light to obtain the distance between the satellite and the receiver, which is referred to as pseudorange, not range (Langley, 1993), because the measurements contain errors and biases coming from the synchronization error between the satellite and receiver clocks, multipath errors and other error sources. GPS provides the pseudorange and carrier phase measurements. While

GPS signal acquisition gives coarse estimates of these measurements, carrier phase tracking provides a precise measurement of change in the satellite user pseudorange over a time interval, and the estimates of its instantaneous rate, or Doppler. Estimations of position and velocity are based on these measurements (Braasch, 1999 and Ward, 1995). A minimum of four measurements made on four different satellites can precisely determine position, velocity, and time (Kaplan, 1990).

The GPS satellites transmit two carrier frequencies: L1 (1575.42 MHz) and L2 (1227.60 MHz). The pseudorandom noise (PRN) codes (Misra, 2001) and navigation data message are added to the carriers as binary phase modulations (Rappaport, 1995). The navigation data message is a 50 bits/second digital data stream, which contains GPS satellite coordinates, the satellite health status, the satellite clock correction, the satellite almanac, and other satellite system parameters (Kaplan, 1990). The PRN codes include C/A (coarse acquisition) code on L1 carrier and P (precise) code on L1 and L2 carriers. The codes are called chips instead of bits to emphasize they do not carry data. Compared with the C/A code, which is 1023 chips long and is broadcast at 1.023 Mega-chips per second, the P-code is much longer (seven days) with a faster chipping rate 10.23 MHz, offering much higher accuracy (Misra, 1999 and Hoffmann-Wellenhof, 1994). The P-code is encrypted and the resulting code is called P(Y)-code. The encrypted P(Y)-code is for use only by authorized users with cryptographic keys.

Every GPS receiver design involves GPS signal acquisition, code tracking loop, and carrier tracking loop circuit design (Kaplan, 1990). The acquisition circuit searches

over a three-parameter space: satellite PRN code, code phase, and carrier frequency to acquire the signal. Acquisition can provide a "coarse" estimation of the pseudorange. The code tracking loop tracks the locally generated PRN code to be synchronized with the received code in order to despread the signal, derive navigation data and timing information.

Traditionally, the GPS receiver locks onto the C/A code to extract the navigation data message. The Hand-over-word (HOW) is the second word in each subframe/page of a navigation message. A HOW occurs every six seconds in the data frame (ICD-GPS-200, 1991). It provides the necessary timing information to tell where the P(Y) code pattern is in its whole sequence.

Then, starting from the HOW, acquisition is transferred to the P-code acquisition part. As a result, P-code acquisition relies on the hand over from an acquired C/A code (Lin, 1999). This is because the C/A code repeats every millisecond so that synchronizing to the C/A code is easy. A brute force chip-by-chip search of P-code is formidable in terms of the number of search trials and the time required to carry it out. But if the receiver can accurately predict the satellite signal transmit time and the satellite location, direct P(Y)-code acquisition is faster than handover from the C/A code search. During certain military operations, the C/A-code signal could be degraded so that the use of the open Standard Positioning Service to adversaries is denied and the use of the encrypted P(Y)-code is still sustained. Consequently, direct acquisition of the P code is the only option available. Newer designs attempt to achieve acquisition without first acquiring the

C/A code and use the P(Y)-code for direct acquisition.

The direct P (Y)-code acquisition potential is a more robust functionality for GPS receivers to provide the ability to acquire the P(Y)-code without the aid of the C/A code (Zyfer, 2002). Application of P(Y)-code rate sequences can also be used on pseudolites that implement wideband code formats. In situations with limited or no visibility of the GPS satellites, ground transmitters that emulate the signal structure of the GPS satellites (pseudolites) (Cobb, 1998) can be used as additional or replacement signal sources (Wang, 2000 and Stone, 1999). Pseudolites are useful for a variety of applications, including differential GPS implementation in aircraft precision approach in the Category II and III for universal availability. Pseudolites have the capability to augment the GPS constellation, providing better geometry for enhanced positioning accuracy, reliability, availability, continuity, and integrity monitoring. In addition they can be used to speed up integer ambiguity resolution in differential carrier phase applications, due to the large geometry change possible with the pseudolite signal (Ndili 1994).

The overall objective of this dissertation is to implement the direct GPS P-code acquisition algorithm using FPGA (Field Programmable Gate Array) technology. The challenges are how to reduce the code phase search time for the extremely long period of the P-code, how to avoid large size Fast Fourier Transform (FFT), and how to design the P-code generator, which can rapidly produce the P-code at any specific time of a GPS week. The exploration of the direct GPS P-code acquisition algorithm presents a good starting point for meeting these objectives. To produce a local code, which can continuously duplicate the incoming GPS signal code phase, the initial unknown code phase has to be determined by searching through a set of possible phases around an initial time estimate. If a search over 10 ms is needed, this can be translated into a location uncertainty of  $3 \times 10^6$  meters. This location uncertainty may be caused by the uncertainty of the satellite location, the satellite clock offset, the receiver clock offset or other uncertainty factors from the time of transmission to the time of reception. The fast P-code phase search using the direct average and overlap average method proposed in this dissertation may be a tradeoff of the carrier to noise ratio performance. In addition, the proposed methods use a small size FFT/IFFT, which greatly facilitates the FPGA hardware design.

After the direct P-code acquisition algorithm is proposed and simulated, it is possible to have a hardware design to map the algorithm. A FPGA is a good choice to do hardware design. FPGA offers the advantage of short design cycles, rich resources, and programmability (Trimberger, 1994). In the past, FPGAs were primarily used for prototyping and lower volume applications. Custom ASICs were used for high volume, cost sensitive designs. Today's deep submicron fabrication technologies enable design engineers to implement an impressive number of components like microprocessors, memories, and interfaces in a single microchip (Langen, 2002). With today's deep submicron technology, it is possible to deliver over several millions usable system gates (Xilinx White Paper, 2002) and system speeds up to several hundreds MHz in an FPGA. In addition, the average ASIC design operating at 50-100 MHz can be implemented in an

FPGA using the same RTL (Register-Transfer-Logic) synthesis design methodology as ASICs. As device densities keep increasing, not only new levels of systems are integrated onto a single chip, but also a wide variety of features and capabilities are allowed for reprogrammable technology. Moreover, several companies, such as LSI Logic (Matsumoto, 1999), ADI (Ohr, 2000), Lucent (Lucent, 2000), QuickLogic (Merritt, 2000), Actel (Tanurhan, 2001), some startup companies (Matsumoto, 2000) and so on, already provide pre-designed and pre-verified blocks, often called cores or intellectual property (IP) blocks (Wilton, 2001). Fixed hardware designs called hardcores are incorporated into the FPGA architecture such as PowerPC/ARM processor cores, Booth multipliers for DSP (Digital Signal Processing) data paths, serial transceivers and so on (Xilnix, 2003). On the other hand, softcores are flexible IP building blocks that take full advantage of an efficient and flexible implementation in the FPGA including PCIcores for I/O busses, processor cores, Viterbi decoders for DSP functions and many other examples (Hellmich, 2000 and Erdogan, 2003). These programmable logic cores are utilized by other companies and combined onto a single chip, and in a design process called System-on-a-Chip methodology (Savage, 2000 and Vladimirova, 2000).

This dissertation's major objectives are twofold: (1) to develop and analyze a direct GPS P-code acquisition algorithm which targets on FPGA design, and (2) to design FPGA architecture implementing the proposed algorithm.

The difficulty of direct GPS P-code acquisition is the extremely long period of the P-code, which makes the search for the correct carrier frequency and code phase very

slow. The promising methods to improve acquisition speed proposed by other researchers focus more on software simulation performance. They require large Fast Fourier Transform size. This is prohibiting in FPGA design because of large hardware resource requirement and design complexity. As a result, an appropriately scaled direct P-code acquisition design algorithm, especially for FPGA implementation would be desirable.

In addition, the design of a P-code generator is also a challenging task in this work. The basic properties of P-code are described in the literature, but there is no complete detailed hardware implementation of a P-code generator. Another necessary feature will be the availability of a P-code starting from any time of a week. This fits into the situation that there is approximate time information so that acquisition starts from some specific time range.

In order to have a successful implementation of the whole direct GPS P-code acquisition system in FPGA, Nallatech FPGA board interface and Xilinx VirtexE FPGA architecture features must be studied and utilized in the design. The whole system design should be partitioned into different processing parts. Each processor must be properly designed and the signal flows between different parts must be properly handled. It is very beneficial to use the Xilinx 1024-point FFT/IFFT core to achieve a fast system design cycle. A controller which is designed to meet the Xilinx 1024-point FFT/IFFT timing specification is critical for the integration of the core into the whole design system. A exhaustive test is also necessary to see how stable the FFT/IFFT results are and to verify

if the controller is right. At last, all synthesizable VHDL codes need to be downloaded on the FPGA board. Each partitioned processor must be verified. The final overall results should give the right direct P-code acquisition code phase shift and acquired maximum correlation information.

This dissertation is organized as follows. Chapter 2 covers the necessary GPS principles of operation. Chapter 3 models the direct GPS P-code acquisition algorithm and its modifications. The comparisons of different direct GPS P-code acquisition techniques are also made in this chapter. Then, Chapter 4 presents the GPS P-code generator architecture, design strategy and test results of P-code generator design. Next, Chapter 5 gives details on direct GPS P-code acquisition design implementation. In addition, Chapter 6 verifies each step and the overall FPGA designs. At last, Chapter 7 summarizes the whole dissertation and provides direction for future research.

## Chapter 2

### **GPS** Background

This chapter deals with some important concepts of GPS such as GPS signal structure, GPS code division multiple access (CDMA) principle, GPS receiver front ends, GPS P-code acquisition, software and hardware receivers. GPS signal structure and CDMA are the basic underlying components for GPS. A GPS receiver receives GPS signals by its front end, processes them in analog domain, and then outputs digital signals from an A/D converter for further acquisition process. Both sequential and parallel code phase search methods are explained. Furthermore, software and hardware receiver implementation are compared.

#### 2.1 GPS Signal Structure

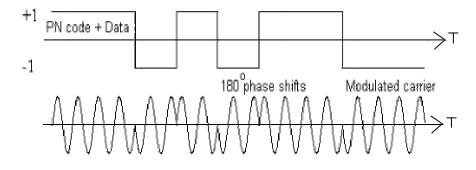

Each GPS satellite transmits a unique navigational signal centered on two L-band frequencies of the electromagnetic spectrum: L1 at 1575.42 MHz and L2 at 1227.60 MHz. PRN codes and navigation message modulate the L1 and/or L2 carrier phase using the binary phase shift keying (BPSK) modulation technique (Kaplan, 1990). The binary codes are directly multiplied with the carrier, which results in a 180-degree phase shift of

the carrier every time the code changes its state. A BPSK diagram is shown in Figure 2.1.

Figure 2.1 BPSK diagram (Braasch, 1999)

The C/A code is a repeating 1.023 MHz PRN code. There is a different C/A code PRN for each satellite. C/A sequences belong to Gold codes, which have very good autocorrelation and cross correlation properties. The P-code is a very long (seven days) 10.23 MHz PRN code. In the Anti-Spoofing (AS) mode of operation, the P-code is encrypted into the P(Y)-code. The encrypted P(Y)-code requires a classified AS module for each receiver channel and is used only by authorized users with cryptographic keys.

The C/A code is the basis for Standard Positioning Service (SPS) and the P-code offers Precise Positioning Service (PPS). According to the 1999 Federal Radio Navigation Plan, the SPS predictable accuracy is around 100-meter horizontal accuracy, 156-meter vertical accuracy and 340-nanosecond time accuracy. The PPS predictable accuracy is around 22meter horizontal accuracy, 27.7-meter vertical accuracy and 200- nanosecond time accuracy.

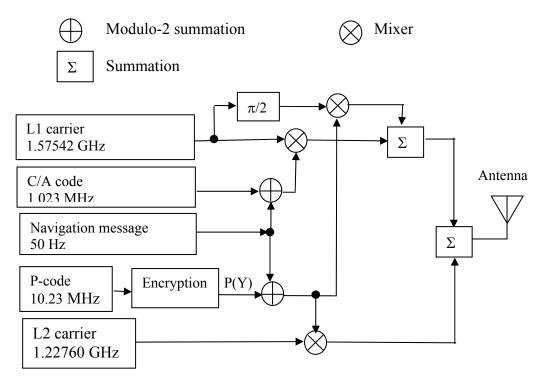

The L1 signal is modulated by both the C/A code and the P(Y)-code, which are at

90 degrees to each other, so that one is in phase and the other is in quadrature. The L2 signal is modulated by the P(Y)-code.

The navigation message modulates both the L1 and L2 signals. The GPS navigation message contains parameters that describe the location of the GPS satellites, their clock offsets, and various other system parameters. Each satellite transmits a navigation message at 50 bits per second. The navigation message is composed of five subframes. Each subframe contains 10 words of 30 bits.

Figure 2.2 shows the GPS signal structure modeled in equation (2.1).

$$S_{L1i}(t) = A_p P_i(t) D(t) \sin(2\pi f_{L1}t) + A_c G_i(t) D(t) \cos(2\pi f_{L1}t)$$

$$S_{L2i}(t) = B_p P_i(t) D(t) \sin(2\pi f_{L2}t)$$

(2.1)

where  $A_{p}$ ,  $A_{c}$  and  $B_{p}$  are signal amplitudes

$P_i(t)$  is the P code for satellite i

- $G_i(t)$  is the C/A code for satellite i

- D (t) is the navigation data for satellite i

- $f_{L1}$  is the L1 carrier frequency equal to 1575.42 MHz

- $f_{L2}$  is the L2 carrier frequency equal to 1227.60 MHz.

Figure 2.2 GPS signal structure (Kaplan, 1990)

### 2.2 GPS CDMA Principle

CDMA is a form of spread-spectrum, a digital communication technique that has been used in military applications for many years. Now it is one of the driving forces behind the rapidly advancing personal communications industry. CDMA uses unique noise-like spreading codes to spread the baseband data before transmission (Glisic, 1997 and Prasad, 1996). The signal can then be transmitted in a channel below the noise level. The receiver uses a correlator to despread the signal. One type of CDMA technique is direct sequence spread spectrum (DSSS) (Viterbi, 1995). GPS uses the BPSK DSSS technique. When the user receives the GPS signals, the receiver will mix the received signal with a locally generated PRN-code. The locally generated PRN-code must be synchronous with that generated from the satellite. After the receiver is fully correlated with the GPS data, a correlation peak is generated. Because GPS signals have very wide spread spectrum, they are transmitted at a much lower spectral power density than narrowband transmitters (Braasch, 1999).

One important signal quality parameter is the signal-to-noise ratio (SNR), which is a measure of the signal strength relative to background noise. The ratio is usually measured in decibels (dB) for a specified bandwidth. The noise can be approximated by

$$N = kT_E B \tag{2.2}$$

where k is Boltzmann's constant  $(1.3806 \times 10^{-23} JK^{-1})$

- B is the bandwidth in Hz

- $T_E$  is the effective noise temperature in Kelvin.

A normalized SNR to a 1-Hz bandwidth is called carrier-to-noise density ratio  $(C/N_a)$ . It is bandwidth-independent. The  $C/N_a$  is defined as equation 2.3.

$$C/N_{o} = (SNR)(B)[ratio - Hz]$$

(2.3)

where SNR is signal to noise ratio at certain stage of a receiver

B is the bandwidth of a receiver at the same stage.

The received satellite signal power varies with the user antenna gain, the satellite

elevation angle, and the satellite age. The typical  $C/N_o$  value is from 35 to 55 dB-Hz (Braasch, 1999).

#### 2.3 GPS Receiver Front Ends

The input to the GPS receiver is the analog GPS signal from an antenna via a lownoise pre-amplifier (LNA). The GPS signals are down converted by the radio frequency into the intermediate frequency (IF) signals, which are further converted by an A/D converter into the digital signals. These digital signals are taken by the GPS channels for the subsequent GPS acquisition and tracking process.

The RF front ends deal with the analog signal processing including filtering, amplification, and down conversion (Shaeffer, 1998). The main design parameters that have to be taken into consideration are antenna gain, LNA gain, LNA intermodulation, noise figure (NF), and power consumption (Shahani, 1997, and Piazza, 1998). Sharp cutoff filters must suppress out-of-band interference. Hard-limiting architecture (1-bit A/D conversion) results in slightly degraded performance compared to that of a multibit converter, but it allows the design of a simpler, lower power receiver without employing automatic gain control. Downconversion is performed either in single or multiple stages (Braasch, 1999). Multistage architectures allow for adequate image suppression and general bandpass filtering with the final IF placed close to the baseband

single-stage. The final conversion to baseband involves converting the IF signal to the inphase and quadrature components of the signal envelope (Dierendonck, 1996).

#### 2.4 GPS P-code Acquisition

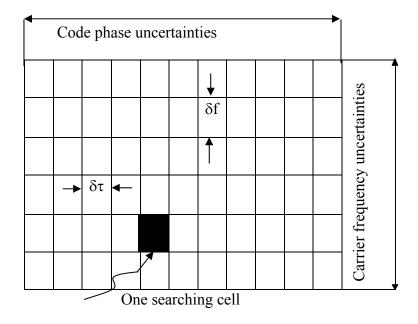

A GPS receiver performs a three-dimensional search to acquire a GPS satellite signal: the GPS satellite PRN code, code phase, and carrier frequency offset (Parkinson, vol. I, 1996). If one has no knowledge on which satellites are in space, the acquisition must be performed on all satellites. However, usually there is information on the rough location and the approximate time of day, so acquisition is only necessary for those satellites which are known to be available to receivers. For each satellite, a two dimensional search must be performed: code phase and carrier frequency.

In Figure 2.3,  $\delta \tau$  is typically 1/2 code chip and  $\delta f$  is Doppler bin. Carrier frequency uncertainties are due to unknown Doppler shift and local oscillator drift. The span of code phase to be searched depends on uncertainties in indicated clock time and receiver position (Brown, 2001). Due to the extremely long period of the P-code, a search over a one-week long P-code is challenging. The FPGA design requirement in this dissertation is to search the P-code code phase over 10 ms. In realistic stand-alone receivers, the usual search is within 1 s. Satellite induced Doppler frequency uncertainty is less than 10 Hz, and stationary receiver oscillator frequency offset is within 1 kHz.

Figure 2.3 GPS signal acquisition two-dimensional searching area

In situations with limited or no visibility of the GPS satellites, ground transmitters that emulate the signal structure of the GPS satellites (pseudolites) (Cobb, 1998) can be used as additional or replacement signal sources (Wang, 2000 and Stone, 1999). In pseudolite application, satellite introduced Doppler is less than 1 Hz, and the receiver oscillator frequency offset is less than 10 Hz if a Rubidium oscillator is used.

Traditionally, a C/A code can be quickly and easily acquired, and is used as a hand over which provides accurate time-tick information for P-code acquisition. Direct P-code acquisition is desirable when a C/A code is not available under jamming conditions but it is still possible to acquire P(Y)-code.

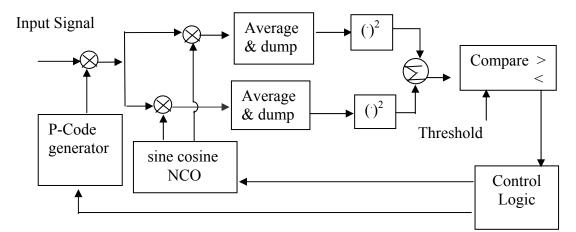

### 2.4.1 Sequential Search

In Figure 2.4, the acquisition is based on a measurement of the correlator output. The correlators provide a measurement of the total I and Q channel correlation energy over the integration time. The In-phase and Quadrature components I and Q respectively are formed by stripping off the reference code and the carrier from the received signal. When the replica and reference signals are aligned with the incoming signal, the amplitude of the recovered correlation energy is at a maximum. The amplitude is compared with a threshold. When the amplitude is at or above the threshold (Brown, GPS Solutions 2000), it is detected as the presence of the signal. In the presence of noise, one must set the threshold based upon an acceptable probability that a noisy measurement that does not contain the signal will appear to match the replica (Kaplan, 1996).

Figure 2.4 Sequential search direct GPS P-code acquisition diagram

#### 2.4.2 Parallel Code Phase Search

In time domain, a massive parallel P-code generator with 1,024 or even 2,048 correlator channels searching for a code match has been reported (Trimble, 2002).

General GPS acquisition parallel search techniques include the parallel frequency space search, and the parallel code-phase search. They limit the search space to carrier frequency space and code phase space respectively. When the number of Doppler bins to be searched is far less than that of the code phases, the parallel code-phase search is the most efficient approach.

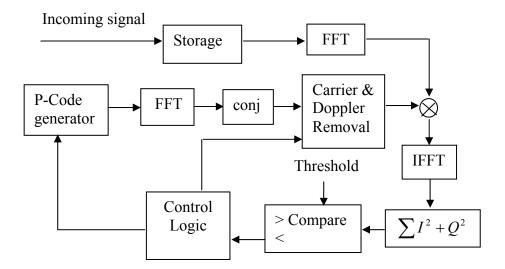

In Figure 2.5, the GPS acquisition scheme is shown implemented in the digital storage receiver using frequency domain correlation. In this architecture, the GPS signals are first buffered in memory to allow them to be accessed by hardware for processing. Since the GPS signals do not have to be processed in real-time, enhanced signal processing algorithms can be applied that allow the digital signals to be optimally reprocessed, maximizing the probability of acquiring the GPS signals in a challenging environment.

Figure 2.5 Parallel code phase search direct GPS P-code acquisition diagram

This approach takes advantage of the Fourier Transform correlation theorem which states that the frequency transform of the correlation function in the time domain is the product of the signals' transforms in the frequency domain. The FFT algorithm provides a convenient and computationally efficient method of performing correlations in the digital storage receiver architecture.

### 2.5 Software and Hardware Receiver

Development and operation of advanced GPS systems are provided through a variety of software (Brown, ION 2000 and Psiaki, 2001) and hardware solutions (BAE,

1998 and McCullagh, 1999). Except for the RF front ends, the software receiver implements the other receiver functions in software in a microprocessor (Kelley, 2002 and Krumvieda, 2001). The software based implementation of the receiver blocks allows the new acquisition architecture, improved tracking loops and other new features to be implemented, tested and simulated. New frequencies and new PRN codes can be used simply by making software changes. The software based approach can be used for the simulation of hardware receiver design and development.

Usually, the software receiver depends on a host processor that has limited capability to provide real time performance for GPS systems because of a required high dynamic range, a large bandwidth, and a large computation load. However, the use of pre-processors such as FPGA or DSP correlators (for correlation processing), FPGA or DSP processors for FFT processing (Masella, 1999 and Gerein, 2001) are available and provide real time capabilities.

## Chapter 3

# Direct GPS P-code Acquisition Modeling

#### 3.1 Introduction

In order to have a good direct P-code acquisition hardware design, a good understanding of P-code acquisition property and a good searching algorithm are needed. The efficiency of a searching algorithm greatly affects the P-code acquisition time. Although the general parallel code-phase search is used due to its efficient searching speed, it is necessary to explore the advanced searching algorithm because of the extremely long period of P-code. Even just searching a segment of the P-code for several ms or 1 s, the searching task is still huge. A good acquisition algorithm is absolutely necessary by limiting the searching segment to several ms or 1 s, the searching task is still huge. A good acquisition algorithm is absolutely necessary.

In this chapter, new algorithms are introduced in this dissertation called direct average and overlap average methods. The performance of new algorithms is analyzed. The P-code property is studied. In addition, different acquisition techniques reported by researchers are compared.

### 3.2 P-Code Property

Each satellite uses unique P-codes to implement the CDMA technique. The autocorrelation function (Proakis, 2000) of a P-code is

$$R_{P}(\tau) = \int_{-\infty}^{\infty} P_{i}(t) P_{i}(t+\tau) dt \qquad (3.1)$$

where  $P_i$  is the P-code from the *ith* satellite and  $\tau$  is the time phase shift of the P-code.

The correlation peaks repeat after one P-code period of one week. The property of the autocorrelation function is used to synchronize the receiver-replicated code with the received signal. It is important that the cross-correlation of any two P-codes is minimum for any phase or Doppler shift over the entire code period. The ideal cross-correlation is defined by

$$R_{ij}(\tau) = \int_{-\infty}^{\infty} P_i(t) P_j(t+\tau) dt = 0$$

(3.2)

where  $P_i$  is the P-code from the ith satellite and  $P_j$  from the *jth* satellite and  $i \neq j$ .

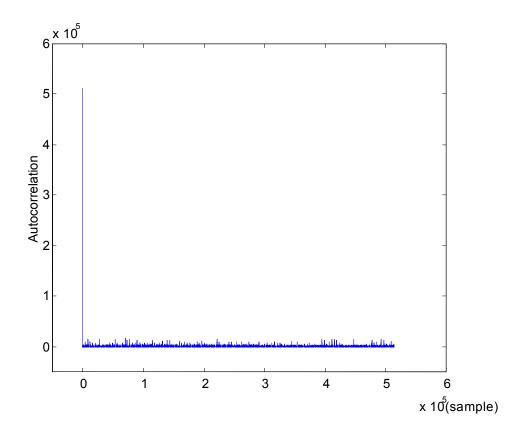

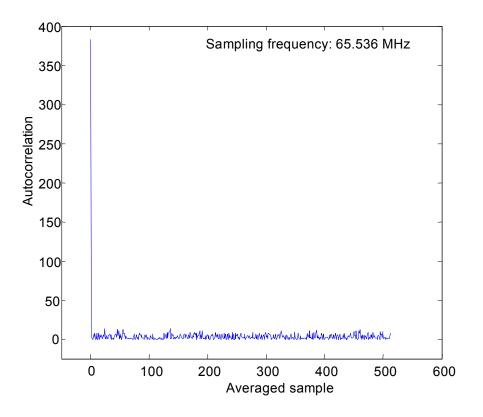

The autocorrelation plot in Figure 3.1 has a big peak value. The plot has relatively small side lobes.

Figure 3.1 P-code Autocorrelation over 50 ms

First, we define the correlation peak in Figure 3.1 as the largest correlation peak. Then a terminology of acquisition margin can be defined as the ratio of the largest correlation peak divided by the second largest correlation peak

$$ACQUISITION \ MARGIN = \frac{LARGEST \ CORRELATION \ PEAK}{SECOND \ LARGEST \ CORRELATION \ PEAK}$$

(3.3)

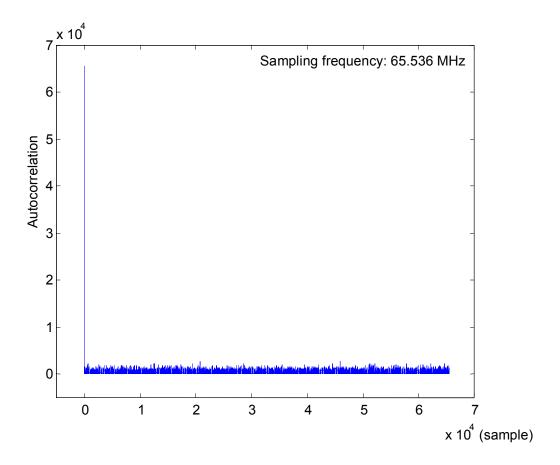

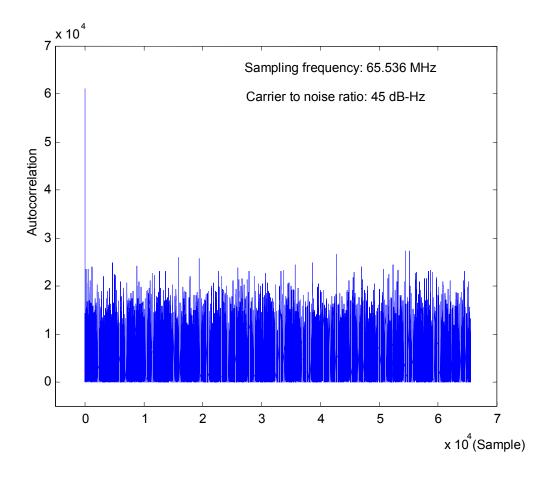

Of course, the bigger the acquisition margin value, the better. As for the long period P-code, a careful statistical analysis is necessary. Suppose the IF for P-code

acquisition is 12.5 MHz, and the GPS signal is up sampled to 65.536 MHz. The signal is finally converted to the base band. Figure 3.2 shows the autocorrelation result of the up sampled P-code in 1 ms and Figure 3.3 illustrates the acquisition margin distribution in 1

S.

Figure 3.2 Direct acquisition autocorrelation in 1 ms

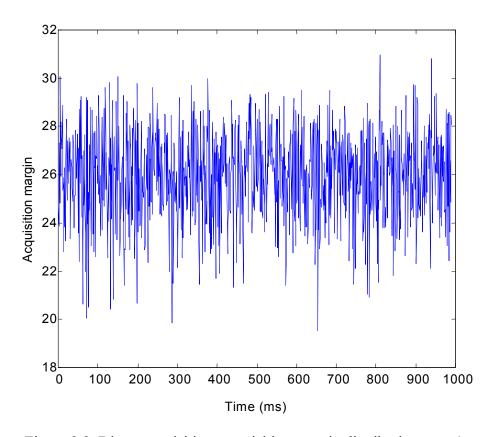

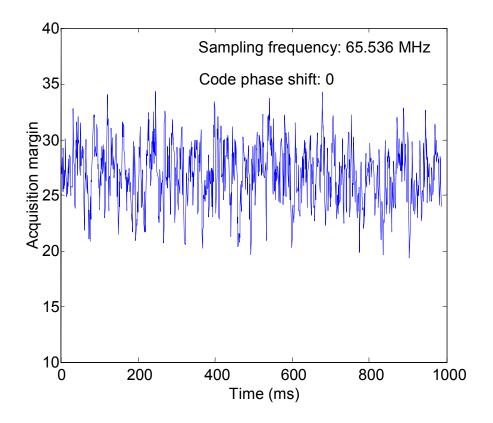

Figure 3.3 Direct acquisition: acquisition margin distribution over 1 s

In Figure 3.3, the mean value of the acquisition margin is 25.954 and the standard deviation is 1.841. So statistically, the acquisition margin value is stable when doing direct acquisition. From Figures 3.1, 3.2, and 3.3, it is interesting to observe that segments of the P-codes or up sampled P-codes are essentially orthogonal to each other. This is the basis for the direct average and the overlap average methods described later. This orthogonal property can be further tested if P-codes at any time interval of a week are available. One efficient way to generate the P-code will be described in Chapter 5.

### 3.3 FFT Search and Zero Padding

The linear correlation of periodic code can be performed by circularly shifting the replica code (Tsui, 2000). This resembles the circular convolution, which is a multiplication in the frequency domain. It can be expressed as

$$R[m] = \sum_{n=0}^{L-1} x[n] * x[n+m] = x[n] \otimes x[-n] = F^{-1} (F(x[n]) \bullet F(x[n])^*)$$

(3.4)

The Discrete Fourier Transform (DFT) and its inverse are used to calculate the correlation value R in the above equation. The incoming signal in-phase and quadrature components are used as the real and imaginary inputs when calculating the DFT. The result is multiplied by the complex conjugate of the DFT of the periodic code. The FFT algorithm (Brigham, 1974) is used to implement the DFT and the IDFT, which greatly reduce computation compared with the serial search method (van Nee, 1991).

For non-periodic codes, such as a segment of the P-code, the above calculation method won't give correct correlation results. A zero padding method is used to solve this problem.

First, construct signal A by taking the  $1^{st}$  ms of P-codes and pad the  $2^{nd}$  ms with zeros. Then, get signal B by taking the  $1^{st}$  and the  $2^{nd}$  ms of P-codes. Next, calculate correlation according to the following equation:

$$R[m] = F^{-1} \left( F(B[n]) \bullet F(A[n])^* \right)$$

(3.5)

Finally, the first half of the correlation results are kept while the second half are discarded. The final correlation results correspond to the correlation of the 1<sup>st</sup> ms P-codes with the 1<sup>st</sup> ms of incoming signal.

#### 3.4 Comparison of Different Acquisition Methods

The direct P-code acquisition in the time domain needs massive physical correlators in parallel for code search (Wolfert, 1998), which require a significant amount of resources for hardware implementation. Other attempts on direct P-code acquisition using a software radio algorithm are described below.

A. Circular correlation by partition and zero padding (Lin, 2000)

When doing circular correlation, two blocks of signals are taken. One block of reference is taken with another block padded by zeros. Then, take only the first half circular correlation results and discard the other half. Such design considers the almost non-periodic property of the P-code. In addition, the frequency search can be done by performing a FFT on the corresponding correlation results from several different blocks. The number of blocks used for frequency search corresponds to the frequency range covered.

B. Circular correlation by partition and superposition (Lin, 2000)

Similar to method A. Method B adds two neighboring blocks into one.

C. Non-coherent circular correlation by partition (Lin, 1998)

Similar to method A. Method C adds amplitude of correlation results from different blocks to find the initial code phase. Then, do FFT to find the carrier frequency.

D. Delay and multiplication (Lin, 1998)

Multiply the input signals with delayed signals. Do the same operation on local codes. Then correlate them to find the initial code phase. Next, do FFT to find frequency. Delay should be properly designed so that  $2\pi f_s \tau \approx \pi$ , where  $f_s$  is the sampling frequency, and  $\tau$  is the time delay.

E. Extended replica folding (Yang, 1999 and Yang 2000)

First, in order to implement Doppler removal, the incoming signal spectrum is shifted by a given number of frequency bins along the frequency axis. Then do circular correlation with a locally extended replica folded reference, which covers the entire time uncertainty interval. At last, the folded correlations are coherently integrated over time with several consecutive incoming signal segments in the same way. A more detailed sequential block search technique is illustrated in other research (Yang, 2001).

Table 3.1 gives the performance comparison of different acquisition methods. As illustrated in Table 3.1, methods A~C need larger size FFT than method E for direct P-code acquisition, so they consume more hardware resources. Method D needs huge size FFT, so it is good for hardware design. Method E only uses small size FFT, but it requires a larger size of data.

| Speed          | A(1ms) | B(1ms) | C(1ms) | D(10ms) | E(16ms) |

|----------------|--------|--------|--------|---------|---------|

| Multiplication | 7.517  | 3.781  | 0.478  | 1.665   | 0.26    |

| (×10^7)        |        |        |        |         |         |

| Addition       | 15.021 | 7.445  | 0.786  | 3.133   | 0.49    |

| (×10^7)        |        |        |        |         |         |

| Bandwidth      | 1kHz   | 1kHz   | 1kHz   | 100Hz   | 1kHz    |

| FFT size       | 8192   | 4096   | 4096   | 655360  | 1024    |

Table 3.1 Performance comparison of different acquisition methods

Table 3.2 compares different acquisition methods when acquisition probabilities are the same for all methods at around 90%. Methods A, C and D have better performance than methods B and E.

Table 3.2 C/No ratio for different acquisition methods with acquisition detectionprobability of around 90%

| Methods      | Α     | В     | С     | D      | Е      |  |

|--------------|-------|-------|-------|--------|--------|--|

|              | (1ms) | (1ms) | (1ms) | (10ms) | (16ms) |  |

| C/No (dB/Hz) | 41    | 44    | 42    | 41     | 47     |  |

From the above comparisons, when a large size FFT/IFFT hardware design is available, and also very good carrier to noise ratio performance is required, methods A and C are recommended for hardware design. When only a small size FFT/IFFT is available, also a fast acquisition is a major concern, method E is better for hardware design when GPS signals have a high carrier to noise ratio.

### 3.5 Direct Average Method

Due to the long period of the P-code, a fast correlation method has to be found. An average method can speed up the correlation procedure. First, let's see how the direct average method affects the autocorrelation function.

Step 1: There are 131,072 P-code samples in 2 ms if a sampling frequency is 65.536 MHz and suppose an IF of 12.5 MHz. Average every 128 samples to generate 1024 samples every 2 ms, and call them target 1.

Step 2: Pick up the first 512 points from target 1, pad them with 512 point zeros at the end to generate target 2 signals.

Step 3: Calculate the conjugate of 1024-point FFT for target 2 signals.

Step 4: Calculate 1024-point FFT for target 1 signals.

Step 5: Multiply the results from Step 3 and Step 4, and then do 1024-point IFFT.

Step 6: Select the first 512 elements from the results of Step 5, and discard the other 512 elements. The final results correspond to the autocorrelation function of the 1<sup>st</sup> ms P-code up samples.

Step 7: Shift the P-code samples by 65,536 samples, repeat Steps 1 to 6, get the autocorrelation function of the  $2^{nd}$  ms.

Step 8: Similarly, get all autocorrelation functions of 15 ms and sum all correlation results in 15 ms.

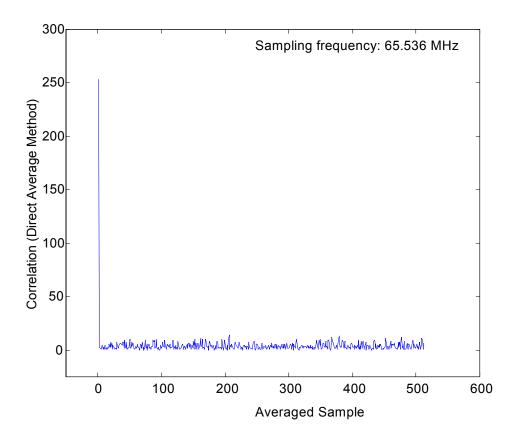

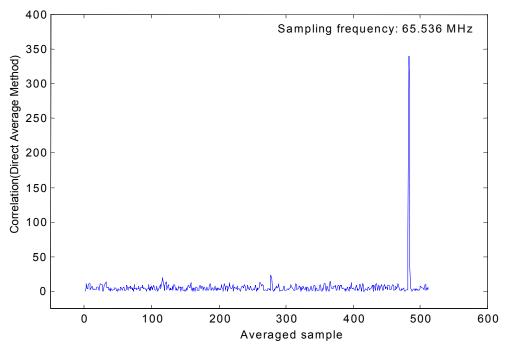

Figure 3.4 shows that averaged chunks of data are basically orthogonal to each other.

Figure 3.4 Direct average autocorrelation result for P-code

In Figure 3.5, the acquisition margin for a well aligned signal and reference over 1 s is calculated. The mean value is around 26.882 and the variation value is 2.676. As a result, the direct average method is statistically valid for segments of P-code up samples in different milliseconds. Compared with the direct acquisition margin, which is equal to 25.954 when no average is used for acquisition, the direct average method has the similar acquisition margin. This is the case when there is no noise added. However, the direct average method avoids using the extremely large size FFT hardware for 50 ms samples.

Figure 3.5 Direct average method: acquisition margin distribution over 1s

Based on the results from Figure 3.4 and Figure 3.5, the direct average method can be used to reduce the time for acquiring P-code signals. The block processing technique (Haag, 1999) can be used to suppress noise by processing correlations in several blocks and then adding them together. After GPS signals are demodulated, the further acquisition procedure is given as follows:

Step 1 to Step 8 are similar to those described above for autocorrelation calculation except the target 1 reference is locally generated P-code samples rather than incoming signals.

Step 9: If a correlation peak is not detected, shift P-code samples by another 1 ms as reference. Repeat Steps 1 to 9 until a correlation peak is acquired.

Step 10: If a correlation peak is detected at location m, the peak location has a code phase resolution of 128 samples. If a more accurate peak location is needed, go to step 11.

Step 11: Shift the demodulated GPS signals by (m-1)\*128 samples. Then use the first 1024 signal samples to do a 1024-point FFT.

Step 12: Take the first 512 samples from the reference and pad them with 512 zeros. Obtain the conjugate of a 1024-point FFT for this new reference.

Step 13: Multiply results from Steps 11 and 12, and then do a 1024-point IFFT.

Step 14: Select the first 512 elements from the results of Step 13, and discard the other 128 elements. The final results should show the correlation peak location at n. Then use (m\*128+n-128) to get the exact sample location.

Example 1: GPS signals are 42 samples in advance of reference. This example is given to show the simulation results using the above acquisition procedure.

Figure 3.6 Direct average acquisition example

Figure 3.6 is a result of Step 1 to Step 8 in the above acquisition procedures using the direct average method. The acquisition correlation peak is located in the zero shift position, which is within the 128-sample resolution.

The result of Step 9 to Step 12 is illustrated in Figure 3.7. The correlation peak is located at the 86-sample shift position. Since (0\*128+86-128) is equal to -42, the acquired location is 42 samples in advance of the reference.

Figure 3.7 Correlation resolution improvement

### 3.6 Effect of Code Phase Shift

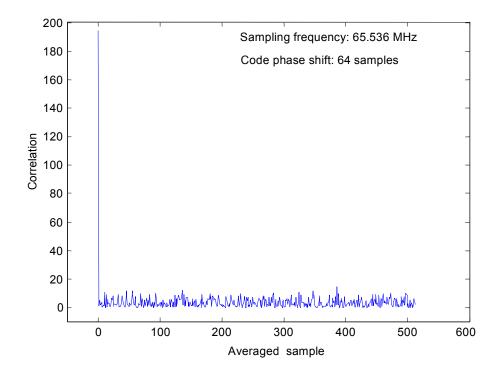

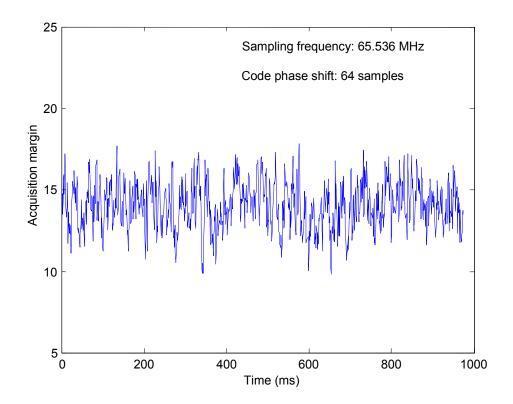

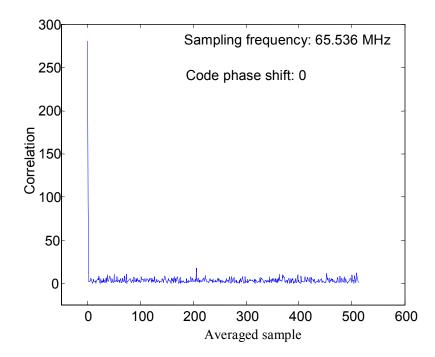

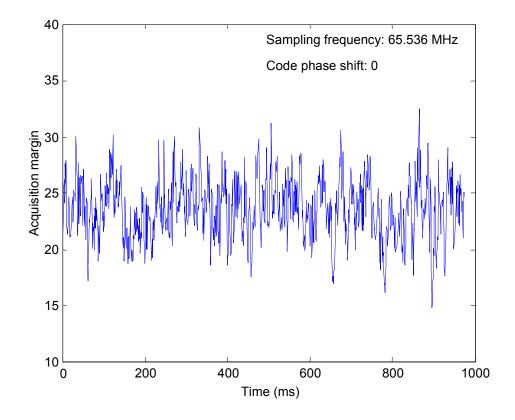

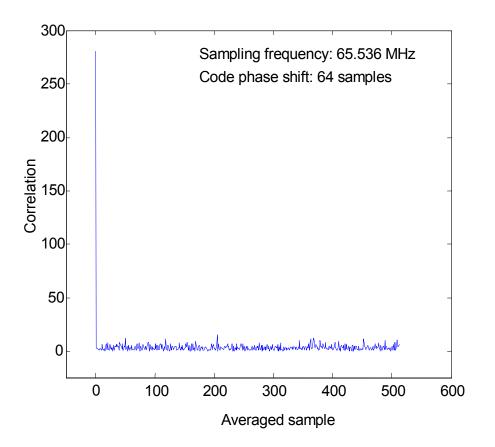

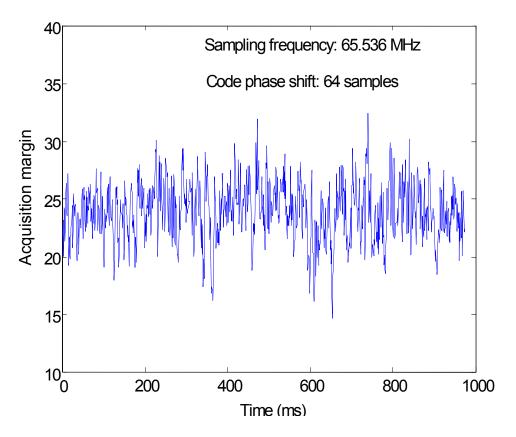

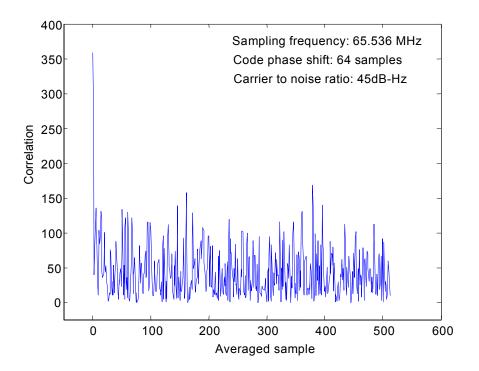

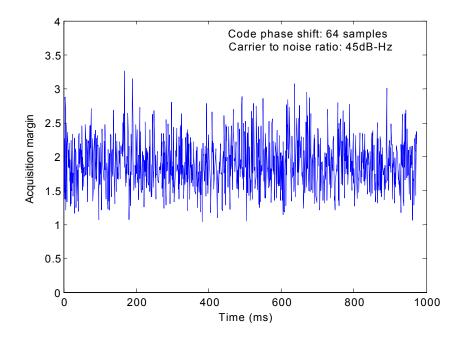

The acquisition results are optimum when the reference samples have a zero code phase shift relative to the incoming signal samples. Obviously, it is very important to study how the code phase shift affects the maximum correlation peak value and the acquisition margin. Figures 3.8 and 3.9 correspond to a code phase shift of 64 samples.

Figure 3.8 Direct average method: correlation results with a code phase shift of 64 samples

Figure 3.9 Direct average method: acquisition margin distribution over 1s with a code phase shift of 64 samples

Compared with Figures 3.4 and 3.5, the correlation peak value and the acquisition margin decrease a lot as can be observed from Figures 3.8 and 3.9. The mean of Figure 3.9 is 14.042, and the standard deviation is 1.424.

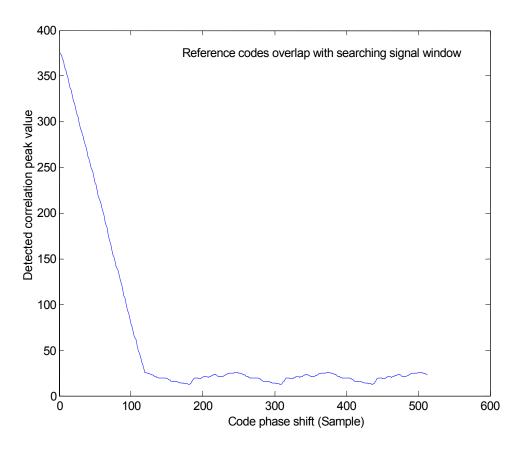

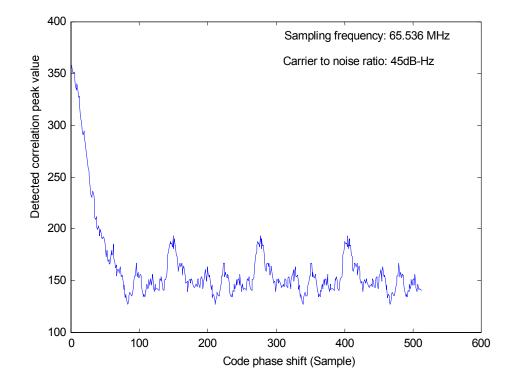

Figure 3.10 is a two dimensional plot of the relation between the correlation peak value and the code phase shift in samples. The correlation peak decreases almost linearly within the 128-sample shift. When there is a shift of 64 samples, there is almost a half correlation peak value loss, or a 3 dB loss.

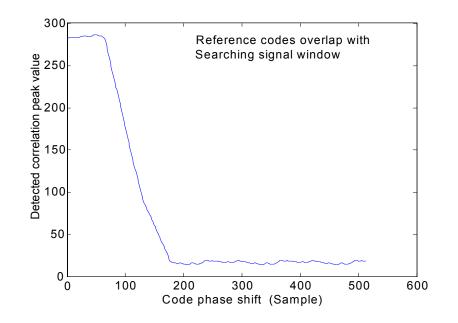

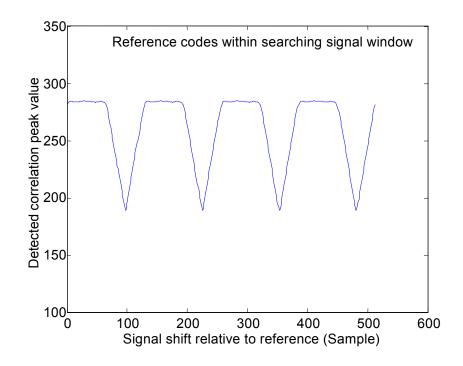

Figure 3.10 Direct average method: detected correlation peak value change, case 1

The triangle in Figure 3.11 repeats for 1 ms with a cycle of 128 samples, which means that if reference codes are hidden inside the first half of the 2 ms searching window, correlation peak can always detected.

Figure 3.11 Direct average method: detected correlation peak value change, case 2

In order to make up the correlation energy loss in the dip region in the above figures, a new algorithm is presented in the next section to improve the acquisition performance.

### 3.7 Overlap Average Method

Since the detected correlation peak value changes almost linearly within the 128sample shift range, a linear combination algorithm may gain more correlation energy and make Figures 3.10 and 3.11 as flat as possible. Those are the goals of the overlap average method. The basic operation of this method is similar to the direct average method except the reference is different. Here, a second reference is used which is overlapped with the old reference by 64 P-code up samples. Averaging two reference codes will produce the new reference used as the first experiment in the overlap average method. In Figures 3.12 to 3.15, the correlation value and the statistical acquisition margin distribution are calculated without a code phase shift and with a code phase shift of 64 samples.

Figure 3.12 Correlation result using overlap average method

When there is no code phase shift, the optimum correlation value and acquisition margin value are achieved. Figures 3.13 and 3.14 show that the overlap average method

has a small decrease of these values. The mean of Figure 3.13 is 23.596, and the standard deviation is 2.653.

Figure 3.13 Statistical acquisition margin result for overlap average method

The advantage of the overlap average method shows up when there is a code phase shift. Figure 3.14 illustrates a worse case with a code phase shift of 64 P-code up samples. The correlation value remains similar to that without the code phase shift.

Figure 3.14 Correlation result for overlap average method with a code phase shift of 64 samples

In Figure 3.15 the acquisition margin in case of a code phase shift of 64 P-code up samples remains similar to the results without the code phase shift. The energy compensation is around 2 to 3 dB compared with the direct average method. The mean of Figure 3.15 is 23.885, and the standard deviation is 2.487.

Figure 3.15 Statistical acquisition margin result for overlap average method with a code phase shift of 64 samples

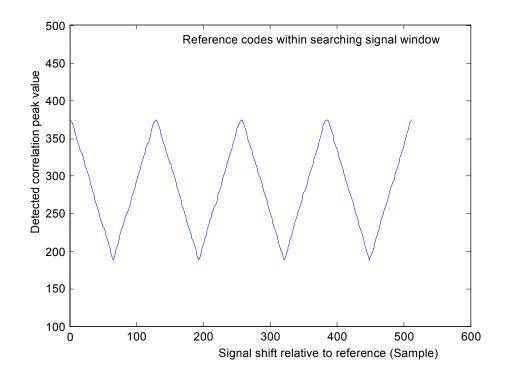

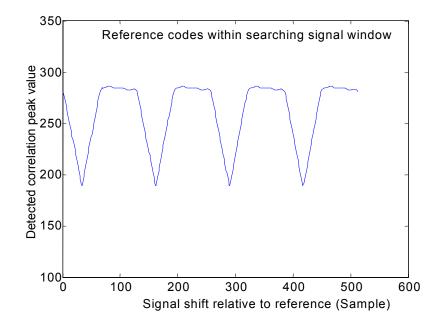

In addition, the detected correlation peak changes are shown in Figures 3.16 and 3.17. As can be seen, the maximum correlation value curve becomes relatively flat and correlation energy loss, in the worse case, is decreased. The flat parts in Figures 3.16 and 3.17 prove the linear combination really works. In order to find out why there are still dips in Figure 3.17, it's necessary to explore the correlation peak location detection difference by using two different references.

Figure 3.16 Overlap average method: two reference overlap, case 1

Figure 3.17 Overlap average method: two reference overlap, case 2

Suppose grouping the signal by 128 samples. In Figure 3.18, when the code phase shift is between 0 to 64 samples, reference 1 detects the correlation peak location in the 1st group, but reference 2 indicates the 2<sup>nd</sup> group. As a result, two correlation peaks don't have a chance to be added up. That's why dips happen in Figure 3.16. However, when the code phase shift is between 64 to 128 samples, two references detect the same correlation peak location so that the two correlation peaks are summed up into a bigger value, which results in the flat part in Figure 3.17.

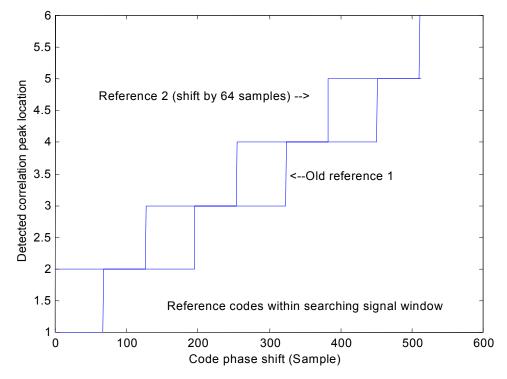

Figure 3.18 Peak correlation location detection difference using two different references

Theoretically, since actually we only utilize the positive part of linear correlation peak curve property, the negative part is not used. We can also use the cycling property showed in Figure 3.11. Accordingly, a new procedure is described next.

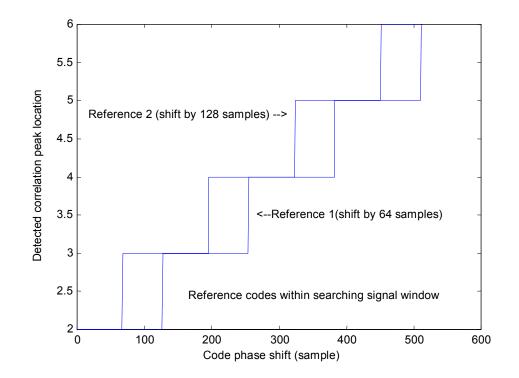

First, let's take two new references. One has a shift of 64 samples, and another one has a shift of 128 samples. These two references will shift the pattern in Figure 3.18 right by 64 samples as illustrated in Figure 3.19. Next combine these two into a new reference, and then the corresponding curve in Figure 3.17 will also shift right by 64 samples to generate a new curve showed in Figure 3.20.

Figure 3.19 Peak correlation location detection pattern change

Figure 3.20 Overlap average method: two reference overlap case 3

Suppose the reference is within the signal searching window. Then the correlation peak value satisfies the following equation:

$$correlation \ peak = \max \left\{ \sum [(x_m + x_{m+128})^* (y_0 + y_{64} + y_{64} + y_{128})/4] \right\}$$

=

$$\max \left\{ \sum [x_m y_0 + 2^* (x_m y_{64} + x_{m+128} y_{64}) + x_m y_{128} + x_{m+128} y_0 + x_{m+128} y_{128}]/4 \right\}$$

=

$$\max \left\{ \sum [(x_m y_0 + x_m y_{128}) + 2^* (x_m y_{64} + x_{m+128} y_{64}) + (x_{m+128} y_0 + x_{m+128} y_{128})]/4 \right\}$$

=

$$\max \left\{ \sum [x_0 y_0 + 2^* x_0 y_0 + x_0 y_0]/4 \right\}$$

=

$$\max \left\{ \sum [x_0 y_0 + 2^* x_0 y_0 + x_0 y_0]/4 \right\}$$

(3.6)

where  $x_0$  is the original signal without any shift,  $x_m$  and  $x_{m+128}$  are the signals with a shift of *m* samples and (m+128) samples;  $y_0$ ,  $y_{64}$  and  $y_{128}$  are the references with zero shift, 64-sample shift and 128-sample shift relative to signal  $x_0$  respectively.

There are pairs in Equation 3.6, which complement each other on correlation peak values. These pairs are  $(x_m y_0, x_m y_{128}), (x_m y_{64}, x_{m+128} y_{64}), and (x_{m+128} y_0, x_{m+128} y_{128})$ . As a result, the maximum correlation peak value has no relation with the shift variable *m* and it should be the maximum correlation peak value. The correlation peak curve in Figure 3.21 has values a little less than the maximum value because the linear relationship described before is not perfect.

Figure 3.21 Overlap average method by using three references

Actually the final overlap average method uses three references. The first reference has no code phase shift, the second has a code phase shift of 64 samples, and the third has a code phase shift of 128 samples. Add one copy of the first reference, two copies of the second reference, and one copy of the third reference, and then average them to get a new reference. Also add incoming signals with signals having 128-sample code phase shift to obtain new signals. At last, correlate new signals with the new reference. In this way, almost optimum acquisition performance can be achieved.

#### 3.8 Noise Effect

The above simulation results are ideal since noise is not considered. Table 3.3 lists characteristics of different acquisition schemes without noise added. Case 1 corresponds to the best situation and case 2 to the worse situation.

First, the direct acquisition has a big mean acquisition margin. But it needs a huge size FFT, which is almost impossible in the hardware design currently. Second, in the best case, the direct average method has a big correlation peak and mean acquisition margin. However, when there is a relative code phase shift such as 64 samples, the correlation peak value decreases a lot and the 2<sup>nd</sup> peak value doesn't change. As a result, the mean acquisition margin becomes much lower. Compared with the direct average method, the overlap average method is not so sensitive to the code phase shift. In

conclusion, the overlap average method has overall good performance in different situations. Also a small size FFT is available by averaging and it is good for hardware implementation.

| *Case 1: no shift         |           | No Noise    |                |         |                 |         |  |  |

|---------------------------|-----------|-------------|----------------|---------|-----------------|---------|--|--|

| *Case 2: a relative shift |           | Direct      | Direct Average |         | Overlap Average |         |  |  |

| of 64 samples             |           |             | Case 1         | Case 2  | Case 1          | Case 2  |  |  |

| Correlation               | True Peak | 6.5536*10^4 | 382.848        | 194.477 | 288.662         | 285.549 |  |  |

| (1 ms)                    | Second    | 2.6500*10^3 | 13.919         | 14.824  | 13.452          | 13.178  |  |  |

|                           | Peak      |             |                |         |                 |         |  |  |

| Acquisition               | Mean      | 25.954      | 26.882         | 14.042  | 23.596          | 23.885  |  |  |

| Margin                    | Standard  | 1.841       | 2.676          | 1.424   | 2.653           | 2.487   |  |  |

|                           | Deviation |             |                |         |                 |         |  |  |

Table 3.3

Correlation and acquisition margin characteristics using different schemes without noise

In the real world, noise always exists in GPS signals. So it is important to analyze the above algorithms with noise added.

In Figure 3.22, when noise is added, the noise floor increases a lot in direct acquisition.

Figure 3.22 Noise effect on direct autocorrelation result of P-code up samples over 1 ms

In Figure 3.23, when noise is added, the mean acquisition margin decreases.

Figure 3.23 Direct acquisition: noise effect on acquisition margin result

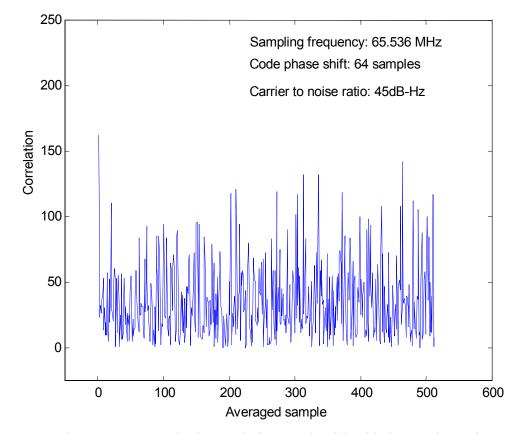

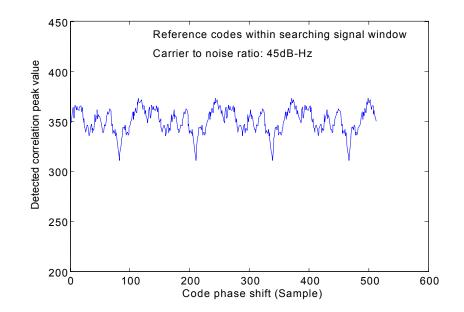

As illustrated in Figure 3.24, the direct average method doesn't perform well when there's a relative big code phase shift such as 64 samples when noise is added. The detected correlation peak value decreases a lot.

Figure 3.24 Direct average method: correlation result with added Gaussian noise

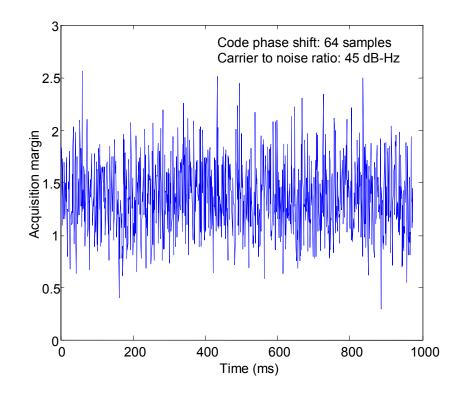

When there's a relative big code phase shift such as 64 samples, Figure 3.25 shows the acquisition margin decrease a lot in case of added noise.

Figure 3.25 Direct average method: noise effect on acquisition margin

Figure 3.26 Direct average method: noise effect on detected correlation peak change with code phase shift

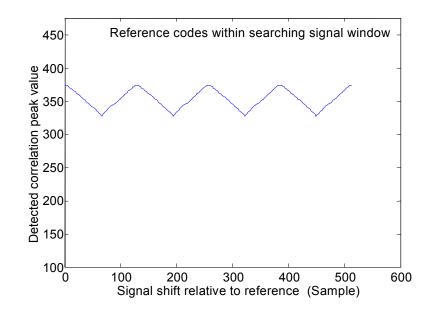

When noise is added, the overlap average method doesn't decrease detected correlation peak and acquisition margin much in Figures 3.27~3.29. So it performs much better than the direct average method. If reference codes are within the searching signal window, the detected correlation peak value curve keeps relatively flat with different code shifts.

Figure 3.27 Overlap average method: correlation result with added Gaussian noise

Figure 3.28 Overlap average method: noise effect on acquisition margin

Figure 3.29 Overlap average method: noise effect on detected correlation peak value

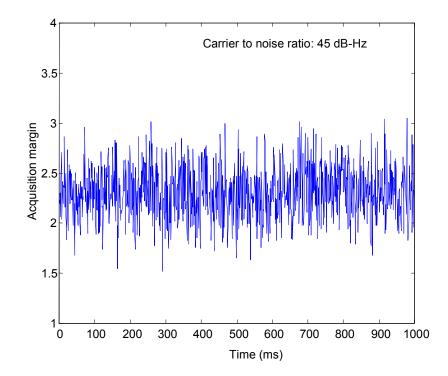

Table 3.4 quantifies the correlation and acquisition margin using different acquisition schemes when noise is added.

| *Case 1: no shift |                           | Added Gaussian Noise (carrier to noise ratio=45dB-Hz) |                |        |                 |         |

|-------------------|---------------------------|-------------------------------------------------------|----------------|--------|-----------------|---------|

| *Case 2: a :      | *Case 2: a relative shift |                                                       | Direct Average |        | Overlap Average |         |

| of 64 sample      | of 64 samples             |                                                       | Case 1         | Case 2 | Case 1          | Case 2  |

| Correlation       | True Peak                 | 6.125 *10^4                                           | 358.04         | 162.18 | 350.258         | 358.696 |

|                   | Second                    | 2.726 *10^4                                           | 140.89         | 142.00 | 162.963         | 168.395 |

|                   | Peak                      |                                                       |                |        |                 |         |

| Acquisition       | Mean                      | 2.308                                                 | 2.722          | 1.364  | 2.186           | 1.897   |

| Margin            | Standard                  | 0.255                                                 | 0.409          | 0.341  | 0.409           | 0.366   |

|                   | Deviation                 |                                                       |                |        |                 |         |

Table 3.4 Correlation and acquisition margin characteristics using different schemes with added noise

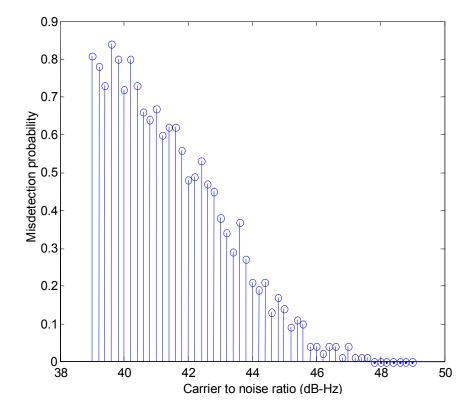

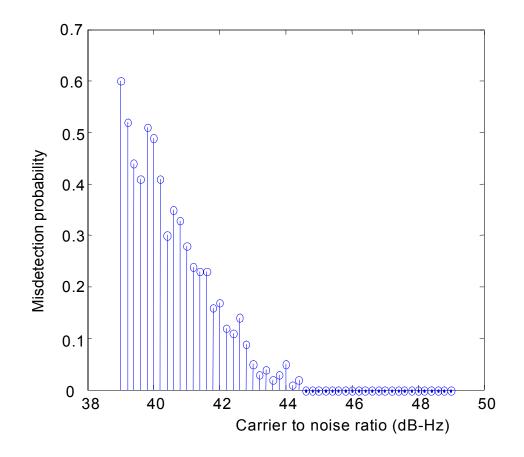

Furthermore, 16 ms signals are taken to do acquisition using the direct average and the overlap average method with the same misdetection probability but a different carrier to noise ratio. The direct average method requires around a 3 dB-Hz less carrier to noise ratio compared with the overlap average method according to Figures 3.30 and 3.31.

In these figures, although the carrier to noise ratio using both methods is relatively high, these two methods have the advantages of reducing the time for the code phase search and using a small size FFT. So there is a tradeoff between the code phase search speed and the carrier to noise ratio.

Figure 3.30 Direct average method: misdetection probability with different carrier to noise ratio when the signal code phase shift is 64 samples

Figure 3.31 Overlap average method: misdetection probability with different carrier to noise ratio when the signal code phase shift is 64 samples

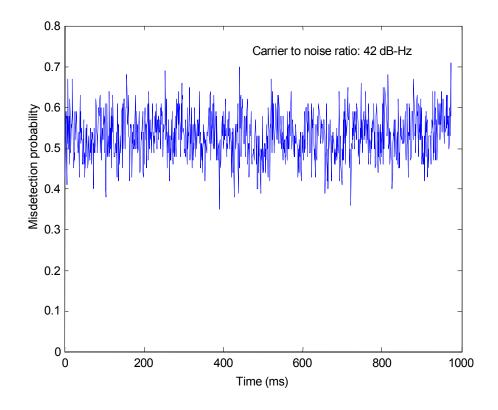

A statistical analysis was made to compare two acquisition methods. A study of the misdetection probability statistical distribution in 1 s using the direct average method illustrated in Figure 3.32 indicates that the midsection probability has a mean of 0.5318 and a standard deviation of 0.055 when the carrier to noise ratio is equal to 42 dB-Hz.

Figure 3.32 Direct average method misdetection probability distribution in 1 s with carrier to noise ratio equal to 42 dB-Hz

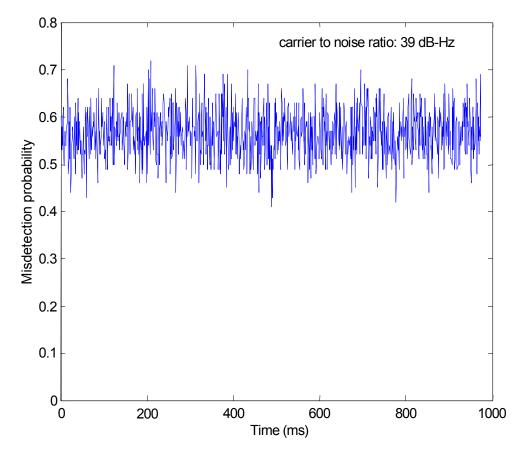

In case of using the overlap average method illustrated in Figure 3.33, the misdetection probability has a mean of 0.5658 and a standard deviation of 0.0512 when the carrier to noise ratio is equal to 39 dB-Hz. So with the almost the same misdetection probability, the overlap average method has a gain of around a 3 dB-Hz carrier to noise ratio higher than the direct average method statistically. In conclusion, the overlap average method has overlap with or without noise added.

Figure 3.33 Overlap average method misdetection probability distribution in 1 s with carrier to noise ratio equal to 39 dB-Hz

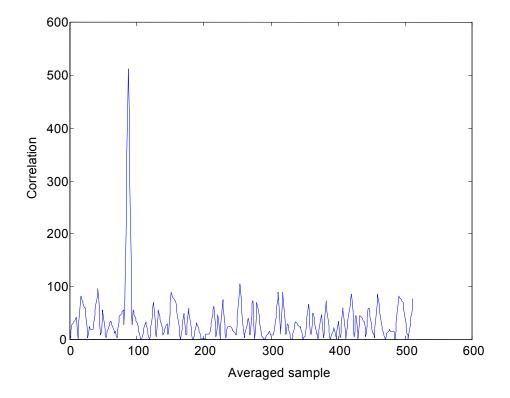

# 3.9 Example

Example: Suppose reference codes are within 2 ms searching signal window. The relative code phase shift between signal and reference is 61,746 samples.

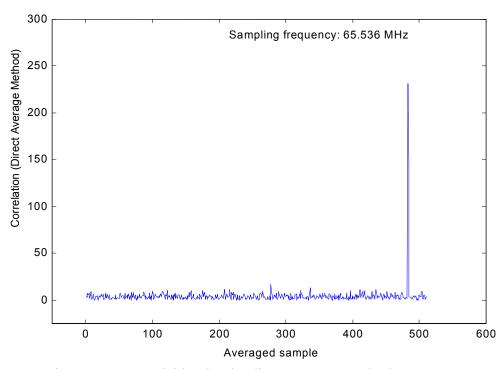

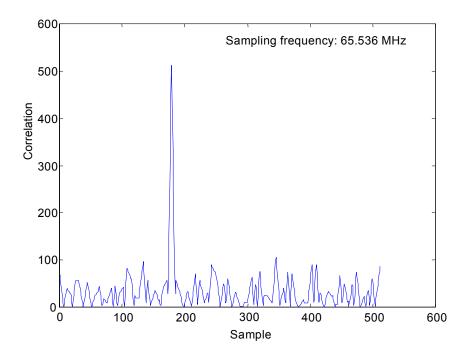

Both direct average and overlap average methods detect the correlation peak at a code phase shift equal to 482 in Figures 3.34 and 3.35. The result has a resolution equal to 128 samples. Searching at least 256 samples near the correlation peak location can refine the resolution. Since a 1024-point FFT is used, 1024 samples are taken for the searching purpose.

Figure 3.34 Acquisition by the direct average method

Figure 3.35 Acquisition by the overlap average method

Shift 2ms-signals by 481\*128 samples. Then take the first 1024 points to do a 1024-point FFT. Next take the first 512 points from reference and pad them with 512 zeros to get a new reference. Use the new reference to get the conjugate of the 1024-point FFT, and multiply them with previous 1024-point FFT results. Then do a 1024-point IFFT. At last, keep the first 512 results from the IFFT and discard the other half.

The final results are illustrated in Figure 3.36. The peak location has a shift of 178 samples.

Figure 3.36 Resolution improvement by correlating 128 samples

As a result, the final shift is located at 482\*128+178-128 = 61,746 samples in advance of reference.

# 3.10 Conclusion

The P-code or even segments of the P-code have good autocorrelation and crosscorrelation properties. Because a segment of the P-code is considered as nonperiodic, its correlation function is computed by the FFT search and zero padding method. Many reported direct P-code acquisition algorithms listed in this dissertation need a large size FFT/IFFT, which requires large hardware resources and adds hardware design complexity. In this chapter, the direct average method is proposed to reduce the direct P-code acquisition code phase searching time using 1024-point FFT/IFFT. This method is based on the symmetrical linear P-code correlation curve discovered by using averaging.