# ANALOG AND MIXED-SIGNAL

## **TEST AND FAULT DIAGNOSIS**

A Dissertation Presented to

The Faculty of the

Fritz J. and Dolores H. Russ College of Engineering and Technology

Ohio University

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy

by

Dong Liu

August, 2003

THIS DISSERTATION ENTITLED

# "ANALOG AND MIXED-SIGNAL TEST AND FAULT DIAGNOSIS"

by

Dong Liu

has been approved

for the School of Electrical Engineering and Computer Science

and the Russ College of Engineering and Technology

Janusz A. Starzyk, Professor

Dennis Irwin, Dean Fritz J. and Dolores H. Russ College of Engineering and Technology

#### ACKNOWLEDGEMENTS

I want to thank all the persons who help me finishing this dissertation. Although I cannot list them all within this small page, I do want to express my deepest gratitude to some of them directly involved in my Ph. D research.

I would like to sincerely thank my advisor, Prof. Janusz A. Starzyk, for his guidance, support and encouragement. His insight and knowledge in analog testing were the greatest benefits to this dissertation work.

Many sincere thanks are due to my dissertation committee members, Prof. Robert A. Curtis, Prof. Herman W. Hill, Prof. Henryk J. Lozykowski and Prof. Sergiu Aizicovici, for their time, instructions, and patience during my dissertation research.

I am also greatly thankful to Mr. Genard N. Stenbakken for his instructions when I was working at NIST. This dissertation could not be finished without his knowledge, skill, and support.

I am pleased to acknowledge the financial support from NIST and Stocker Research Associateship at College of Engineering, Ohio University during my research work.

Finally, special thanks to my wife, Ying, and my parents, for their support and encouragement all of these years.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTSiii                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIST OF TABLES                                                                                                                                                                                                                                                                    |

| LIST OF ILLUSTRATIONSvii                                                                                                                                                                                                                                                          |

| LIST OF ABBREVIATIONSix                                                                                                                                                                                                                                                           |

| CHAPTER 1 INTRODUCTION1                                                                                                                                                                                                                                                           |

| 1.1.History21.2.Significance31.4.Classification71.5.Problems in Analog Test and Fault Diagnosis11                                                                                                                                                                                 |

| CHAPTER 2 FAULT VERIFICATION FOR ACCURATE COMPUTATION15                                                                                                                                                                                                                           |

| 2.1. Ambiguity and Verification15                                                                                                                                                                                                                                                 |

| 2.2. Woodbury Fault Verification Technique                                                                                                                                                                                                                                        |

| 2.3. Fault Diagnosis in Woodbury Fault Verification Technique262.3.1. Fault Detection.262.3.2. Fault Identification.262.3.2.1. Gaussian Elimination.292.3.2.2. QR Factorization.302.3.2.3. Element Swapping332.3.3. Parameter Evaluation.362.3.4. Algorithm for Fault Diagnosis37 |

| 2.4. Example Circuits                                                                                                                                                                                                                                                             |

| 2.5. Generalized Applications462.5.1. Nominal Fault Verification Technique472.5.2. Adjoint Fault Verification Technique512.5.3. Tableau Fault Verification Technique532.5.4. Comparisons of Four Fault Verification Techniques61                                                  |

| 2.6. Conclusions                                                                                                                                                                                                                                                                  |

| CHAPTER 3 LARGE SCALE SYSTEM DECOMPOSITION                                                                                                                                                                                                                                        |

| 3.1.  | Complexity, Accessibility and Decomposition            | 65  |  |  |

|-------|--------------------------------------------------------|-----|--|--|

| 3.2.  |                                                        |     |  |  |

| 3.3.  | · · · ·                                                |     |  |  |

| 3.4.  |                                                        |     |  |  |

| 3.5.  | Conclusion                                             |     |  |  |

| СНАР  | TER 4 LOCATING CATASTROPHIC FAULTS                     |     |  |  |

| 01111 |                                                        |     |  |  |

| 4.1.  | Stuck Fault Model and Catastrophic Fault Location      | 81  |  |  |

| 4.2.  | Application of Stuck-at, Bridging and Stuck-Open Model |     |  |  |

| 4.3.  | Stuck Fault Location                                   |     |  |  |

| 4.4.  | Example Circuit                                        |     |  |  |

| 4.5.  | Conclusions                                            |     |  |  |

| CHAP  | TER 5 CONCLUSIONS                                      | 96  |  |  |

| 5.1.  | Summary of the Research Results                        | 96  |  |  |

| 5.2.  | Recommended Future Work                                |     |  |  |

| REFE  | RENCES                                                 | 100 |  |  |

| ABST  | RACT                                                   |     |  |  |

## LIST OF TABLES

| Table 1.1 Cost of manufacturing testing in 2000AD          | 13 |

|------------------------------------------------------------|----|

| Table 1.2 Current and future development of IC fabrication | 14 |

| Table 2.1 Comparison among Four verification techniques    | 61 |

## LIST OF FIGURES

| Figure 1.1 Classification of analog test and fault diagnosis [2]                    | 9 |

|-------------------------------------------------------------------------------------|---|

| Figure 1.2 Diagram of analog and mixed-signal system1                               | 1 |

| Figure 1.3 Diagram of analog and mixed-signal test and fault diagnosis              | 2 |

| Figure 2.1 Model of parameter location                                              | 9 |

| Figure 2.2 Complexity comparison: comprehensive search vs. ambiguity group locating |   |

|                                                                                     | 5 |

| Figure 2.3 Algorithm for fault verification technique [39]                          | 8 |

| Figure 2.4 Example circuit in [21]40                                                | 0 |

| Figure 2.5 Active low pass analog filter44                                          | 4 |

| Figure 2.6 Model for operational amplifier44                                        | 4 |

| Figure 2.7 Resistive network example59                                              | 9 |

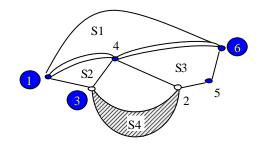

| Figure 3.1 Illustration of a common node60                                          | 8 |

| Figure 3.2 Decomposed system for example 3.17                                       | 1 |

| Figure 3.3 Fault-free nodes location for example 3.2                                | 5 |

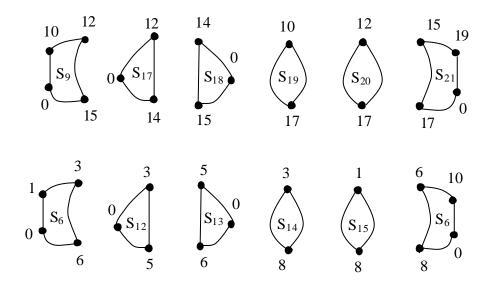

| Figure 3.4 Active low-pass filter                                                   | 7 |

| Figure 3.5 Decomposed subsystems78                                                  | 8 |

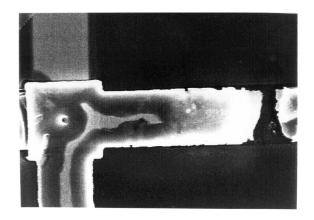

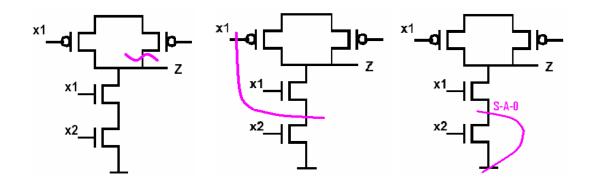

| Figure 4.1 Broken signal line in analog manufacturing82                             | 2 |

| Figure 4.2 Open fault, bridging fault, and short-to-ground fault                    | 2 |

| Figure 4.3 Bridging fault                                                           | 4 |

| Figure 4.4 Stuck-at-0 fault                                                         | 4 |

| Figure 4.5 Stuck-open fault                                                          | 84 |

|--------------------------------------------------------------------------------------|----|

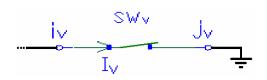

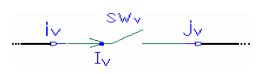

| Figure 4.6 A model of ideal open switch                                              | 85 |

| Figure 4.7 Modified coefficient matrix with an inserted switch                       | 86 |

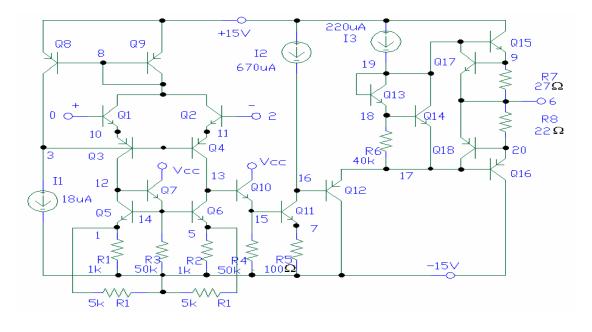

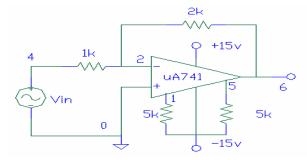

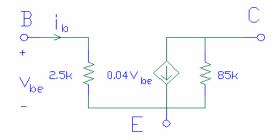

| Figure 4.8 A overall sche matic of the Fairchild <b>m</b> A741 operational amplifier | 93 |

| Figure 4.9 Negative feedback configuration of <b>m</b> A741                          | 93 |

| Figure 4.10 The small signal model of BJT                                            | 93 |

viii

### LIST OF ABBREVIATIONS

- ADC Analog-Digital-Converter AI Artificial Intelligence ATE Automated Test Equipment BIST Built-in-Self-Test CDF Cumulative Density Function CSL Cumulative-Sum-Limited CUT Circuit-Under-Test DAC Digital-Analog-Converter DC Direct Current DFT Design-for-Testability GPS Global Positioning System IC **Integration Circuit** ICDF Inverse Cumulative Density Function IT Information Technology KCL Kirchhoff Current Law NIST National Institute of Standards and Technology PDF **Probability Density Function** PLL Phase-Locked-Loop RF Radio Frequency PME Phase-Maximum-Error RMS Root-Mean-Square S&H Sample & Hold SAT Simulation-After-Test SBT Simulation-Before-Test SoC System-on-Chip

- TTM Time-to-Market

TTV Time-to-Volume

## VLSI Very Large Scale Integration circuits

## CHAPTER 1 INTRODUCTION

Analog and mixed-signal test and fault diagnosis play an essential role in circuit design, device production, and instrumentation maintenance. It is the most challenging area in electronics test for academic researchers and industrial engineers [1-4]. The purpose of test and fault diagnosis is to obtain useful information about the Circuit-Under-Test (CUT) based on limited excitations and measurements on CUT. The resulting information benefits not only testing engineers and instrumentation operators, but also design engineers and field engineers who could correct their design or manufacturing process, thus reducing Time-To-Market (TTM) and Time-To-Volume (TTV), increasing production yield, and reducing system cost. Generally speaking, analog and mixed-signal test and fault diagnosis consist of three tasks. The first task is **fault detection** which is to check if the CUT is faulty by comparing its responses with responses of a fault-free circuit (gold circuit) under the same excitations. This task is a go/not go operation, which is usually called test in industry. In this task, excitations and measurements as few as possible are required to cover as many as possible faults. If the CUT is judged faulty, the second task is **fault location** to find out where the faulty parameters are within this faulty circuit. This task is dominant for analog and mixed-signal test and fault diagnosis, and distinct methodologies were developed to address this problem. Based on the results of fault location, the final task is **parameter evaluation** to compute how much the faulty parameters are deviated from their nominal values, and how much deviation can be observed among other circuit parameters such as nodal voltages and branch currents.

#### 1.1. History

Analog and mixed-signal test and fault diagnosis always accompany design, manufacture, and maintenance of analog circuits. In the era of discrete analog components, the task of test and fault diagnosis is simple and easy, mostly depending upon the testing engineers' detailed knowledge about analog circuit's operational characteristics and their experiences in analog test and fault diagnosis. In the 1960s, research on this topic was rare, not a systematic exploration With volume production and widespread application of commercial analog integration circuits (IC), research on analog and mixed-signal test and fault diagnosis became an important area in the 1970s. Numerous methodologies have been designed to meet distinct requirements for analog circuits' specification, model, function, and structure. Several good periodical reviews on this topic appeared in 1979 [1], 1985 [2], 1991 [3] and 1998 [4], respectively.

Recently, with astounding achievements of semiconductor integration and computer-aided software technologies, there is an urgent need for effective, highly automated, systematic solutions to analog and mixed-signal test and fault diagnosis. It is not surprising to observe that there is a steady growth in the number of journal articles and conference/workshop papers addressing problems in analog test and fault diagnosis. More and more professional workshops and special journal issues are also devoted to this area. The papers [5-30] are examples of research efforts since 1997. Review of these papers is in later chapter of this dissertation.

#### 1.2. Significance

After researchers and engineers have paid more attention to digital test during the past three decades, the ir focus recently switches more to analog and mixed-signal test and fault diagnosis. The driving forces behind this change of focus came from economic considerations and modern technology advances. Economic consideration is the most important factor influencing the motivations for analog and mixed-signal test and fault diagnosis. Like digital test, test cost is a large fraction of the whole cost for design, manufacture and maintenance. Without effective, systematic techniques for analog test and diagnosis, analog test cost could be a dominant fraction of test cost for the whole system. This is even true when analog parts only occup y a small portion of mixed-signal system. Eventually, disproportionate product failure and yield losses will result. Simultaneously, more and more strict requirements to reduce time-to-market and time-to-volume also urge the development of fast and efficient test algorithms to reduce test time. Driven by these economic considerations, mostly from industry, research efforts to look for effective methodologies of analog and mixed-signal test and fault diagnosis are being actively developed now.

Another motivation is coming from modern technology advances. First, it is the development of semiconductor technology that results in such products with high integration density as analog VLSI chips, large scale mixed-signal systems, and System on-Chip (SoC) solutions. Due to the unbeatable advantages of high speed, analog VLSI chip is the most promising candidate for any area in which the speed is the dominant design specification such as front-end RF circuits in communication, wireless

networking, internet, GPS navigation, real-time control systems, multimedia, artificial intelligence (AI) and information technology (IT). A newly developed technology, system-on-chip, is obtaining popularity in academia and industry. It integrates the whole system (processor, memory and peripherals) into one chip which includes electronic parts (analog and digital hybrid parts), mechanical parts, and even embedded software. As a consequence, the design, manufacture, and maintenance of such systems require corresponding techniques for testing and fault diagnosis. New challenges such as increased complexity, increased die size and reduced accessibility are posed on the problems of analog and mixed-signal test and fault diagnosis.

Secondly, development of computer-aided design tools allowed designers to design more and more complicated circuits. However, corresponding test and diagnosis techniques for analog parts did not improve at the same level. The commercial software devoted to analog circuits still stays on the simulation level such as PSpice, Saber, Smash, etc. The available commercial design and simulation software could satisfy test and diagnosis requirement to some extend by systematic checks and verification of the design process. But insufficient development of test and diagnosis tools (relative to automated design tools) obviously hampers further development of advanced electronic products. Without specialized effective testing and fault diagnosis techniques for analog circuits, the system implementation, time-to-market, and time-to-volume of such products are in significant jeopardy.

Thirdly, digital test can be concluded as successful and mature comparing with analog test and fault diagnosis. Fault models such as stuck-at-1 and stuck-at-0 models which represent the most fault mechanisms encountered in digital circuits have been widely accepted for a long period. Test strategies, test buses or standards such as Designfor-Testability (DFT) and Built-In-Self-Test (BIST) were proven effective in terms of circuit area, test time, and test cost. Particularly, the IEEE 1149.1 standard for digital boundary-scan test gains more and more supports from industry, so that most of digital products could be effectively tested based on this standard. Computer-aided digital testing software is available commercially and digital Automated Test Equipment (ATE) is widely utilized in manufacturing process of digital products. It is the significant success of digital test that transfers the problem of mixed-signal test to be dominated by the problems of analog test and diagnosis, while digital portions within a mixed-signal system can be easily ested by their domain specific technologies. Based on such assumption, the research focus in this dissertation is on analog test and fault diagnosis.

All of these advances in the techniques for semiconductor integration, automated design, and digital test, together with economic considerations reluctantly witness the falling behind of the analog and mixed-signal test and fault diagnosis. The significant improvement in the automation level of analog and mixed-signal design, test, and fault diagnosis are expected to bridge the gaps with the techniques for digital design, integration and test. In 1998, IEEE proposed the 1149.4 standard for mixed-signal test bus, in order to standardize the process of analog and mixed-signal test and fault diagnosis. But it is only one of attempts to address the problem of analog and mixed-signal test and fault diagnosis, and has not yet gained enough support from industry. Different voices can also be heard from academia about this standard. It does not enjoy the similar success level like its counterpart – IEEE 1149.1 standard for boundary scan in digital test area. There is still a long way for the emergence of a widely accepted standard

or strategy in analog test and fault diagnosis. In general, there is an urgent and growing need to develop methodologies and software tools for analog test and fault diagnosis.

### 1.3. Objectives of the Dissertation

Based on the assumption that mixed-signal system is decomposed into separated analog, digital and software blocks, the scope of this dissertation is in the area of analog test and fault diagnosis.

Facing up the fact that there is no general paradigm in analog test and diagnosis, the primary objective of the dissertation research is exploring a computer-aided test and diagnosis methodology or strategy applicable to general analog systems. The challenging test problems happened in most of analog systems including ambiguities, complexity, accessibility, catastrophic faults and model building are on the top list of the dissertation research. The computer-aided solution to analog test and fault diagnosis is to improve the efficacy and automation level of the test methodologies. Thus, the research results could be programmed and embedded into simulator or ATE test program.

The subject is a continuous-time, time-invariant, analog system under stable state. Independent measurements are limited, so that an obvious identification of faults cannot be guaranteed. The primary task in dissertation research is to address ambiguities problem in analog fault diagnosis. Firstly, the analog system can be described in matrix format by circuit analysis and measurement. Hence this system description matrix is determined by parameter values, parameter locations (or circuit topology) and measurements. When faults occur, the value changes of faulty parameters and their corresponding locations must be reflected in system description matrix in terms of dependency/independency, and/or consistency/inconsistency relations among matrix elements. Then, the dissertation research is to find out an approach to efficiently extract the ambiguities hidden in system description matrix to identify the faults and implement the aims of analog test and diagnosis.

The other tasks in dissertation work include exploring complexity and accessibility problems through decomposing large system into smaller subsystems, and considering special test cases – catastrophic faults location. The significance of this dissertation work is to provide a efficient and systematic paradigm for general-background analog test and fault diagnosis.

## 1.4. Classification

The existing techniques for analog and mixed-signal test and fault diagnosis come from different research efforts with distinct goals to satisfy the requirements for specification, function, or model. The most straightforward technique is to ensure that the circuit meets all the specification requirements provide by the design engineers. This is called specification-based test technique. The test inputs are generated directly from the specifications. Thus, a circuit passing test process will surely meet the specifications. However, this technique is extremely expensive because the number of specifications is usually huge even for small analog circuits.

Another technique is to verify that the circuit meets the desired functional requirements. This is called functional-based test technique [4, 50]. It is very effective for

digital test since digital circuits satisfying desired function will meet the performance requirements. But most of specifications of analog circuits are not function-based. It is possible for an analog circuit to function correctly without meeting performance specifications. This is one of the peculiarities of analog circuits which result from its highly nonlinear behavior.

One idea is to build models for specific faults encountered in the process of design, manufacture and operation. This is called model-based technique [3-4, 50]. Since until now no effective fault model can cover most of fault mechanisms, no direct relation between fault coverage and specification satisfaction can be established. Therefore, this technique is only effective for specific faults, not for the faults not covered by the fault model.

Analog and mixed-signal test and fault diagnosis can also be divided into two categories according to the number of faults: single fault and multiple-fault [2-4]. Single fault is the most common case occurred in practice. Multiple-fault case usually happens as a consequence of a serious single fault. For example, a short-circuit fault may result in a strong current and cause the failure of other circuit components. Multiple-fault is more difficult to model and detect, particularly in the presence of tolerance or a measurement noise. In addition, in a multiple-fault situation, one fault's effect on the circuit could be masked by the effects of other faults. The research in this dissertation addresses a multiple-faults diagnosis.

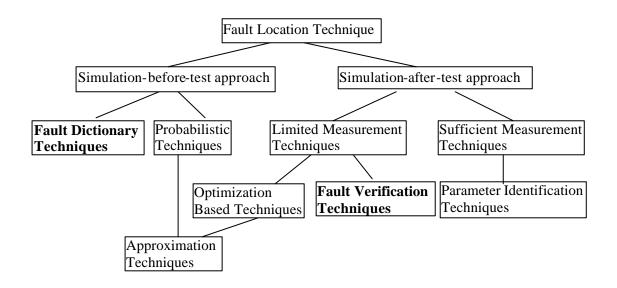

In this dissertation, a popular classification proposed by Bandler [2] is used, which categorizes the analog and mixed-signal test and fault diagnosis according to the stage in testing process at which simulation of the tested circuit occurs: Simulation-

Before-Test (SBT) and Simulation-After-Test (SAT) approach. Fig. 1.1 illustrates the different techniques according to this classification in [2].

Figure 1.1 Classification of analog test and fault diagnosis [2]

Fault dictionary technique is the most popular methodology under the Simulation Before-Test approach. It has wide applications in digital test, in which the responses of circuit under test are compared with a set of pre-stored outputs on the ATE. Similarly, analog circuits are analyzed and most likely faults are collected into the look-up table, or a dictionary. Then the circuit for each case of specific faults is simulated with chosen stimuli, and the corresponding responses are also stored in the dictionary. To achieve the required degree of diagnosability, optimum measurements are selected. In the process of testing, responses of the CUT are compared with signatures stored in the dictionary. Fault location is implemented by criteria based on pattern recognition methods. There are three dominant methods in constructing a fault dictionary for analog circuits: DC, frequency domain, and time domain approaches. Efficient fault simulation and optimum selection of measurements play very important role in the dictionary method.

Approximation technique is based on the optimization theory. Although a limited number of measurements is needed, on-line simulation (and thus extensive on-line computation) is required for fault location. The most likely fault parameters are located according to certain fault locating criteria. Due to the nature of this technique, the exact solution to fault location and parameter evaluation cannot be obtained. Therefore the application of such kind method is limited.

Fault verification technique is a practical and promising solution to the problems of analog test and fault diagnosis. When the number of faults is limited and the number of independent measurements is greater than the number of faults, verification techniques are effective based on known information such as circuit topology, nominal circuit parameters and nodal voltage measurements.

The most attractive feature of parameter identification technique is that it can provide solution to the values of all circuit parameters within faulty circuit. The faulty parameters are consequently located by checking which circuit parameters are beyond the design tolerance margins. Circuit topology and nominal values of all circuit parameters are assumed known. Only a part of the circuit nodes is accessible for measurement. The necessary condition for parameter identification technique is that enough independent measurements must be used. This leads to an unavoidable disadvantage for this technique: too many accessible nodes are required for independent measurements, which is not practical for analog circuits with high integration density and limited accessibility. Considering both advantages and disadvantage of above four techniques, fault dictionary and fault verification techniques are the most promising solutions to practical problems in analog test and fault diagnosis. Most of research efforts from industry and academia are located within dictionary and verification categories. In this dissertation, techniques of fault dictionary, fault verification including decomposition methods are involved to address the problems in analog test and diagnosis.

## 1.5. Problems in Analog Test and Fault Diagnosis

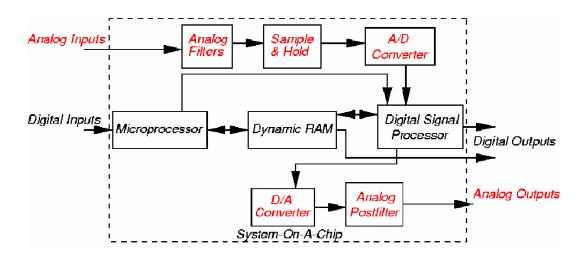

Fig. 1.2 is a typical diagram of analog and mixed-signal system. Most of tasks are processed by digital units. This is a trend in today's market of mixed-signal products. Although analog units are relatively less numerous than digital in modern electronics, they cannot be completely replaced by digital units completely because the real world is talking in analog signals. Analog units such as filter, sample-and-hold (S&H), analog-to-

Figure 1.2 Diagram of analog and mixed-signal system

digital converter (ADC), digital-to-analog converter (DAC), and phase-locked-loop (PLL) are utilized as interfaces between digital processing units and the real world. High frequency communication signals, radio transmitters, TV broadcast, etc, are using modulated analog signals for transmission, perhaps transmitting digital information.

In order to test an individual analog unit within such a mixed-signal system, all available information about circuit-under-test is collected. Circuit topology and nominal circuit parameters can be obtained from manuals or design engineers. Excitations and responses can be measured. Based on these known information, the task of test and fault diagnosis is to obtain useful information about faults by different circuit analysis and information extraction techniques (Fig. 1.3).

Figure 1.3 Diagram of analog and mixed-signal test and fault diagnosis

The difficulties of analog est and fault diagnosis lie in inherited features of analog circuits. The first challenging problem is ambiguities which prevent accurate measurement and accurate computation. Examples of ambiguities include circuit parameter tolerance, limited measurements and non-linearity of analog circuits. Even for a linear circuit, the deviation of circuit parameters from their nominal values will lead to the nonlinear relationship between the circuit responses and changes in the component values. With the popularity of SoC, circuit complexity is significantly increased while accessibility is relatively reduced. Universally accepted, effective analog fault model to establish a relation between fault coverage and circuit performance is still lacking. Fast and efficient computation algorithms are also greatly needed for analog simulation and building up analog models.

Due to above difficulties in analog test and fault diagnosis, analog test cost is significantly increasing. Table 1.1 is the average cost for one ATE according to statistical data in 2000: \$ 4.272 M to buy one ATE and \$ 1.439 M to operate this ATE [31].

Table 1.1 Cost of manufacturing testing in 2000AD[31]

| • | <ul> <li>0.5-1.0GHz, analog instruments,1,024 digital pins:</li> </ul> |  |  |  |  |  |

|---|------------------------------------------------------------------------|--|--|--|--|--|

|   | ATE purchase price                                                     |  |  |  |  |  |

|   | = \$1.2M + 1,024 x \$3,000 = <b>\$4.272M</b>                           |  |  |  |  |  |

| • | Running cost (five-year linear depreciation)                           |  |  |  |  |  |

|   | = Depreciation + Maintenance + Operation                               |  |  |  |  |  |

|   | = \$0.854M + \$0.085M + \$0.5M                                         |  |  |  |  |  |

|   | = <b>\$1.439M/year</b>                                                 |  |  |  |  |  |

|   |                                                                        |  |  |  |  |  |

| • | Test cost (24 hour ATE operation)                                      |  |  |  |  |  |

|   | = \$1.439M/(365 x 24 x 3,600)                                          |  |  |  |  |  |

|   | = 4.5 cents/second                                                     |  |  |  |  |  |

|   |                                                                        |  |  |  |  |  |

Table 1.2 shows the developing trends of IC fabrication [32]. ATE is becoming more and more expensive because semiconductor products will become more and more complicated in terms of circuit complexity, pin number, clock rate, power consumption, etc.

|                       | 1997 -2001  | 2003 - 2006 | 2009-2012 |

|-----------------------|-------------|-------------|-----------|

| Feature size (micron) | 0.25 - 0.15 | 0.13 - 0.10 | 0.07-0.05 |

| Transistors/sq. cm    | 4 - 10M     | 18 - 39M    | 84-180M   |

| Pin count             | 100 - 900   | 160 - 1475  | 260-2690  |

| Clock rate (MHz)      | 200 - 730   | 530 - 1100  | 840-1830  |

| Power (Watts)         | 1.2 - 61    | 2 - 96      | 2.8-109   |

Table 1.2 Current and future development of IC fabrication [32]

In this dissertation, all above problems are buched on and at least one solution facing general background analog systems is provided for each problem. Fault verification based on ambiguity group locating technique is described in Chapter 2 to address the problem of ambiguities resulting from limited measurement for the purpose of accurate computation. To reduce complexity, Chapter 3 illustrates how to decompose a large scale system into smaller sub-systems in order to reduce system complexity. Simultaneously, nodal voltages on some specific inaccessible nodes can be calculated. Thus, accessibility to its systems is relatively increased. Based on a stuck fault model, a multiple-stuck-fault location technique is implemented in Chapter 4 to eliminate the requirement for repetitive simulations in traditional stuck-fault location techniques. Conclusions are given in Chapter 5.

# CHAPTER 2 FAULT VERIFICATION FOR ACCURATE COMPUTATION

#### 2.1. Ambiguity and Verification

One of the reasons for ambiguities in analog test and fault diagnosis is a limited number of independent measurements. Fault verification technique is effective for accurate computation to address the problem of limited measurements. As stated in Section 1.4, fault dictionary and fault verification techniques are the most utilized approaches in analog fault diagnosis. Dictionary techniques require huge simulation works [5-7] before test because a complete fault dictionary containing all feasible fault examples cannot obviously be generated due to the continuous nature of the analog parametric faults. That is why dictionary technique usually test and diagnose the singlefault case and catastrophic faults, but not effective for multiple-fault case or parametric faults. Neural network through learning and training processes can supplement this incompleteness problem by sampling the fault space or recognizing the fault patterns [8-10]. As a consequence, the accuracy of fault location and parameter evaluation is limited by those optimization approaches.

Fault verification is a promising solution to solve limited measurements and computation accuracy problems in analog test and fault diagnosis. The basic requirement is that a few parameters are faulty while the remaining parameters are within design tolerance specifications. Specifically speaking, the number of measurements required is less than the number of circuit nodes or circuit parameters, but greater than the number of

faults in a faulty circuit. The circuit topology is assumed known, thus the graph theory can be utilized to locate faulty parameters. The nominal values of circuit parameters are also supposed known to facilitate the application of network theory and mathematical methods in the fault location. Only the voltage measurements are needed, which reduces the error introduced by measurement instrumentation. All of these requirements are easily satisfied in practice. The idea behind fault verification technique is to check the consistency of certain equations which are invariant to the changes in faulty parameters. Since this technique checks whether a certain subset of circuit parameters can be faulty or not based on the assumption that the circuit is faulty, it is referred to as a verification technique.

In [11-12], a verification technique was developed for single-fault diagnosis in piecewise linear analog circuits based on homotopy approach and on bilinear transformation. Another verification approach was proposed in [13] for parametric fault diagnosis in linear and non-linear circuits, but its performance is weak when the values of deviations are large. Large change sensitivity analysis was utilized by some researchers [14, 33] in analog fault diagnosis when there are large deviation values of parametric faults. To address the problems of computation round-off and large amount of computations, symbolic analysis was utilized [15-17]. To efficiently recognize the ambiguity groups hidden within the fault diagnosis equation, different ambiguity group locating techniques were proposed for fault verification [18-20, 34]: symbolic analysis was utilized in [18], numerical analysis in [19, 34] and decomposition analysis in [20].

In [21], a fault verification method was proposed for single fault diagnosis in linear analog circuits. Multiple excitations are required and Woodbury formula in matrix

theory is applied to locate the faulty parameter. This method was also applied to multiple fault diagnosis by decomposition technique assuming that each sub-circuit contains at most a single faulty parameter. In this chapter, the fault verification method developed in [21] is generalized and extended to multiple fault diagnosis of linear analog circuits in frequency domain. Ambiguity group determination based on numerical analysis in [19] is modified and used for fault location. Large parametric deviations and open/short faults are considered.

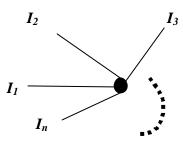

In Section 22, Kirchhoff current law (KCL) is applied to each circuit node, together with the constitutive equations for all circuit parameters without admittance description, to obtain the modified nodal equation. Circuit topology is comprehensively described by two structural matrices, and the Woodbury formula is used to construct the fault diagnosis equation. In Section 2.3, a newly developed technique for minimum size ambiguity group locating technique based on QR factorization is applied to detect and identify the multiple faults directly. Only one node is needed for voltage measurement, but multiple excitations and corresponding measurements on this node are required for fault identification. Parameter evaluation is to calculate the exact solution to the deviated values of faulty parameters. Section 2.4 provides example circuits to demonstrate the developed technique. The results are compared with those obtained by the method in [21]. The demonstrated methodology is generalized in Section 2.5 and applied to develop two new techniques for multiple fault diagnosis. Simultaneously, an advanced research on this verification technique is explored in order to remove Gaussian elimination and swapping operations based on multiple excitations and multiple measurements. Example

circuit is used to verify this approach. In Section 2.6, the developed techniques are summarized.

## 2.2. Woodbury Fault Verification Technique

Generally, circuit topology as well as its parameters' nominal values are known. Consider a continuous-time, time-invariant, strongly connected, linear circuit with n+1 nodes and p parameters. The  $(n+1)^{th}$  node , denoted by zero, is assigned to be the grounded reference node while the remaining n nodes are ungrounded. All p parameters are divided into two categories: one contains parameters which have admittance description such as conductance, capacitor and voltage-controlled-current source, another contains parameters which have no admittance description such as impedance, inductor, current-controlled-source, operational amplifier, etc.

Applying the KCL to each circuit node, one can obtain n equations with variables being nodal voltages and parameter currents. Constitutive equations in terms of nodal voltages and parameter currents, which define the characteristics of all parameters without admittance description, are appended to the above n KCL-based equations, thus the system's equations are constructed in the following form:

$$T_g X_g = W_g \tag{2.1}$$

where  $T_g$  is a gxg coefficient matrix consisting of circuit parameters,  $X_g$  is a gx1solution vector of node voltage and parameter currents, and  $W_g$  is a gx1 excitation vector composed of independent current and voltage sources, and initial conditions of capacitors and inductors. The first *n* rows in  $T_g$ ,  $X_g$  and  $W_g$  correspond to *n* nodes. The resulting system equation (2.1) is called the *modified nodal equation* in [35]. Note that g=n for normal nodal analysis of a circuit in which all parameters have admittance description, and g>n for modified nodal analysis of a circuit in which some parameters have non-admittance description. Provided that the circuit functions in a stable state, the parametric values of nodal voltages and parameter currents are finite and unique. The coefficient matrix  $T_g$  is non-singular since the circuit is a strongly connected network.

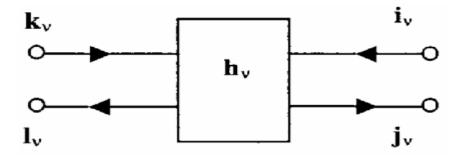

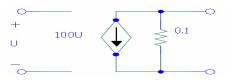

Figure 2.1 Model of parameter location

One important fact about circuit topology is that each circuit parameter, say  $h_v$  (v = 1, 2, ..., p), can be located by at most 4 circuit nodes as indicated in Fig. 2.1: 2 input nodes  $k_v$  and  $l_v$ , and 2 output nodes  $\dot{i}_v$  and  $\dot{j}_v$ . The current orientations are also indicated in Fig. 2.1. For 2-terminal parameters such as resistor and capacitor, the input nodes will be the same as the output nodes:  $k_v = i_n$  and  $l_v = j_n$ . Based on this fact, the

circuit topology can be completely described by two gxp structural matrices P and Q which are defined as follows:

$$P = [p_1 \ p_2 \ \dots \ p_p] = [e_{i_1} - e_{j_1} \ e_{i_2} - e_{j_2} \ \dots \ e_{i_p} - e_{j_p}]$$

$$Q = [q_1 \ q_2 \ \dots \ q_p] = [e_{k_1} - e_{l_1} \ e_{k_2} - e_{l_2} \ \dots \ e_{k_p} - e_{l_p}]$$

(2.2)

where  $e_n$  represents a gx1 vector of zeros except for the  $v^{th}$  entry, which is equal to one, and  $p_n$  and  $q_n$  represent gx1 vectors describing the locations of output nodes and input nodes, respectively. Matrices P and Q are only determined by the locations, not the values of the circuit parameters. The columns of matrix P correspond to the locations of the output nodes of circuit parameters while the columns of matrix Q correspond to the locations of the input nodes of circuit parameters.

Another important fact is that most parameters in linear circuits will enter the coefficient matrix  $T_g$  in the symbolic form

$$\begin{array}{ccc} k_{\mathbf{n}} & l_{\mathbf{n}} \\ i_{\mathbf{n}} & \begin{bmatrix} h_{\mathbf{n}} & -h_{\mathbf{n}} \\ -h_{\mathbf{n}} & h_{\mathbf{n}} \end{bmatrix} \end{array}$$

(2.3)

with the equivalent algebraic representation being

$$(e_{i_n} - e_{j_n})h_n (e_{k_n} - e_{l_n})^T = p_n h_n q_n^T$$

(2.4)

where superscript T denotes transpose of a matrix or a vector. For any grounded node, the corresponding row or column in the symbolic form will be removed together with the corresponding unit vector  $e_n$  in the algebraic form. Resistor, inductor, capacitor,

dependent sources, and operational amplifier with its negative inverse gain being a parameter are examples of circuit devices described in this way. In this chapter, all faulty parameters are restricted to such type of circuit devices.

Apply (2.1) to fault-free and faulty circuit, respectively, with the same excitation sources to get

$$T_0 X_0 = W_0 \tag{2.5}$$

$$TX = (T_0 + \Delta T)(X_0 + \Delta X) = W_0$$

(2.6)

where

$$T = T_0 + \Delta T \tag{2.7}$$

$$X = X_0 + \Delta X \tag{2.8}$$

Suppose that the first f of p parameters are faulty and are changed from their nominal values  $h_{10}, h_{20}, ..., h_{f0}$  to the new values  $h_1 = h_{10} + d_1, h_2 = h_{20} + d_2, ...,$  $h_f = h_{f0} + d_f$ , where  $d_1, d_2, ..., d_f$  are the parameter deviations and the deviation vector d is an fx1 vector:

$$\boldsymbol{d} = [\boldsymbol{d}_1 \ \boldsymbol{d}_2 \ \dots \ \boldsymbol{d}_f]^T \tag{2.9}$$

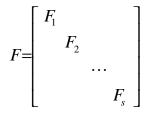

Define *F* as the faulty parameter set, and assume that each faulty parameter  $F_v$  (v = 1, 2, ..., f) is located on intersection of the corresponding rows  $i_v$  and  $j_v$  and columns  $k_v$  and  $l_v$  of the coefficient matrix *T*. The deviation of the coefficient matrices now has the following form:

$$\Delta T = \sum_{n=1}^{f} p_{\nu} \boldsymbol{d}_{n} q_{n}^{T} = P_{f} diag (\boldsymbol{d}) Q_{f}^{T}$$

(2.10)

where  $diag(\mathbf{d})$  is an *fxf* diagonal matrix and  $P_f$  and  $Q_f$  are *gxf* matrices which contain 0 and  $\pm 1$  entries:

$$P_{f} = \begin{bmatrix} p_{1} & p_{2} & \dots & p_{f} \end{bmatrix} = \begin{bmatrix} e_{i_{1}} - e_{j_{1}} & e_{i_{2}} - e_{j_{2}} & \dots & e_{i_{f}} - e_{j_{f}} \end{bmatrix}$$

$$Q_{f} = \begin{bmatrix} q_{1} & q_{2} & \dots & q_{f} \end{bmatrix} = \begin{bmatrix} e_{k_{1}} - e_{l_{1}} & e_{k_{2}} - e_{l_{2}} & \dots & e_{k_{f}} - e_{l_{f}} \end{bmatrix}$$

(2.11)

Note that  $P_f$  and  $Q_f$  are sub-matrices of P and Q respectively. They can be constructed from P and Q by selecting all columns in P and Q corresponding to faulty parameters.

The solution vector for fault-free circuit is

$$X_0 = [x_{1,0} \ x_{2,0} \ \dots \ x_{g,0}]^T$$

(2.12)

where subscript 0 indicates that the denoted parameters are for fault-free circuit. Hence the product of  $Q_f^T$  and  $X_0$  can be written as

$$Q_{f}^{T} X_{0} = [e_{k_{1}} - e_{l_{1}} e_{k_{2}} - e_{l_{2}} \dots e_{k_{f}} - e_{l_{f}}]^{T} X_{0}$$

=  $[x_{k_{1},0} - x_{l_{1},0} x_{k_{2},0} - x_{l_{2},0} \dots x_{k_{f},0} - x_{l_{f},0}]^{T}$  (2.13)

=  $[x_{k_{1}l_{1},0} x_{k_{2}l_{2},0} \dots x_{k_{f}l_{f},0}]^{T}$

and it has the physical interpretation of controlling nominal signal values (e.g. voltages) on faulty parameter input terminals. Applying the Woodbury formula [36] in matrix theory

$$\left(A + PS^{-1}V\right)^{-1} = A^{-1} - A^{-1}P\left(S + VA^{-1}P\right)^{-1}VA^{-1} \qquad (2.14)$$

to (2.7) and (2.10) with  $A=T_0$ ,  $S^{-1} = diag(\mathbf{d})$ ,  $P=P_f$  and  $V = Q_f^T$ , the inverse of coefficient matrix *T* has the following form:

$$T^{-1} = \left(T_0 + P_f \, diag(\mathbf{d}) Q_f^{T}\right)^{-1}$$

=  $T_0^{-1} - T_0^{-1} P_f \left(diag(\mathbf{d}^{-1}) + Q_f^{T} T_0^{-1} P_f\right)^{-1} Q_f^{T} T_0^{-1}$  (2.15a)

The value of  $d_n$  (n = 1, 2, ..., f) cannot be zero or infinity to meet the requirements of inverting restrictions in the Woodbury formula. Since  $d_n$  being zero means fault-free parameter, and only faulty parameters will be identified by following fault diagnosis algorithm, only one restriction is resulted:  $d_n$  cannot be infinite, which corresponds to the case of open admittance or short impedance. But open or short faults can be dealt with by ideal switch introduced in modified nodal analysis [35]. Therefore, the proposed method can handle open and short faults as well.

Let us define

$$\boldsymbol{b} = [\boldsymbol{b}_1 \quad \boldsymbol{b}_2 \quad \dots \quad \boldsymbol{b}_n]^T = T_0^{-1} P_f$$

$$\boldsymbol{g} = Q_f^T T_0^{-1} P_f$$

(2.16)

then (2.15a) has following form

$$T^{-1} = T_0^{-1} - \boldsymbol{b} \left( diag(\boldsymbol{d}^{-1}) + \boldsymbol{g} \right)^{-1} Q_f^{T} T_0^{-1}$$

(2.15b)

Since the coefficient matrices  $T_0$  and T are non-singular, the solution vector for faulty circuit *X* is then obtained using (2.6) and considering (2.15b) and (2.5):

$$X = T^{-1}W_{0}$$

=  $T_{0}^{-1}W_{0} - \boldsymbol{b} \left( diag \left( \boldsymbol{d}^{-1} \right) + \boldsymbol{g} \right)^{-1} Q_{f}^{T} T_{0}^{-1} W_{0}$  (2.17)

=  $X_{0} - \boldsymbol{b} \left( diag \left( \boldsymbol{d}^{-1} \right) + \boldsymbol{g} \right)^{-1} Q_{f}^{T} X_{0}$

Thus, the deviation vector  $\Delta X$  can be obtained by (2.8) considering (2.17) and (2.13):

$$\Delta X = X - X_{0}$$

$$= -\mathbf{b} \left( diag \left( \mathbf{d}^{-1} \right) + \mathbf{g} \right)^{-1} Q_{f}^{T} X_{0}$$

$$= \begin{bmatrix} \mathbf{a}_{11} \ \mathbf{a}_{12} \ \dots \mathbf{a}_{1f} \\ \mathbf{a}_{21} \ \mathbf{a}_{22} \ \dots \mathbf{a}_{2f} \\ \dots \dots \\ \mathbf{a}_{g1} \ \mathbf{a}_{g2} \ \dots \mathbf{a}_{gf} \end{bmatrix} \begin{bmatrix} x_{k_{1}l_{1}, 0} \\ x_{k_{2}l_{2}, 0} \\ \dots \\ x_{k_{f}l_{f}, 0} \end{bmatrix}$$

(2.18)

where

$$\mathbf{a} = -\mathbf{b} \left( diag \left( \mathbf{d}^{-1} \right) + \mathbf{g} \right)^{-1}$$

$$= \begin{bmatrix} \mathbf{a}_{11} \ \mathbf{a}_{12} \ \dots \mathbf{a}_{1f} \\ \mathbf{a}_{21} \ \mathbf{a}_{22} \ \dots \mathbf{a}_{2f} \\ \dots \\ \mathbf{a}_{g1} \ \mathbf{a}_{g2} \ \dots \mathbf{a}_{gf} \end{bmatrix} = \begin{bmatrix} \mathbf{a}_{1} \\ \mathbf{a}_{2} \\ \dots \\ \mathbf{a}_{g} \end{bmatrix}$$

(2.19)

Usually, voltage measurements are easier to carry out and are less invasive to analog circuit properties than current measurements. Therefore, only nodal voltage measurements are used in this technique. Suppose the  $i^{th}$  node is accessible for measurement, then by (2.18):

$$\Delta X_{i} = [\boldsymbol{a}_{i1} \ \boldsymbol{a}_{i2} \ \dots \boldsymbol{a}_{if}] [x_{k_{1}l_{1}, 0} \ x_{k_{2}l_{2}, 0} \ \dots \ x_{k_{f}l_{f}, 0}]^{T}$$

(2.20)

According to definition of gxf matrix a in (2.19) and (2.16), matrix a does not dependent on the location of the excitation sources. Thus matrix a is invariant when applying the multiple excitation method, i.e., the same coefficients  $a_{ij}$  link deviation of measurements  $\Delta X_i$  and nominal signal values at the location of faulty parameter  $X_{k_j l_j}$ independently on the excitation vector applied. After measuring the corresponding nodal voltages at the *i*<sup>th</sup> node with *m* independent excitation vectors  $W_e$  (e = 1, 2, ..., m), following equations are then obtained

$$\Delta X_{i}^{(1)} = [\boldsymbol{a}_{i1} \ \boldsymbol{a}_{i2} \ \dots \boldsymbol{a}_{if}] [x_{k_{1}l_{1}, 0}^{(1)} \ x_{k_{2}l_{2}, 0}^{(1)} \ \dots \ x_{k_{f}l_{f}, 0}^{(1)}]^{T}$$

$$\Delta X_{i}^{(2)} = [\boldsymbol{a}_{i1} \ \boldsymbol{a}_{i2} \ \dots \ \boldsymbol{a}_{if}] [x_{k_{1}l_{1}, 0}^{(2)} \ x_{k_{2}l_{2}, 0}^{(2)} \ \dots \ x_{k_{f}l_{f}, 0}^{(2)}]^{T}$$

$$\dots \qquad (2.21)$$

$$\Delta X_{i}^{(m)} = [\boldsymbol{a}_{i1} \ \boldsymbol{a}_{i2} \ \dots \ \boldsymbol{a}_{if}] [x_{k_{1}l_{1}, 0}^{(m)} \ x_{k_{2}l_{2}, 0}^{(m)} \ \dots \ x_{k_{f}l_{f}, 0}^{(m)}]^{T}$$

or in a matrix form

$$\Delta X_{i}^{M} = \begin{bmatrix} \Delta X_{i}^{(1)} \\ \Delta X_{i}^{(2)} \\ \dots \\ \Delta X_{i}^{(m)} \end{bmatrix} = \begin{bmatrix} x_{l_{1}l_{1},0}^{(1)} & x_{l_{2}l_{2},0}^{(1)} & \dots & x_{l_{f}l_{f},0}^{(1)} \\ x_{l_{2}l_{2},0}^{(2)} & \dots & x_{l_{f}l_{f},0}^{(2)} \\ \dots \\ x_{k_{1}l_{1},0}^{(m)} & x_{k_{2}l_{2},0}^{(m)} & \dots & x_{k_{f}l_{f},0}^{(m)} \\ \end{bmatrix} \begin{bmatrix} \boldsymbol{a}_{i1} \\ \boldsymbol{a}_{i2} \\ \dots \\ \boldsymbol{a}_{if} \end{bmatrix}$$

$$= X_{b}^{MF} \boldsymbol{a}_{i}$$

(2.22)

where superscript *M* denotes the set of multiple excitations and *m* is the number of these excitations. Since each single measurement node can be one of the nodes used for multiple excitation method, then the total number of accessible nodes should be *m*. Assume that  $f \le m-1 \le p$ , then the coefficient matrix  $X_b^{MF}$  has more rows than columns which is necessary to guarantee the uniqueness of solution to (2.22) with test verification. This ability to verify results of fault diagnosis is unique for the fault verification techniques (hence their names). In addition, fault verification techniques give

exact solutions even with large (catastrophic) faults, which is also unique in analog fault diagnosis. Equation (2.22) establishes a linear relationship between the measured responses of the faulty circuit  $\Delta X_i^M$  and the faulty parameter deviations d (since according to Q.19), vector  $\mathbf{a}_i$  is a linear function of d) Therefore (2.22) is called Woodbury fault diagnosis equation, and the coefficient matrix  $X_b^{MF}$  is called Woodbury fault diagnosis matrix.

### 2.3. Fault Diagnosis in Woodbury Fault Verification Technique

Testability is not the focus of this dissertation Therefore an assumption is made that the given measurement set can give at least one finite solution to circuit parameters.

## 2.3.1. Fault Detection

As the first stage of fault diagnosis, fault detection is easily implemented. If the measurement deviation vector  $\Delta X_i^M$  in the fault diagnosis equation is a zero vector, then the CUT is judged as fault-free for the given excitation and measurement sets. Otherwise, at least one fault is judged detected by the given measurement set.

## 2.3.2. Fault Identification

To identify the faulty parameters, first let us analyze the fault diagnosis equation. The left-side of (2.22) is a known vector from measurements, the right side is the product of an unknown coefficient matrix  $X_b^{MF}$  and an unknown solution vector  $\mathbf{a}_i$ . According to (2.13), matrix  $X_b^{MF}$  is determined by faulty parameter locations and  $X_o$ , is a solution vector for fault-free circuit. Hence the columns in  $X_b^{MF}$  represent the differences between the nominal values of nodal voltages or parameter currents across the 2 input nodes of the faulty parameters. Although matrix  $X_b^{MF}$  is unknown, but all of the nodal voltages and parameter currents in fault-free circuit are really known! Similar as in (2.13), a new *mxp* matrix  $X_b^{MP}$  is constructed as follows

$$Q^{T}X_{0} = [e_{k_{1}} - e_{l_{1}} e_{k_{2}} - e_{l_{2}} \dots e_{k_{p}} - e_{l_{p}}]^{T}X_{0}$$

=  $[x_{k_{1},0} - x_{l_{1},0} x_{k_{2},0} - x_{l_{2},0} \dots x_{k_{p},0} - x_{l_{p},0}]^{T}$

=  $[x_{k_{l}l_{1},0} x_{k_{2}l_{2},0} \dots x_{k_{p}l_{p},0}]^{T}$  (2.23)

$$X_{b}^{MP} = \begin{bmatrix} x_{k_{1}l_{1},0}^{(1)} & x_{k_{2}l_{2},0}^{(1)} & \dots & x_{k_{p}l_{p},0}^{(1)} \\ x_{k_{1}l_{1},0}^{(2)} & x_{k_{2}l_{2},0}^{(2)} & \dots & x_{k_{p}l_{p},0}^{(2)} \\ \dots & & & \\ x_{k_{1}l_{1},0}^{(m)} & x_{k_{2}l_{2},0}^{(m)} & \dots & x_{k_{p}l_{p},0}^{(m)} \end{bmatrix}$$

(2.24)

where superscript *P* denotes the set of all circuit parameters. Each column of  $X_b^{MP}$  corresponds to one circuit parameter. Apparently, fault diagnosis matrix  $X_b^{MF}$  is a submatrix of  $X_b^{MP}$ , which can be constructed by collecting all columns in  $X_b^{MP}$

corresponding to the faulty parameters. Matrix  $X_b^{MF}$  has more rows than columns whereas  $X_b^{MP}$  has less rows than columns due to the restriction  $f \le m - 1 \le p$ .

For the purpose of fault identification, it is necessary to find out which set or sets of columns in  $X_b^{MP}$  can satisfy the fault diagnosis equation, i.e., find the dependency between  $\Delta X_i^M$  and the desired set(s) of columns in  $X_b^{MP}$ . It is very possible that there are more than one qualifying sets, so it is regulated in this chapter that the minimum size of the column set satisfying fault diagnosis equation will be the desired coefficient matrix in fault diagnosis equation One obvious way is to have a combinatorial search through all columns in  $X_b^{MP}$ , which is the traditional way in fault verification technique

[2] and requires the number of operations  $O\left(\sum_{i}^{f} {p \choose i}\right)$  for limited faults among p parameters, thus it is computationally costly. More efficient method for fault identification is expected to reduce the computational cost. Our idea is to transform fault identification problem into a mathematical problem: locating the minimum size ambiguity group which satisfy the fault diagnosis equation. Ambiguity group is defined as a set of parameters corresponding to linearly dependent columns of  $X_b^{MP}$  which, in general case, does not give a unique solution in fault identification. However, in this work it will be shown how the set of faulty parameters can be identified by finding ambiguity groups.

In [19], a method was developed to locate the minimum size ambiguity groups by using a linear combination matrix C (which will be introduced later) with minimum

number of non-zero entries. In this chapter, the method in [19] is modified to identify dependence of the measurement vector  $\Delta X_i^M$  on a subset of columns from  $X_b^{MP}$ . Gaussian elimination step is introduced, and a minimum size ambiguity group is located by identifying the column with minimum number of non-zero entries in the linear combination matrix *C*. The three steps, Gaussian elimination, QR factorization and swapping performance are detailed next.

#### 2.3.2.1. Gaussian Elimination

First let us denote an augmented mx(p+1) matrix  $B_S$  as the concatenation of the vector  $\Delta X_i^M$  and the matrix  $X_b^{MP}$ :

$$B_{s} = \left[\Delta X_{i}^{M} \quad X_{b}^{MP}\right]$$

(2.25)

Then the first column of matrix  $B_S$  will be normalized to have a unit in its first row,

$$\hat{B}_{s}(i,1) = \frac{B_{s}(i,1)}{B_{s}(1,1)}, \quad i = 1, 2, ..., m.$$

(2.26)

If the first entry of matrix  $B_s$ ,  $B_s(1,1)$  happens to be zero, just permute the rows of  $B_s$  so that the first entry  $B_s(1, 1)$  is non-zero. Such a nonzero entry must exist since  $\Delta X_i^M$  is a non-zero vector for a faulty circuit. Eliminate the remaining entries in the first row of matrix  $B_s$  by performing a similar operation to Gaussian elimination as follows:

$$\hat{B}_{s}(i,j) = B_{s}(i,j) - \frac{B_{s}(i,1)}{B_{s}(1,1)} B_{s}(1,j), \quad i = 1, 2, ..., m; \ j = 2, 3, ..., \ p+1$$

(2.27)

Finally, an mx(p+1) matrix  $\hat{B}_s$  is obtained in the following form:

$$\hat{B}_{S} = \begin{bmatrix} 1^{1 \times 1} & 0^{1 \times p} \\ (\Delta \hat{X}_{i})^{(m-1) \times 1} & B^{(m-1) \times p} \end{bmatrix}$$

(2.28)

where the superscript represents the size of a vector or a matrix. Matrix *B* is obtained from  $X_b^{MP}$  after elimination the dependence on  $\Delta X_i^M$  and is called a **fault verification matrix**. The dependency among columns of matrix *B* surely indicate the dependency between  $\Delta X_i^M$  and corresponding columns of matrix  $X_b^{MP}$ . Thus the research efforts can only concentrate on the dependencies among the columns of the verification matrix *B*. The fault verification matrix will be used to identify faulty parameters and find their deviations from the nominal values, thus providing us with a fault diagnosis mechanism.

# 2.3.2.2. QR Factorization

The rank of *B* determines a maximum number of faults that can be uniquely identified by solving the fault diagnosis equation. Because m-1 < p, *B* can be decomposed into two linearly dependent sub-matrices as follows

$$B = [B_1 \ B_2] = B_1 [I \ C]$$

(2.29)

$$B_2 = B_1 C \tag{2.30}$$

where (m-1)xr matrix  $B_1$  has the full column rank equal to the rank r of the matrix B, and  $r \times (p-r)$  matrix C is called a **linear combination matrix** whose columns expand a set

of basis columns from  $B_1$  into the corresponding columns of  $B_2$ . Note that the selection of independent columns of  $B_1$  is not unique, which is an important issue in solving the fault diagnosis equation in the presence of ambiguities. Different partitions define different linear combination matrices *C*.

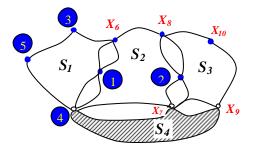

Since an ambiguity group is a set of circuit parameters corresponding to linearly dependent columns of B, a canonical ambiguity group is defined as a minimal set of parameters corresponding to linearly dependent columns of B. It means that if any single parameter is removed from the canonical ambiguity group, the remaining set corresponds to independent columns of B and is uniquely solvable. A combination of canonical ambiguity groups with at least one common element was defined as ambiguity cluster.

To efficiently deal with the fault verification problem, it is necessary to look for a partition (2.29) with the matrix *C* in a **minimum form**, which is defined as such a matrix that one or several of its columns have the maximum number of entries equal to zero. Thus, the minimum number of columns in  $X_b^{MP}$  satisfying the fault diagnosis equation (2.22) can be got. The corresponding partition (2.29) is called a canonical form of the fault diagnosis equation. Notice that according to fault verification principles [2] it is enough to find a single entry in one column of *C* equal to zero to solve the fault diagnosis equation. This column and all rows with non-zero entries will correspond to the faulty parameters indicated by the element of co-basis  $B_2$  and elements of basis  $B_1$ , respectively.

In this dissertation, a numerically robust algorithm based on the QR factorization [19] will be referred to find a numerically stable solution of over determined system of linear equations that minimizes the least square error. Fault diagnosis equation uses more

measurements than the number of unknown variables in order to be able to find a unique solution as well as to compensate for the measurement errors and noise of the measurement equipment. At least one extra measurement is needed to verify the fault selection hypothesis. As a result of the QR factorization of (m-1)xp verification matrix B, the following equation can be obtained:

$$BE = QR \tag{2.31}$$

where *E* is *pxp* column selection matrix, *Q* is (m-1)x(m-1) orthogonal matrix, and *R* is (m-1)xp upper triangular matrix. Each column of matrix *E* has only one nonzero entry, which is equal to one. Matrix product *BE* represents a permutation of the original columns of the verification matrix *B*. Matrix *R* has its rank equal to the rank of matrix *B*. Since *R* is an upper triangular matrix and m-1 < p, *R* can be written as

$$R = \begin{bmatrix} R_1 & R_2 \\ 0 & 0 \end{bmatrix}$$

(2.32)

where  $R_I$  is  $r \times r$  upper triangular and has its rank equal to the rank of the verification matrix *B*.

The following theorem in [19] provides a basis for a numerically efficient approach to finding the ambiguity groups.

## **Theorem:**

A linear combination matrix C can be numerically obtained from the QR factorization of the verification matrix B using

$$C = R_1^{-1} R_2 (2.33)$$

## 2.3.2.3. Element Swapping

A single QR run cannot guarantee that the matrix C will be obtained with one or several of its columns having the maximum number of zero entries unless the proper basis is selected. To find a minimum form partition, it is necessary to swap one parameter of the basis with one parameter of the co-basis in the ambiguity cluster in order to increase the number of nonzero entries in C. Note that swapping parameters of the basis and the co-basis can be performed independently in different ambiguity clusters, since different clusters have mutually disjoint sets of parameters.

#### **Lemma 1** [19]:

The necessary condition for swapping to increase the number of zero entries in C is that the columns of basis and co-basis to be swapped have a singular 2x2 sub-matrix of nonzero entries.

Let us consider a linear combination matrix *C* with a 2x2 singular sub-matrix  $\begin{bmatrix} c_{jk} & c_{jm} \\ c_{ik} & c_{im} \end{bmatrix}$ with all nonzero entries. If the *j*<sup>th</sup> element of the basis is swapped with *k*<sup>th</sup>

element of the co-basis, then after swapping, the  $k^{th}$  column of C changes to

$$C_{k} = -\frac{1}{c_{jk}} [c_{1k} \ c_{2k} \ \cdots \ 1 \ \cdots \ c_{rk}]^{T}$$

(2.34)

In addition, all other columns of matrix C will be equal to

$$C_{n} = \left[ c_{1n} - \frac{c_{jn}c_{1k}}{c_{ik}} c_{2n} - \frac{c_{jn}c_{2k}}{c_{ik}} \cdots \frac{c_{jn}}{c_{ik}} \cdots c_{rn} - \frac{c_{jn}c_{rk}}{c_{ik}} \right]^{T}$$

(2.35)

such that all zero locations in the  $k^{th}$  column of *C* will remain zero as they were in the original *C*. However, as can be deducted from (2.34), a nonzero location  $C_{im}$  in row *i* and column *m* will become zero. Let us analyze this column *m* with at least one zero entry. The circuit parameter in the basis corresponding to such a column *m* is selected first, then the circuit parameters in the co-basis corresponding to all non-zero entries in column *m* are selected. An ambiguity group *F* is formed by combining the selected basis parameter with the co-basis parameters. Any column of *C* with zero entries form an ambiguity group *F* and has to be consider for further processing. Since ambiguities may exist in the original matrix  $X_b^{MP}$  then *F* contains all faults in the CUT only if the corresponding columns in  $X_b^{MP}$  are independent. Hence the following lemma can be formulated:

## Lemma 2:

A necessary condition for an ambiguity group F of the linear combination matrix C to contain the set of all faults in the tested circuit is that the rank of the corresponding columns in matrix  $X_b^{MP}$  is equal to the cardinality of F.

$$rank(X_{b}^{MP}) = card(F)$$

(2.36)

Thus, according to Lemma 2, any ambiguity group of the verification matrix which do satisfy (2.36) needs to be verified.

The purpose of column swapping is to find out at least one ambiguity group of a minimum size. It is possible to locate several different ambiguity groups with minimum size and all of them will satisfy Lemma 2. The last step of fault location is to check

whether the sub-matrix of  $X_b^{MP}$  corresponding to such an ambiguity group can satisfy fault diagnosis equation or not. If yes, the circuit parameters corresponding to such a minimum size ambiguity group are concluded as a set of faulty parameters, *F*. Hence, the coefficient matrix  $X_b^{MF}$  is also determined.

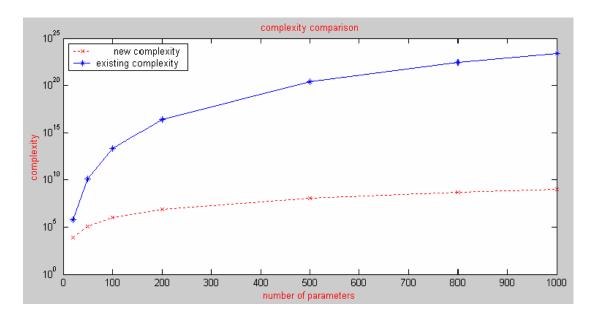

The number of operations required for Gaussian elimination step is  $O(p^2)$ ,  $O(p^3)$  operations are needed for QR factorization and  $O((p-r)^3)$  for column swapping, so the computational cost of the developed technique is  $O(p^3)$ . It is more efficient than comprehensive search whose number of operations is  $O\left(\sum_{i=1}^{l} {p \choose i}\right)$ .

Figure 2.2 Complexity comparison: comprehensive search vs. ambiguity group locating

Fig. 2.2 illustrates the complexity comparison between comprehensive search and ambiguity group location technique. Suppose that the number of faults, f, is equal to 10,

the number of circuit parameters is 20, 50, 100, 200, 500, 800 and 1000 respectively. The ambiguity group locating technique requires fewer operations, especially when the number of parameters is large.

# 2.3.3. Parameter Evaluation

After location of the faulty parameters (and determination of  $X_b^{MF}$ ), the invariant vector  $\boldsymbol{a}_i$  can be uniquely solved from (2.22):

$$\mathbf{a}_{i} = \left( \left( X_{b}^{MF} \right)^{T} X_{b}^{MF} \right)^{-1} \left( X_{b}^{MF} \right)^{T} \Delta X_{i}^{M}$$

(2.37)

Then, the parameter deviation vector d can be exactly computed by

$$\boldsymbol{d} = \boldsymbol{a}_i \ rdivide\left(-\boldsymbol{b}_i - \boldsymbol{a}_i \boldsymbol{g}\right)$$

(2.38)

where *rdivide* is an element-by-element division of two vectors. Additionally, the other variables in the faulty circuit can be obtained from the construction process of fault diagnosis equation. For example, the entire deviation vector  $\Delta X$  can be obtained by using (2.18) and considering (2.16). Then the solution vector for faulty circuit X can be obtained from Q.8). Alternatively, vector X can be solved from Q.6) by inverting its coefficient matrix T, obtained by Q.7) and Q.10). In one word, everything about the faulty circuit can be known.

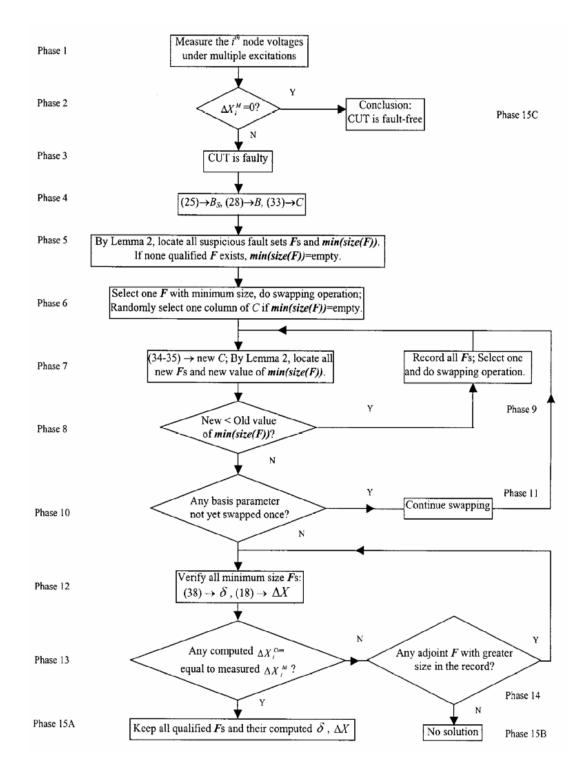

### 2.3.4. Algorithm for Fault Diagnosis

A flow diagram of a computer program which implements the fault diagnosis discussed above is shown in Fig. 2.3. Since most of the phases of the algorithm are self-evident from the flow diagram, only some phases are detailed in this section.

In Phase 1, since nominal values of circuit parameters are known and all nodal voltages in fault-free circuit can be solved by (2.5), only the nodal voltages of the  $i^{th}$  node in the CUT under multiple excitation method is needed for measurement to obtain measurement deviation vector  $\Delta X_i^M$ .

In Phase 5, F denotes one suspicious fault set and min(size(F)) represents a scalar which is equal to the minimum size of all suspicious fault sets.

In Phase 6, if several suspicious fault sets have the same minimum size, min(size(F)), select one of them arbitrarily for analysis. Only one parameter in the selected F is from the co-basis and the remaining parameters from the basis. Swap that co-basis parameter which corresponds to column k in matrix C with one of basis parameters which corresponds to row j in the matrix C. By (2.34) and (2.35), all zero entries in the column k of matrix C will be maintained after swapping while new zero-entry will appear in another column of new matrix C, thus the new value of min(size(F)) will be equal to, or less than the old value before swapping.

Figure 2.3 Algorithm for fault verification technique [39]

There are two rules for swapping. One is that, according to Lemma 1, row j is selected with nonzero  $c_{jk}$  on the intersection of row j and column k of matrix C. Another rule is that if one parameter in the current basis has been swapped into the basis by the previous swapping operation, then this element will not be considered during the later swapping operation. Usually m-1 is far less than p, and the rank of rx(p-r) matrix C, r is not greater than m-1, thus there are far less basis parameters than co-basis parameters. The comprehensive swapping between the co-basis parameter k and the basis parameters are very limited, as a result of the two swapping principles.

Phases 12 through 15B are used for verification. One or several suspicious fault sets with minimum size are used to compute the deviation vector  $\Delta X$ . If a computed vector matches the real measured vector  $\Delta X_i^M$ , the corresponding fault set F is our final solution to faulty parameters. Otherwise, this set is discarded, and turn to the adjoint suspicious fault sets recorded in Phase 9. Verification in this phase continues until finding out at least one qualified solution to faulty parameters. Otherwise, the CUT is concluded as un-solvable because the restriction  $f \leq m-1$  discussed in Section 2.2 is not satisfied.

## 2.4. Example Circuits

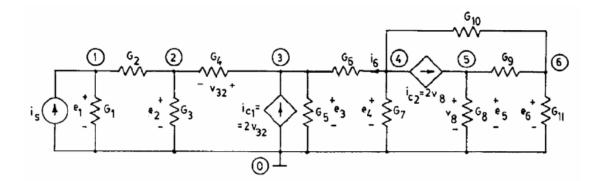

*Example 2.1:* The example circuit 4 in [21] is used here (Fig. 2.4) in order to demonstrate the improvement in efficacy by the method proposed in this paper. There are 6+1 nodes, 11 conductances, 2 voltage-controlled-current sources in the CUT, where

$G_1=1S$ ,  $G_2=1S$ ,  $G_3=2S$ ,  $G_4=1S$ ,  $G_5=0.5S$ ,  $G_6=2S$ ,  $G_7=1S$ ,  $G_8=0.5S$ ,  $G_9=2S$ ,  $G_2=1S$ ,  $G_{11}=0.5S$ ,  $i_s=1A$ .

Figure 2.4 Example circuit in [21]

Suppose that  $G_3$  and  $G_9$  have deviations  $\Delta G_3 = -1$  *S* and  $\Delta G_9 = 2$  *S*, respectively. Node *{1}* is the single measurement node. The single current source *i*<sub>s</sub> is applied between ground and three accessible nodes *{1, 3, 6}* respectively under multiple excitation method. Thus, n=6, p=13, m=3, f=2 and  $f \le m-1 \le p$ . The measurement deviation in Phase 1 of algorithm is

$$\Delta X_{i}^{M} = \begin{bmatrix} 0.2248 \\ -2.1536 \\ -1.2544 \end{bmatrix}$$

## In Phase 4, verification matrix B is obtained after Gaussian elimination as

$B = \begin{bmatrix} 5.3827 & -4.1975 & 1.1852 & -1.8272 & -0.6420 & 0.7531 & 0.1111 & -0.9877 & 0.7407 & -0.3580 & -0.2469 & 0.6420 & 1.0988 \\ 3.3827 & -2.1975 & 1.1852 & 0.1728 & 1.3580 & -0.2469 & 1.1111 & -0.9877 & 0.7407 & -1.3580 & -0.2469 & -1.3580 & 2.0988 \end{bmatrix}$

and the linear combination matrix C is obtained as

$C = \begin{bmatrix} 0.2500 & -0.2500 & -0.7500 & 0.0911 & 0.0911 & -0.2083 & 0.1563 & -0.1432 & -0.0521 & 0 & 0.2995 \\ 0.2500 & 0.7500 & 0.2500 & -0.4089 & 0.5911 & -0.2083 & 0.1562 & -0.6432 & -0.0521 & -1.0000 & 0.7995 \end{bmatrix}$

with permutation vector  $E=\{1, 5, 3, 4, 2, 6, 7, 8, 9, 10, 11, 12, 13\}$ . Thus the basis parameters are  $\{1, 5\}$  and co-basis parameters are  $\{3, 4, 2, 6, 7, 8, 9, 10, 11, 12, 13\}$ . There is only one column, the 10<sup>th</sup> column of *C*, with zero entry. The corresponding ambiguity group (or suspicious fault set) is  $\{5, 12\}$ , but it does not satisfy Lemma 2.

Swapping the first basis parameter  $\{1\}$  with the first co-basis parameter  $\{3\}$ , the new matrix *C* is obtained as

$$C = \begin{bmatrix} 4.0000 & -1.0000 & -3.0000 & 0.3646 & 0.3646 & -0.8333 & 0.6250 & -0.5729 & -0.2083 & 0 & 1.1979 \\ -1.0000 & 1.0000 & 1.0000 & -0.5000 & 0.5000 & 0.0000 & -0.0000 & -0.5000 & 0.0000 & -1.0000 & 0.5000 \end{bmatrix}$$

Totally there are three suspicious fault sets  $\{3, 8\}$ ,  $\{3, 9\}$  and  $\{3, 11\}$ , and min(size(F))=2. Note that the suspicious fault set  $\{5, 12\}$  has already been excluded by Lemma 2 in former analysis. Since min(size(F)) cannot been reduced any more by swapping, it is concluded that these three fault sets are our candidates for verification in Phase 13 through 15B.

For the fault set  $\{3, 8\}$ , the fault diagnosis equation is

| Γ | 0.2248   | ] [ | - 0.1304 | 0.6957   | ]                     |

|---|----------|-----|----------|----------|-----------------------|

|   | - 2.1536 | =   | 2.4348   | - 7.6522 | <b>a</b> <sub>i</sub> |

| L | - 1.2544 |     | 1.9130   | - 4.8696 |                       |

with its unique solution vector by (2.37)  $\mathbf{a}_i = \begin{bmatrix} 0.3191 & 0.3830 \end{bmatrix}^T$ . By (2.38), the deviations of  $G_3$  and  $G_8$  are

$$\begin{bmatrix} \Delta G_3 \\ \Delta G_8 \end{bmatrix} = \begin{bmatrix} -1.0000 \\ 0.2647 \end{bmatrix}$$

The computed nodal voltage deviations on node  $\{1\}$  is

$$\Delta X_{i}^{computed} = \begin{bmatrix} 0.2248 \\ -2.1536 \\ -1.2544 \end{bmatrix}$$

which is equal to the measured vector  $\Delta X_i^M$ . Thus, it is concluded that fault parameters are  $G_3$  and  $G_8$  with  $\Delta G_3 = -1 S$  and  $\Delta G_8 = 0.2647 S$  respectively.

For fault set  $\{3, 9\}$ , the fault diagnosis equation is

$$\begin{bmatrix} 0.2248 \\ -2.1536 \\ -1.2544 \end{bmatrix} = \begin{bmatrix} -0.1304 & -0.5217 \\ 2.4348 & 5.7391 \\ 1.9130 & 3.6522 \end{bmatrix} \mathbf{a}_{i}$$

with the deviations of  $G_3$  and  $G_9$  are equal to

$$\begin{bmatrix} \Delta G_3 \\ \Delta G_9 \end{bmatrix} = \begin{bmatrix} -1.0000 \\ 2.0000 \end{bmatrix}$$

The computed vector of nodal voltage deviations on node {1} is also equal to the measured vector  $\Delta X_i^M$ . It is concluded that fault parameters are  $G_3$  and  $G_9$  with  $\Delta G_3 = -1 S$  and  $\Delta G_9 = 2.0000 S$  respectively.

For fault set {3, 11}, similar conclusion is made that fault parameters are  $G_3$  and  $G_{11}$  with  $\Delta G_3 = -1$  *S* and  $\Delta G_{11} = 1.6364$  *S* respectively.

Totally three solutions to the faulty parameters for the given measurements are obtained. To exactly identify the faulty parameters in the CUT, more measurements are needed, which will be demonstrated in next example.

The accessible nodes are reduced to 3 (nodes 1, 3, and 6) in the developed Woodbury fault verification technique comparing with at least 4 accessible nodes in [21]: nodes  $\{1, 6\}$  for multiple excitations and nodes  $\{3, 4\}$  for measurements of the branch voltages at  $G_6$ . The selection and assumption of one fault-free parameter with corresponding measurement of its branch voltage used in decomposition method in [21] is removed, which is a notable improvement.

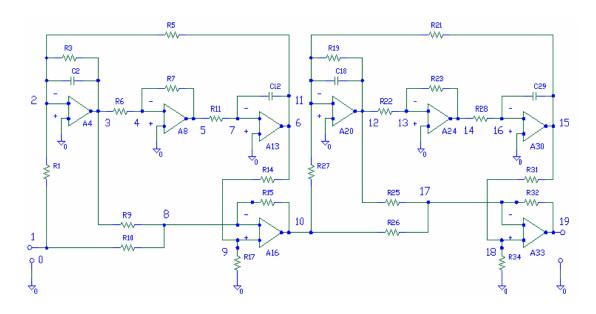

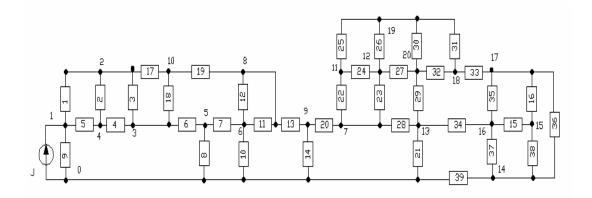

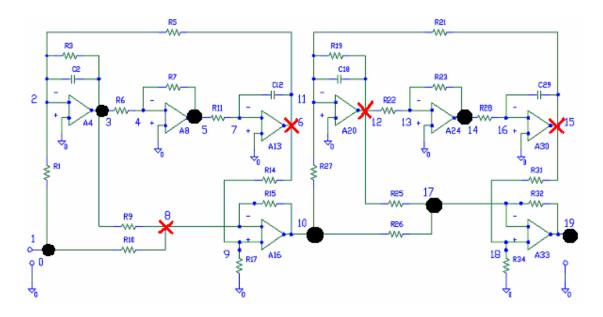

*Example 2.2:* An active low-pass filter [37] is provided as one example to illustrate the approach described in Section 2.3. The example circuit has 20 nodes and 22 resistors, 4 capacitors, and 8 amplifiers with the following nominal values (all resistors in  $k\Omega$  and capacitors in  $\mathbf{m}F$ ):  $R_1=0.182$ ,  $C_2=0.01$ ,  $R_3=1.57$ ,  $R_5=2.64$ ,  $R_6=10.0$ ,  $R_7=10.0$ ,  $R_9=100.0$ ,  $R_{10}=11.1$ ,  $R_{11}=2.64$ ,  $C_{12}=0.01$ ,  $R_{14}=5.41$ ,  $R_{15}=1.0$ ,  $R_{17}=1.0$ ,  $C_{18}=0.01$ ,  $R_{19}=4.84$ ,  $R_{21}=2.32$ ,  $R_{22}=10.0$ ,  $R_{23}=10.0$ ,  $R_{25}=500.0$ ,  $R_{26}=111.1$ ,  $R_{27}=1.14$ ,  $R_{28}=2.32$ ,  $C_{29}=0.01$ ,  $R_{31}=72.4$ ,  $R_{32}=10.0$ ,  $R_{34}=10.0$ . The current source is  $j(t) = 1.0 \cos(2000 t) A$ .

The filter is shown in Fig. 2.5 and all the operational amplifiers are modeled by the circuit in Fig. 2.6.

Figure 2.5 Active low pass analog filter

Figure 2.6 Model for operational amplifier

Assume that the faulty parameters are  $R_6$  which was changed from 10.0  $k\Omega$  to 20.0  $k\Omega$  and  $R_{26}$  changed from 111.1  $k\Omega$  to 75.0  $k\Omega$ . The corresponding admittance deviations are  $\Delta G6=1/20000 - 1/10000 = -5.0 \times e^{-5}/\Omega$  and  $\Delta G26=1/75000 - 1/111100$ = 4.3324 ×  $e^{-6}/\Omega$ . The single measurement node is node {2}, and the single current source is applied between ground and nodes {1, 2, 7, 17, 19}, respectively. Thus n=19, p=42, f=2, m=5 and the restriction  $f \le m-1 \le p$  is satisfied. The measured deviation vector in Laplace domain is

$$\Delta X_{i}^{M} = \begin{bmatrix} -3.4938 \times e^{-3} + 1.3508 \times e^{-2} & i \\ -3.5511 \times e^{-3} + 1.3729 \times e^{-2} & i \\ 2.6940 \times e^{-1} + 7.0256 \times e^{-2} & i \\ -5.1196 \times e^{-14} + 2.1975 \times e^{-13} & i \\ -3.5511 \times e^{-3} + 1.3729 \times e^{-2} & i \end{bmatrix}$$