## MIXED-SIGNAL TESTING OF INTEGRATED ANALOG CIRCUITS AND ELECTRONIC MODULES

A Dissertation Presented to

The Faculty of the

Fritz J. and Dolores H. Russ College of Engineering and Technology

Ohio University

In Partial Fulfillment

of the Requirement for the Degree

Doctor of Philosophy

by

Zhi-Hong Liu

March 20, 1999

### THIS DISSERTATION ENTITLED

## MIXED-SIGNAL TESTING OF INTEGRATED ANALOG CIRCUITS AND ELECTRONIC MODULES

by Zhi-Hong Liu

Has been approved

for the school of Electrical Engineering and Computer Science and the Russ College of Engineering and Technology

Januzs A. Starzyk, Professor

Warren K Wray, Dean Fritz J. And Dolores H. Russ College of Engineering and Technology

### Abstract

Liu, Zhi-Hong. Ph.D March 1999

Electrical Engineering

### Mixed-signal Testing of Integrated Analog circuits and modules (143pp.)

This dissertation has discussed means and techniques to improve mixed-signal testing of analog integrated systems in industrial environment. It covers a number of practical techniques ranging from component verification, statistical fault detection, and optimum test point selection to innovative use of IEEE boundary scan techniques.

A method to perform the equivalent of In-Circuit Test (ICT) as part of the End-Of-Line Test during manufacturing of modules has been investigated. The experiments have proved that the ICT stage in a manufacturing line can be effectively eliminated for certain modules. This is important as future modules are expected to pose access problems for ICT probes.

A procedure to test analog circuit using the Mahalanobis Distance (MD) is proposed. The proposed methods can be automated in performing fault simulation and in construction of the fault dictionary. It provides a robust statistical model for fault detection with good separation property and simplified representation. The frequency application uses a proper metric to measure the characteristics of analog frequency response. The AR model in the time domain essentially accomplishes a frequency sweep up to two times the sampling frequency. It also reduced the dimension of the MD measures.

A fast algorithm for test point selection is proposed. The proposed approach is based on the entropy measure. It provides an algorithm faster than previously developed approaches and has fewer selected nodes than most of them. The selection method is applicable for other applications, in which a quality of selection can be established using system entropy, for instance in information systems.

The feasibility study of using digital sequence in analog components testing has been conducted. The analog information can be stored in a sequential digital registers and be shifted out for evaluation. The proposed methodology has special practical value in testing those limited analog components on PCB board along with IEEE std. 1149.1.

Finally, an analog boundary scan bus (ABSB) has been proposed for observing analog function blocks. The proposed ABSB can be used as a subset of IEEE P1149.4 for virtual probe. The proposed ABSB is compared with IEEE P1149.4 by simulation examples. It is concluded that boundary scan bus has its limitation for high frequency applications.

Approved:\_\_\_

Signature of Director

#### Acknowledgment

When I was pursuing my MS Degree in Electrical Engineering in the early 80s at Beijing University of Posts and Telecommunications, my immediate advisor, professor Renheng Tang introduced me the field of analog fault diagnosis and I finished my master thesis in this field. After five years of teaching and working in the telecommunication area, I switched back to the same area for my Ph.D degree in 1990 at Ohio University. It is impossible for me to come to the states without Dr. Januzs Starzyk, who offered me a research assistant position at Ohio University.

Thanks to Dr. starzyk, Dr. Susana Stoica, and Mr. Gary Mazynski, I got a chance to work in Ford Motor Company in the area of manufacturing testing. My experience at Ford is essential to the selection of the topics, which emphasized more on the application of theory to industry. During my work in Ford Electronics (Now Visteon), I learned a lot from Mr. Lawrence Kirk in the understanding of electronic design and analog integrated circuits and from Dr. stoica in the understanding of basic test concepts. I also got technical guidance from Dr. Dan Dandapani from University of Colorado at Colorado springs. The strong leadership from Dr. Depak Goel and Dr. Stoica helped our project and my dissertation.

I also wanted to express my thanks to Ralph Prunty of Quantum Consultant for his help in understanding of physics failures and statistics. My Thanks should also go to my college Ms. Alicia Spola at GM Small Car Group, who helped me with most of the English correction.

Finally, I would like to thank to my wife Fu-Kai Yang and my parents for their constant support and encouragement for this degree.

| Acknowledgment i                                                                   |

|------------------------------------------------------------------------------------|

| List of Tables iv                                                                  |

| List of Figuresv                                                                   |

| List of Abbreviations vii                                                          |

| Chapter 1 Introduction                                                             |

| 1.1 Basic test issues                                                              |

| 1.2 Introduction of the dissertation topics                                        |

| Chapter 2 A Review of Analog testing                                               |

| 2.1 SAT methods                                                                    |

| 2.2 SBT methods                                                                    |

| 2.3 Failure Modes and Mechanisms for electronic components                         |

| Chapter 3 Analog testing                                                           |

| 3.1 PCB board testing using the component verification approach                    |

| 3.1.1 Component verification approach                                              |

| 3.1.2 A design for test rule for component verification                            |

| 3.1.3 Y- $\Delta$ transformation, pull-up<br>resistor measurement, and testability |

| 3.2 Analog Fault Detection with Mahalanobis Distance ( <b>MD</b> )                 |

| 3.2.1 Mahalanobis Distance                                                         |

| 3.2.2 The frequency test and Mahalanobis Distance                                  |

| 3.2.3 The time domain test and Mahalanobis Distance                                |

| 3.3 An entropy based approach for test point selection             |

|--------------------------------------------------------------------|

| 3.3.1 Fault-wise Table                                             |

| 3.3.2 Inclusive and exclusive approaches                           |

| 3.3.3 Entropy based approach                                       |

| 3.3.4 Test point selection example                                 |

| 3.3.5 Minimum test sets                                            |

| Chapter 4 Application of IEEE Boundary Scan Standards              |

| 4.1 A discussion on boundary scan standards                        |

| 4.1.1 IEEE standard 1149.1 86                                      |

| 4.1.2 Proposed IEEE P1149.4                                        |

| 4.1.3 Analog scan vs. Digital scan                                 |

| 4.2 Testing of analog interconnections with IEEE standard 1149.194 |

| 4.2.1 Delay testing                                                |

| 4.2.2 Fault diagnosis through delay analysis                       |

| 4.2.3 Testing of analog components using boundary scan             |

| 4.3 A "virtual probe" test bus compatible with IEEE 1149.1         |

| Chapter 5 Conclusion                                               |

| Bibliography                                                       |

| Abstract                                                           |

# List of Tables

| Table 2.3.1 Relative occurrences of failure modes in some electronic components       25   |

|--------------------------------------------------------------------------------------------|

| Table 2.3.2 Relative indexes of manufacturing process defects for a manufacturer.       27 |

| Table 2.3.3 Percentage incidences of failure allocations    29                             |

| Table 2.3.4 IC failures, defects, Mechanisms, and electrical failure modes                 |

| Table 3.1.1.1 Impedance test limits for Fig. 3.1.1.2                                       |

| Table 3.2.2.1 Mahalanobis distance for Example 3.2.2.1                                     |

| Table 3.2.3.1 Mahalanobis distance for Example 3.2.3.1    60                               |

| Table 3.2.3.2 Sensitivity matrix for bandpass filter    62                                 |

| Table 3.3.1.1 A fault-wise table    70                                                     |

| Table 3.3.4.1 Test node measurements of an active filter circuit                           |

| Table 3.3.4.2 Integer coded fault-wise table for an active filter circuit                  |

| Table 3.3.4.3 Re-arranged fault-wise table after choosing $n_{11}$                         |

| Table 3.3.4.4 Re-arranged fault-wise table after choosing $n_{11}$ and $n_9$               |

| Table 3.3.4.5 Entropy calculated and node selected    82                                   |

| Table 3.3.5.1 Minimum test sets                                                            |

| Table 4.2.1.1 Test nodes and ambiguity groups    103                                       |

| Table 4.2.2.1 Logic values for nominal and fault circuitry    110                          |

# List of Figures

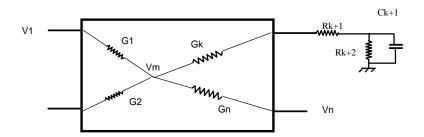

| Figure 3.1.1.1 A typical PCB board structure, used especially in automotive           |

|---------------------------------------------------------------------------------------|

| Figure 3.1.1.2 A typical input circuitry                                              |

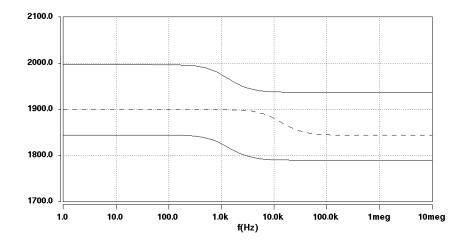

| Figure 3.1.1.3 The impedance at pin J1_13 40                                          |

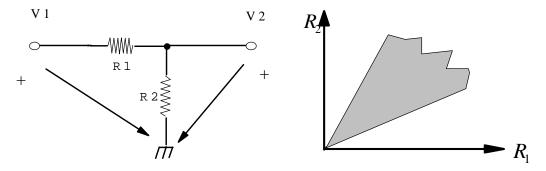

| Figure 3.1.2.1 A voltage divider and its feasibility region for testability design 42 |

| Figure 3.1.3.1 N-port pull-up network                                                 |

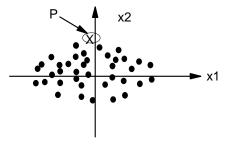

| Figure 3.2.1.1 Scatter plot for bivariate                                             |

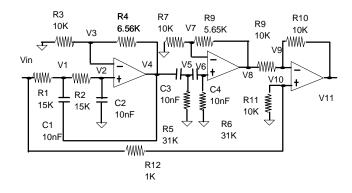

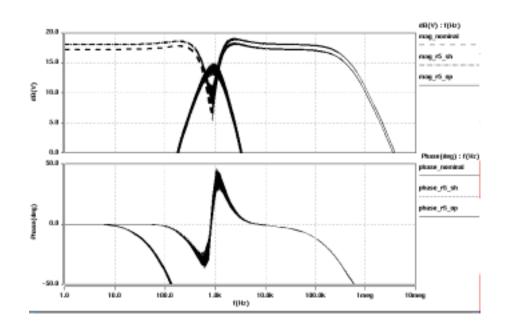

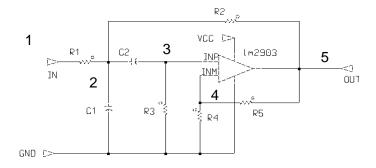

| Figure 3.2.2.1 An active filter                                                       |

| Figure 3.2.2.2 Nominal responses, $R_5$ open and short responses                      |

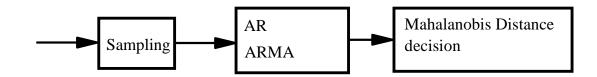

| Figure 3.2.3.1 (a) Simulation-before-test algorithms                                  |

| Figure 3.2.3.1 (b) Simulation-after-test algorithms                                   |

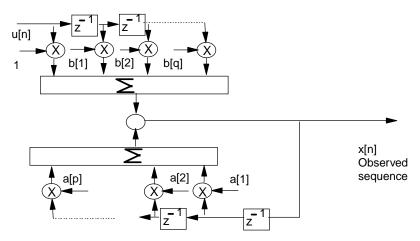

| Figure 3.2.3.2 ARMA model of a random process                                         |

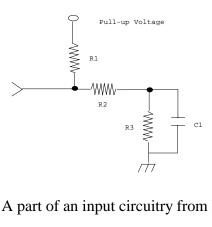

| Figure 3.2.3.3 A part of an input circuitry from Figure 3.1.1.2                       |

| Figure 3.2.3.4 A bandpass filter                                                      |

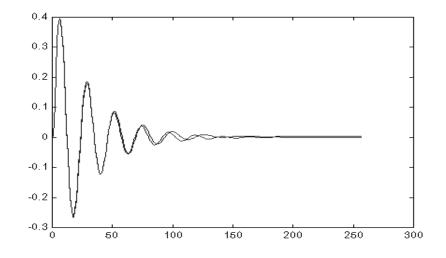

| Figure 3.2.3.5 Comparison between step response and AR model                          |

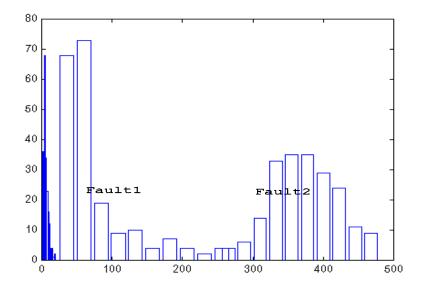

| Figure 3.2.3.6 Histogram of mahalanobis distance                                      |

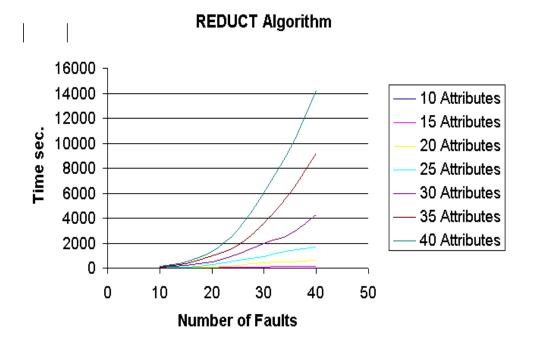

| Figure 3.3.5.1 Computational cost of the REDUCT algorithm                             |

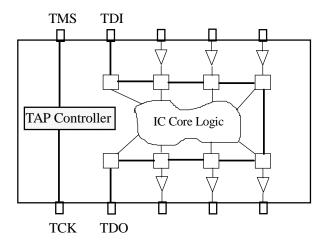

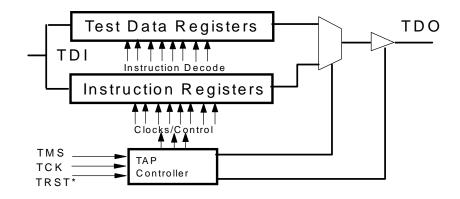

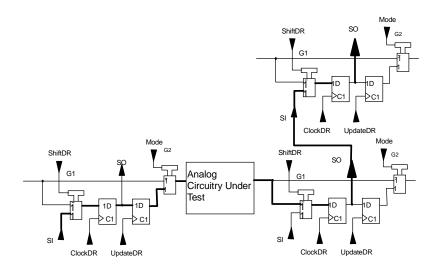

| Figure 4.1.1.1 IC with TAP controller and boundary scan cells for digital circuit 87  |

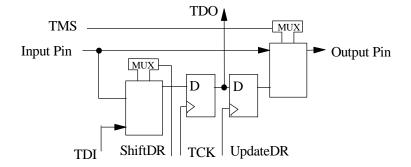

| Figure 4.1.1.2 An IEEE std. 1149.1 boundary scan cell                                 |

| Figure 4.1.1.3 The TAP architecture                                                   |

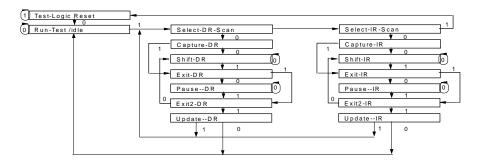

| Figure 4.1.1.4 TAP controller state diagram                                           |

| Figure 4.1.2.1 The structure for the proposed IEEE standard P1149.491                 |

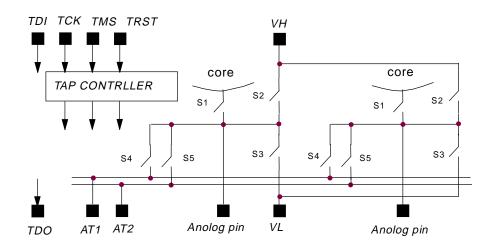

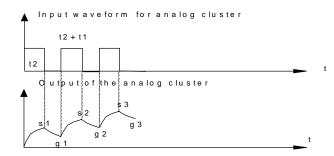

| Figure 4.2.1 An analog cluster with the IEEE boundary scan cells                         |

|------------------------------------------------------------------------------------------|

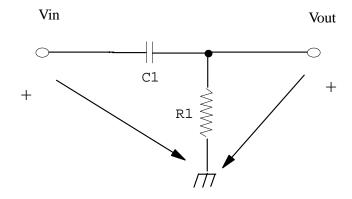

| Figure 4.2.2 A high pass filter                                                          |

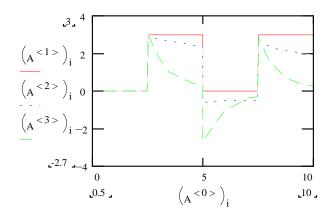

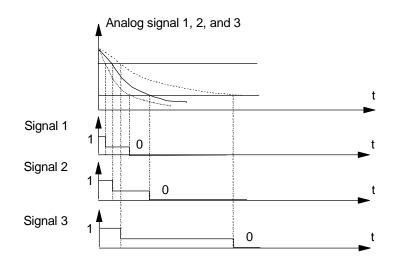

| Figure 4.2.3 The input and output of the low pass filter for different capacitor value95 |

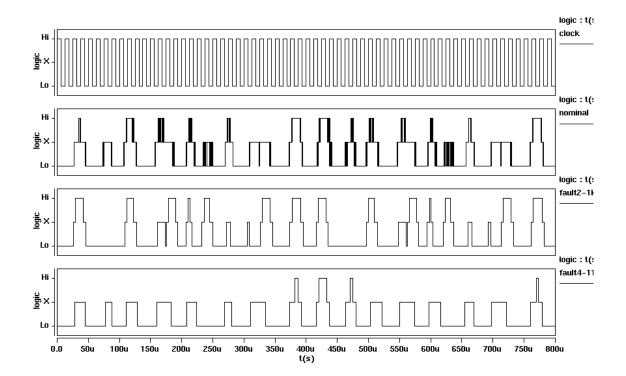

| Figure 4.2.2.1 Exemplary analog signal and its digital waveforms                         |

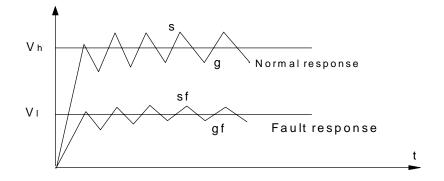

| Figure 4.2.2.2 Input and output signal for an analog circuit                             |

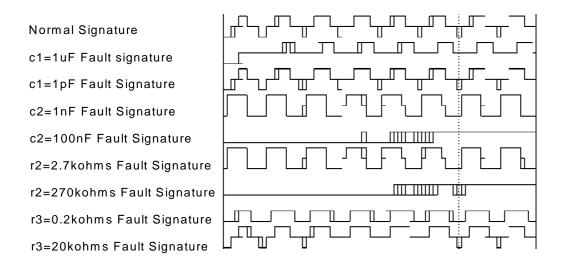

| Figure 4.2.2.3 Nominal signature and fault signature                                     |

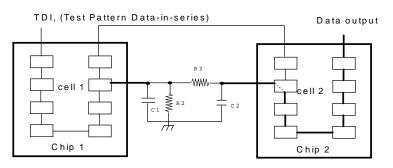

| Figure 4.2.3.1 An analog filter between two chips with boundary scan cells               |

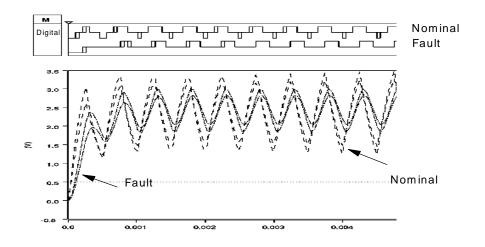

| Figure 4.2.3.2 The analog signals at analog output and their converted digital sequences |

| Figure 4.2.3.3 No fault signature vs. Fault signatures                                   |

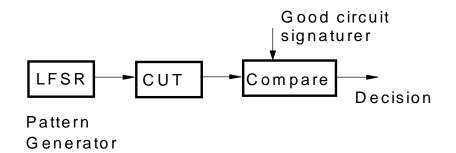

| Figure 4.2.3.4 Simulation block diagram for LFSR method                                  |

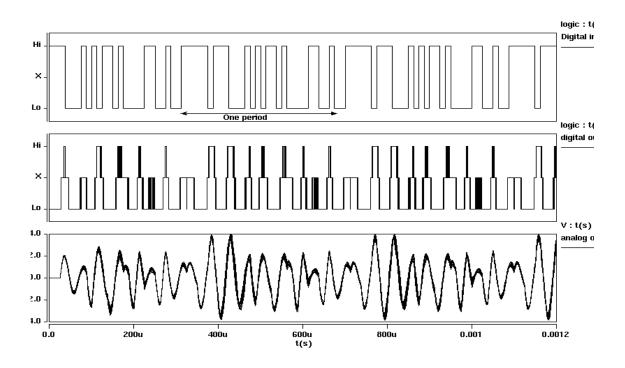

| Figure 4.2.3.5 Input digital sequence and analog output at CUT and its digital form 118  |

| Figure 4.2.3.6 Nominal signature vs. Faulty signatures II                                |

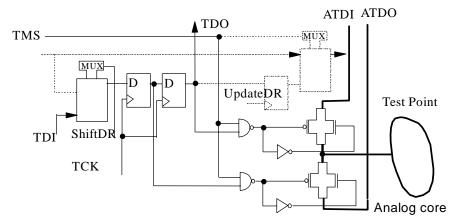

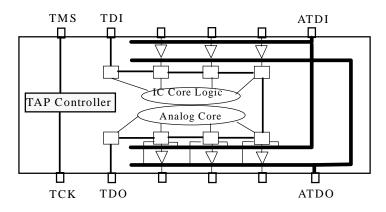

| Figure 4.3.1 An analog boundary scan cell                                                |

| Figure 4.3.2 An IC level boundary scan TAP controller                                    |

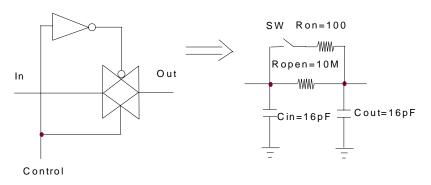

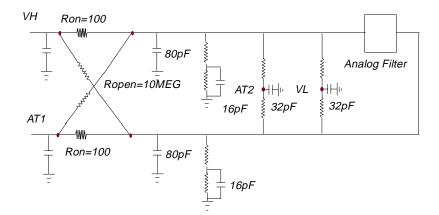

| Figure 4.3.3 Analog switch symbol and its equivalent circuit                             |

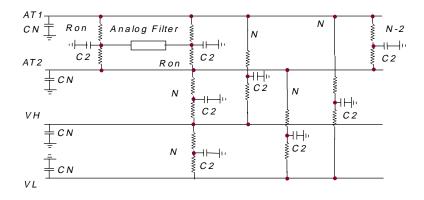

| Figure 4.3.4 The equivalent circuit for IEEE P1149.4                                     |

| Figure 4.3.5 The equivalent circuit for proposed ABSB                                    |

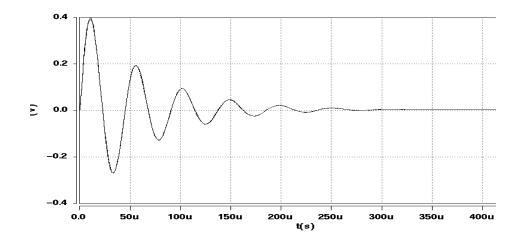

| Figure 4.3.6 Step response at analog bus AT2 vs. Direct output                           |

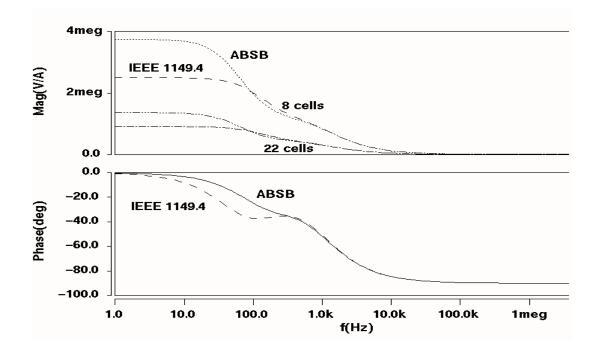

| Figure 4.3.7 $Z_{11}$ parameters for IEEE 1149.4 and ABSB with 8 and 22 cells 125        |

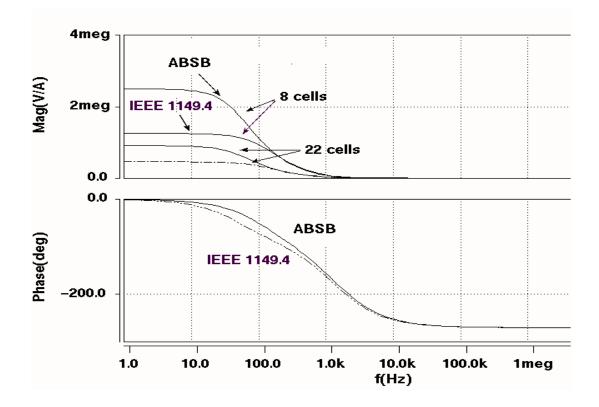

| Figure 4.3.8 Z <sub>12</sub> parameters for IEEE 1149.4 and ABSB with 8 and 22 cells 126 |

# List of Abbreviations

| ABS Antilock Brake System                    |

|----------------------------------------------|

| ABSB Analog Boundary Scan Bus                |

| AI Artificial Intelligence                   |

| AMS Analog and Mixed-Signal                  |

| AR Autoregressive                            |

| ARMA Autoregressive Moving Average           |

| ASIC Application Specific Integrated Circuit |

| ATE Automatic Test Equipment                 |

| ATDI Analog Test Data In                     |

| ATDO Analog Test Data Out                    |

| BILBO Built-in Logic Block Observer          |

| BIST                                         |

| BSD Boundary Scan Design.                    |

| CUT Circuit Under Test                       |

| CV Component Verification                    |

| DC Direct Current                            |

| DFT Design for Testability                   |

| DR Data Register                             |

| DSP Digital Signal Processing                |

| DV Design Verification                       |

| ED Euclidean distance                         |

|-----------------------------------------------|

| EMC Electromagnetic Compatibility             |

| EOL End-Of-Line                               |

| FFT Fast Fourier Transformation               |

| FSM Finite State Machine                      |

| IC Integrated Circuit                         |

| ICT                                           |

| IR Instruction Register                       |

| JETAG (JTAG) Joint European Test Action Group |

| LFSR Linear Feedback Shift Register           |

| LSSD Level Sensitive Scan Design              |

| MA Moving Average                             |

| MCM Multi-Chip Modules                        |

| MD Mahalanobis Distance                       |

| PCB Printed Circuit Board                     |

| PAM                                           |

| PPM parts per millions                        |

| PWM                                           |

| PRSG Pseudo Random Signal Generator           |

| PSD Power Spectrum Density                    |

| PWB Printed Wire Board                        |

| R&D Research and Development                  |

| RF Radio Frequency          |

|-----------------------------|

| SAT Simulation After Test   |

| SBT Simulation Before Test  |

| SMD Surface - Mount Devices |

| TAB Tape-Automated Bonding  |

| TAP Test Access Port        |

| TCK                         |

| TDI                         |

| TDO Test Data Output        |

| TMS Test Mode Select        |

| TRST                        |

### **Chapter 1 Introduction**

Electronic applications have become ubiquitous in industry, science, and everyday life. As modern applications demand greater complexity and smaller packaging, testing will be even more critical. But by the nature of this evolution the methodologies for testing in turn become a greater challenge.

Contemporary technological trends in the electronics industry include surface-mount devices (SMD), tape-automated bonding (TAB), miniaturized components, multi-chip modules (MCM), and application specific integrated circuits (ASIC).

When electronic testing is used in industry it can have numerous benefits. It assures product quality when implemented during key phases of product development. It provides an effective method for concept proving, design validating, and process checking. It also serves as a major determining factor in product time-to-market.

Electronic tests are system-dependent and are classified as either digital, analog, or mixed-signal. Current methodologies for the testing of digital circuits are well-developed. These include D-Algorithm [AIR83], Level Sensitive Scan Design (LSSD) [EIC77], IEEE Standard 1149.1, and Built-in Logic Block Observer (BILBO) [KOE79].

By contrast, methodologies for the testing of analog circuits remain relatively underdeveloped due to the complex nature of analog signals. Present strategy in industry is "to make analog periphery very, very small " [DES93]. But if the applications in digital electronics are so successful and dominant, then why is there still a need to study analog and mixed-signal testing? Stated simply, analog circuitry is where the digital and analog worlds meet.

In a primarily digital system, analog circuitry is where speech signals are converted to digital signals, sensor signals are conditioned into microprocessors, digital bit streams are converted to RF (Radio Frequency) modulation patterns or horizontal scan lines on a computer graphics screen, and microprocessors send control signals to actuators.

Even with a pure digital board there still exist power supplies, pull-up resistors to do level shifting, and capacitors for EMC (Electromagnetic Compatibility) testing. All of these discrete components on a board need to be tested in manufacturing and "when digital clock rates get really high, the 0's and 1's don't have real meaning anymore. The behavior is essentially analog." [DES93] Therefore the importance of analog testing is increasingly significant.

In addition to pure digital circuitry, analog and mixed-signal (AMS) integrated circuits and modules are widely used nowadays. Integrated circuits (IC) with digital, analog, and mixed-signal circuits on the same substrate are common [ISM94]. The applications for AMS include consumer electronics, wireless communications, networking, multimedia, automotive, process control, and real-time control systems.

With such wide applications, AMS circuits will be the mainstream of future electronics, making it imperative to research AMS testing, including digital and analog testing. But because methodologies for the testing of analog circuits are so far behind their digital counterpart, they become the bottleneck in AMS testing. The objective of this dissertation then is to study AMS testing.

New AMS test methodologies need to be compatible with existing digital testing and

be practical in compromising test coverage and test economics. Therefore basic industry test issues are presented in section 1.1 before the motivation of the main thesis in section 1.2.

### **1.1 Basic test issues**

Any specific test method is only suitable in a particular case. To develop the best test strategies, it is necessary to know where, when, and what to test. Let us first address the where-to-test question. Tests can be performed at multiple phases of a product such as in Design Verification (DV), manufacturing, or field services. DV is used in the Research and Development (R&D) phase. Its major function is to check whether the design meets the specification requirements under all possible application conditions (such as temperature, humidity, component variations, etc.). Manufacturing testing is used in the production phase. Its function is to check the manufacturing process so that the faulty modules are rejected. In the field and service phase, testing is needed to provide satisfactory services to the customers by locating faults and replacing the faulty components with good ones as soon as possible.

Different test strategies are used in the three product phases, but the best practice is to have a unified methodology which can be used throughout the life of a product. This can be achieved by following the Design for Testability (DFT) guidelines (i.e. the IEEE standard 1149.1 [IEEE1990]). While DFT is mainly used in manufacturing testing to replace In-Circuit Testing (ICT), DFT can also be used in other phases.

When to test is critically important to test economics. Electronic tests can be performed at several levels including wafer level, package level, module level, system level, even in the field service level. The actual cost for the manufacturer at each level roughly follows the multiple of ten rule. For example, the approximate cost for a company in detecting a fault is one to ten cents at the wafer level, ten cents to a dollar at the package level, one to ten dollars at the board level, ten to a hundred dollars at the system level, and one hundred to one thousand dollars in the field service level respectively [WIL86]. Therefore, a fault should be detected as early as possible. Even though it is better to find a fault earlier, some later process changes may introduce additional failures. Therefore, an optimization of testing effort or some compromise should be incorporated in the test procedures.

What faults to test question addresses various categories of test procedures. Tests can be classified into fault detection, fault location, or fault prediction. In the manufacturing process or during maintenance, a quick check is needed to pass the good parts and reject the bad parts for maximum product throughput. So, only fault detection is needed to evidence the faults. At other times, fault location is needed to detect failed modules or components for repair. The faulty components may be a functional block, a failed module, or a failed component. Fault prediction is used mainly with highly reliable products or safety related products (i.e. in avionics and antilock brake system (ABS) modules in automobiles). Fault prediction continuously monitors the circuit under test (CUT) to identify whether any of the its elements are about to fail allowing for a preventive repair.

The choice between fault location and fault detection creates compromises to be made. Fault location needs better isolation of the components and provides better test coverage. It may be used at both assembly lines and repair stations, but it may slow down the testing process and the throughput. One must keep in mind that the purpose of testing is to help improve product quality. If a manufacturing process has good parts with a low PPM (parts per millions) defect rate, only fault detection is needed and the faulty products can be sent to the repair station or thrown away depending on the repair cost. If a manufacturing process has poor performance and a high PPM defect rate, it is too expensive for the manufacturer to throw away the faulty parts. In order to repair them, fault location is needed. The IEEE 1149.1 standard can provide a decent fault isolation. But for mixed-signal testing, the proposed IEEE P1149.4 standard is still not widely used. In order to locate every fault, most nodes need to be accessed in the network, a requirement which may be impossible to meet in modern fabrication process.

What to test also addresses the types of tested circuits. This includes testing of IC chips and the PCB (Printed Circuit Board). Testing of a chip includes checks for manufacturing defects like layer-to-layer shorts, discontinuous wires, and thin-oxide shorts to the substrate or the well. Testing of a PCB involves testing for manufacturing process defects, component defects, and solder defects. The process defects include wrong, missing, reversed, misplaced parts as well as SMD on edge, SMD tombstone, SMD extra placement, SMD inversed part, and the process damage. The component defects include poor soldering, defective parts, open PWB (Printed Wire Board) traces, and IC lead coplan. Manufacturing defects include no solder, insufficient solder, solder balls, solder voids, excess solder, and shorts. The following classifies the faults.

### **Classification of Faults**

- Deviation Faults those which deviate from acceptable values of the parameters in a continuous manner into unacceptable value ranges

- Catastrophic Faults those which refer to sudden or large variations of the parameters, e.g. short and open.

- Single or Multiple Faults single faults pertain to only one parameter at a time, while multiple faults relate to several parameters or components simultaneously

The current approach to detect manufacturing faults in today's PCB industry uses several forms of Automatic Test Equipment (ATE): bare-board testers, ICT testers, and functional testers. After fabrication of a raw unassembled board, bare-board testing is done for open-etch circuits between nodes by forcing a voltage onto one circuit node and sensing the voltage at other circuit nodes. After board assembly, the ICT is done to check for part orientation, part value, part type, and correct solder joints between all parts on the PCB. Software models of each part on a board are used to generate the test patterns used by the in-circuit tester. The main assumption is that both the board and in-circuit testers require physical access to nodes or points on the board in order to perform the necessary testing. A functional tester is usually customized to a particular product. Usually, it tests the circuit through edge-connectors. Both bare-board and in-circuit testers require the ability to inject a voltage or current onto a network and sense the voltage or current at another point on the network. But the shrinkage in dimension of PCB board and the application of SMDs make

it impossible to access every test point by an in-circuit tester. Therefore, alternative methods must be found to address these challenges. IEEE standard 1149.1 [IEEE90] and IEEE proposed standard P1149.4 [IEEE96] are such alternatives which provide virtual probes. With more and more functions integrated into chips, PCBs tend to have simple structures. A typical configuration has the microprocessor in the center and all input-output circuits in the peripheries. In Section 3.1, a component verification approach is described to test such simple modules through edge connectors.

By now, new microprocessors and ASIC start to incorporate boundary scan designs (BSD). BSD is a structured test technique where shift registers and latches are placed at the functional I/Os (Input/Output) of an IC. Each I/O pin can be driven to a known state or its current logic level can be captured and scanned out via a proposed four-wire serial bus. The test bus and protocol as well as the behavior of the boundary cells are defined in IEEE Standard 1149.1. BSD was developed to test IC interconnects on PWBs when physical access test points are impossible, difficult, or impractical. As the IC pin counts increase, pin spacing decreases, and pin accessibility disappears, therefore BSD is playing an increasingly important role in design verification and manufacturing.

BSD must be optimally designed to maximize the benefits of its use. There are usually many factors that determine to what degree the BSD is needed on a PWB. Lack of physical access is the number one reason to use BSD regardless of the cost/benefit tradeoff. Test development time and costs as well as fault isolation requirements justify the cost of adding the BSD. Test equipment costs and test execution time also help to justify the added cost of BSD. On the other hand, BSD is not cost effective for some consumer products such as automotive applications, where even one dollar increase per module adds up to a huge sum of money because of the production volume. In this case, the benefits of BSD can only be realized by considering time-to-market, customer satisfaction, and system integration. For an end product such as an automobile, subsystem manufacturers are known as suppliers. For a subsystem manufacturer, module manufacturers are suppliers. For a module manufacturer, chip manufacturers are suppliers. The business relationship between assemblers and suppliers is one where both parties need to profit. The buyers need to buy cheaper while the suppliers tend to sell expensive. So, it is very hard to justify the cost effectiveness of BSD from a single manufacturer. In order to utilize BSD in every stage of the product, collaborations between different parties are needed. Therefore, the primary driving force behind BSD is a reduced time-to-market it offers. If automobile manufacturers shorten their design cycle to a certain number of months (currently 15 to 24 months), the suppliers have to choose BSD to meet the deadlines.

The secondary purpose for using BSD is customer satisfaction. If automobile owners require time-sensitive repairs, the suppliers have to use the BSD.

The third reason for using BSD is system integration. If manufacturers and suppliers consider themselves as one unit, some compromise can be achieved to solve the cost problems.

In the above section, some basic test issues are summarized and modern trends in testing are discussed. In the following section the research topics addressed in this dissertation will be introduced.

### **1.2 Introduction of the dissertation topics**

The objective of this dissertation is to improve mixed-signal testing of analog integrated circuits and modules under constraints of manufacturing industries. These constraints include testing cost and reliability, testing time and accessability of tested components, as well as IEEE standards and industrial practices. In particular, two major topics are researched -testing strategies in mixed-signal circuits which include test point selection and the innovative use of boundary scan techniques for both digital and analog circuits to improve mixed-signal testing. Motivation for this work was driven by author 's involvement in research and testing work at automotive microelectronic industry.

Electronic Testing is beneficial for detecting defects and assuring quality, but it impacts production costs and time-to-market. A favorable solution is to have one methodology which can be reused in testing chips, modules, and systems.

IEEE boundary scan standard provides such methodology but the additional cost of its integration may not be seen as offsetting its benefit. The inaccessibility of test nodes and lengthened development lead time are major concerns, and in analog and mixed-signal testing those concerns are heightened.

Some of the difficulties in analog testing include spawn from the analog signal inherent nonlinear property, the lack of proper fault models, susceptibility to distortion, measurement errors, and node inaccessibility. Analog testing has become the bottleneck of mixed-signal testing, and analog diagnosis is reviewed in Section 2.0.

Since large analog circuits are cumbersome to test it is necessary to divide the

network into smaller sub-networks. The network can be partitioned according to circuit functionality, macro cells, or test algorithms which have been developed for optimum test point selection. Three approaches to analog test strategies are discussed in chapter 3. In the first two approaches, it is assumed that a partition has been made, while the third approach tries to find the best partition.

The first approach, component verification (CV), is geared toward the manufacturing testing of a special family of PCB boards used in automotive and computer peripherals. The modules have a simple circuit structure and are produced in large quantities. It is not cost effective to apply IEEE 1149.1 or IEEE P1149.4 to these PCB boards, thus a single station replacing current ICT test and functional testing is suggested. Based on computer simulations and component tolerances, the CV approach through edge connectors can be implemented. To ensure fault detection, a corresponding testability measure based on sensitivity analysis is used. It can be implemented in the design stage as additional restraints and DFT guidelines. A special methodology to measure and calculate pull up circuitry will be discussed as an example. In the first approach, test nodes are selected through edge connectors and test frequencies are selected heuristically. The test limits are checked in several frequencies. To increase test resolution, combined test limits from various frequencies are used.

To provide a single metric for multifrequency test, the second approach uses Mahalanobis Distance (MD) criteria. MD method is used in pattern recognition and it also can be used in fault diagnosis or fault detection. It is the expansion of the first approach and superior to the simple CV approach. MD measures can be used in the domains of both frequency and time. However, the application of MD in frequency domain does not provide a method to determine optimal test points, thus various simulations must be performed.

Another way to determine optimal test points is an information-based approach which will be explored in section 3.3. The time-domain approach of MD measures is a way of avoiding test point selection. In this approach, a digital signal processing (DSP) based scheme is suggested. The ARMA (autoregressive moving average) parameters are solved using sampled discrete points. This is essentially equivalent to frequency sweep instead of a few selected frequencies depending on sampling rate. The MD measure of AR (Autoregressive) parameters are then used. The proposed method is as suitable in both manufacturing testing as it is in on-line testing. The advantage of using the MD in time domain is improved selection of time and frequency measurements. The proposed method is generic and has been programmed into SABER software package.

The third approach is information based, which is an excellent method for test-point selection in decision-table applications. Rough set theory is also used for better understanding of the problem. The effectiveness of such an approach has been proven through computer simulation with 200 randomly selected matrices.

The modern trend in testing is to use boundary scan and DFT methodologies. In Section 4, mixed-signal testing and boundary scan tests are studied. The background and brief description and the IEEE Standard 1149.1 are presented first. Numerical equations are then developed to determine if delay information can be used to verify analog components. The analytical equations for the first order charge/discharge equations are later derived as the guideline for waveform design.

Analog component testing with the IEEE standard 1149.1 is discussed in Section 4.3. By selecting the correct pulse-train clock and duty cycles, proper 1 and 0 sequences can be observed. The most attractive method is to use input from a pseudo random signal generator (PRSG). This would provide an application for the completely digital testing of mixedsignal systems.

By the end of Section 4, an analog boundary scan bus (ABSB) and virtual probe test bus for mixed-signal testing is proposed. The IEEE P1149.4 boundary scan test bus is also discussed. The boundary scan test fixtures can be used in both chip fabrication and board manufacturing. Considering the contemporary use of cell-based designs, how to test analog cells or macro cells more effectively is sometimes more important than the circuit partition. The limitation of IEEE 1149.4 is also presented by computer simulation. Simulation results are provided in each chapter.

#### **Chapter 2 A Review of Analog testing**

Mixed-signal testing includes analog and digital testing. In digital testing, the fault models are clearly defined by stuck-at-fault [ABR90], and the scanning and storage of digital signals are easily accomplished by using shift registers. As a result, the IEEE Standard 1149.1 is a very successful DFT strategy. However in analog testing, there is no such effective methodology. The analog fault model is not clearly defined, the scanning and storage of analog signals are almost impossible, and the IEEE Proposed Standard P1149.4 is far from practical for most applications. Therefore, the bottleneck of mixed-signal testing is analog testing. It is necessary to review previous works and to find out why it is difficult to perform mixed-signal testing, what has been previously done, and what can be done in the future.

Analog fault diagnosis has been researched for more than 30 years. Even though analog circuits came into existence well before the advent of digital circuits, the development of analog testing can not match its digital counterpart. One reason is the lack of proper models like stuck-at-zero and stuck-at-one models used in digital testing. The nonlinearity, the continuous characteristics, the broad range of frequency components, the high sensitivity to loading, the easiness to distort internal signals, and the component tolerances make testing of analog circuits even more difficult.

Two outstanding reviews of analog diagnosis were presented by P. Duhamel et al. [DUH79] and J. Bandler et al [BAN87]. Duhamel et al. reviewed and assessed the techniques available before 1979 for automatic test generation of analog systems by classifying different methods and providing an extensive bibliography. Bandler et al. summarized various fault location techniques and algorithms developed before 1987 and added most algorithms developed after 1979. They discussed the fault dictionary approach, the parameter identification approach, the fault verification approach, and the approximation approach. Two books covered representative methodologies in analog fault diagnosis [LIU91] and modern approaches to mixed-signal testing [VIN98]

The measures of testability and the degree of algorithm complexity are the basic theoretical topics for fault diagnosis. The testability studies tell whether the CUT is testable or not for a given methodology, while the degree of complexity tells the effectiveness of the proposed algorithm. Both are related to the specific algorithms and the ways the test equations are formulated. Their effectiveness relates to the kind of faults being targeted. The testability measures can be defined in DC, frequency domain, and time domain.

Analog circuit diagnosis methods are generally classified into simulation after test (SAT) and simulation before test (SBT) [DUH79][BAN85]. SAT methods focus on parameter identification and fault verification and they are very efficient for soft faults diagnosis because they are based on a linearized network model. However, the major problem in parameter identification is the ability to access test points. Very often, there are not enough test points to test all components or each added test point is too expensive to accept. As an alternative, the fault verification method addresses the problem of limited number of measurements, in which, not all parameters of the circuit can be identified at a time. This method assumes that only a few components are faulty and the rest of the network components are within design tolerances.

Faulty components are identified by checking the consistency of certain network equations. The ability to test multiple faults is limited by large number of choices of faulty components, which result in the combinatorial explosion for large designs. The SAT approaches have the disadvantage of high on-line computational complexity, inability to deal with catastrophic faults with ease, error prone to component tolerances, and high numerical sensitivity. To compromise test coverage and test simulation, SBT methods emphasize on building a fault dictionary in which the nominal circuit behaviors in DC, frequency, or time domain are stored. In the test stage, the measured circuit behavior is compared with the nominal case and the faults are diagnosed. In manufacturing testing, a DC test is reliable and effective. However, when higher test coverage is needed, a frequency test or a time domain test may provide more information about the circuit under test without adding test nodes. In the following sections, two most representative methods in SAT namely parameter identification and fault verification are discussed. This is followed by discussion of the SBT methods.

### 2.1 SAT methods

The first task of parameter identification technique is to formulate a sufficient number of independent equations from the measurements to determine all component values. A component value that lies outside the design tolerance range specification is identified as a faulty component.

R.S. Berkowitz [BER62] introduced the concept of network-element-value solvability

by presenting the necessary conditions for passive networks in 1962. Even without an algorithm, Berkowitz's studies heralded a new research area, analog fault diagnosis. Saeks et al. [SAE72] proposed a method to determine parameter values using voltage and current measurements, when a single excitation is applied. Multiple current excitations are applied to a network and voltage measurements are used to identify network parameters by Biernacki and Bandler [BIE80a]. Biernacki and Starzyk [BIE80b] gave test conditions which are sufficient conditions for network solvability problems. T.N. Tricks et al. [TRI79] researched the necessary and sufficient test conditions for a single test frequency and introduced the adjoint circuit concept into fault diagnosis. In Tricks's study, the branch voltages of the unknown components should be available so that the components can easily be solved by a linear method. N. Navid and A. N. Willson [NAV79] have given the necessary and sufficient conditions for the element-value solvability of a linear resistive network. They show that one can determine if it is possible to compute the element values from the test terminals by considering only the circuit's topology. Ozawa and Kajitani [OZA79] studied the problem of diagnosability of linear active networks using a voltage and current graph. Starzyk et al. [STA84] used Coates graph and presented topological and graph-theoretical conditions to determine the required number of excitations and voltage measurements for evaluation of faulty elements within a sub network. T. Ozawa et al. [OZA83] researched generalized Y- $\Delta$ transformation with a voltage controlled current source and its application to element-value solvability problems. The inaccessible nodes in a network are eliminated one by one by the transformation and a sequence of networks are obtained. They researched the backward process of Y-A transformation to determine the solvability problem. Visvanathan and

Sangiovanni Vincentelli [VIS81] developed a theory for the diagnosability of non-linear circuits with DC inputs. They derived conditions for the local diagnosability and showed that for diagnosable systems, it is possible to obtain a finite number of test inputs that are sufficient to diagnose the system.

All of the methods mentioned above deal with DC domain or single frequency excitation. The multifrequency techniques include research on the test point selection and test frequency selections. R. Saeks [SAE77] introduced a testability measure via multifrequency measurements for linear systems and its applications to test point selection. His approach was further discussed by Sen and Saeks [SEN79], and Chen and Saeks [CHEN79]. Saeks' measure is appealing because it provides a quantitative measure of testability and it results in an efficient computational algorithm. R. Priester et al. [PRI81]] proposed a testability measure based on optimal experiment designs borrowed from system identification theory. Priester's measure provides more information on the degree of difficulties about the testability. Rapisarda and Decarlo [RAP83] proposed the tableau approach with multi-frequency excitation for analog fault diagnosis instead of transfer function oriented algorithms. A. Abderrahman et al. [ABD96] used optimization techniques to generate multifrequency test sets for parametric and catastrophic failures. Sheu and Yuen [SHEU96] proposed an efficient frequency domain relaxation pseudo-circuit approach and the associated solvability conditions with reduced dimension and practical implementation scheme.

The time domain approach includes formulating solvable equations which are testable from time domain measurements. R. Seaks et al [SAE81] published an excellent work on

dynamic testing. They extended their diagnosability theory for linear systems [Sen79] and memoryless nonlinear systems [VIS81] by presenting a necessary and sufficient condition for the local diagnosibility of nonlinear dynamical systems. Based on a discrete-time circuit description, V. Visvanathan [VIS84] derived a necessary and sufficient condition for the local diagnosability of a class of nonlinear dynamical circuits whose branch relations are analytic functions of their argument. H. Dai [DAI90] proposed an efficient approach for functional testing and parameter estimation of analog circuits in time domain based on a sensitivity matrix. Salama and Amer [SAL92] developed a technique based on identifying the discrete time transfer function coefficients of the circuit under test from time domain response. Walker et al. [WAL92] developed a two stage SAT fault diagnosis technique based on bias modulation. The first stage, which diagnosis and isolates faulty network nodes, resembles the node fault location method [HUA83]. The second stage, a sub-network branch diagnosis extracts faulty network parameters. The branch diagnosis is achieved by element modulation, a technique to vary the value of the element externally as a modulated element.

The works discussed so far focused on the parameter identification method. The fault verification methods use almost the same equations as are used in the parameter identification approaches, except that in the fault verification approaches, circuit components are partitioned into two groups, a fault-free group 1 and a faulty group 2. It is assumed that all components in group 1 are fault-free and all faults are localized in group 2. Using the measurement data and the nominal characteristics of all circuit components test equations are formulated and expressed as functions of deviations of group 2 components.

Test equations are overdetermined and can be satisfied only if all faults are indeed localized in group 2. Thus the technique of making assumptions on faults and checking their validity is called fault verification.

Another quantative testability measure which is based on sensitivity was introduced by Temes [TEM77] and was further studied by Dejka [DEJ77]. Skala [SKA80] studied a sensitivity algorithm for checking the consistency or inconsistency of certain linear equations which are invariant on fault elements. H. Dai [DAI90] proposed a testability measure using time domain sensitivity equations. Slamani and Kaminska [SLA92] used sensitivity equations and optimization method for selecting test sets.

From the topology point of view, Z.F. Huang et al. [HUA83] introduced k-node-fault testability in 1983. In their studies, node-voltages and nodal equations are used. The beauty of their testability condition is that it depends only on the graph of the circuit instead of the component values. C.S. Lin et al. [LIN83] studied the topological conditions for single-branch-fault. Maeda et al. [MAE86] presented necessary and sufficient analytical as well as graph theoretic conditions for fault detectability and distinguishability in non-linear systems and used these conditions to derive an algorithm for fault diagnosis. Starzyk and Dai [STA92] presented a decomposition approach for testing large scale analog non-linear networks. This was found to be superior to conventional methods using sensitivity approach.

No matter what kind of testbility measures are used, whether it is frequency domain, time domain, or topology point of view, the advantage is that the measure tells whether the CUT is testable or diagnosable. However the computational complexity is a difficult problem to overcome. In manufacturing testing, this problem becomes more severe. SBT methods provide a compromise by shifting the computational burden to simulation before test.

### 2.2 SBT methods

Martens and Dyck [MAR72] used a frequency domain approach for single element faults. They considered a transfer function as a bilinear function of network elements. Morgan and Towill [MOR77] included the higher order harmonics in the dictionary for the frequency domain response of the network. Varghese et al. [VAR79] utilized the Euclidian norm to normalize the network response deviations. Lin and Elcherif [LIN85] considered DC inputs to build the fault dictionary. Seschu and Waxman [SES86] employed a frequency domain approach to construct a fault dictionary of a linear frequency-dependent circuit.

Time-domain analysis approaches were also studied to construct the fault dictionary. Pseudo-noise signal inputs are used by Macelod [MAC73]. For each faulty condition, the deviation in the impulse response of the network is computed using a periodic pseudo-noise signal as excitation. These deviations are quantized and are stored in the dictionary. Schreiber [SCH79] proposed the test signal design method to construct the fault dictionary. In this, the loci of all single-element drift failure fault signatures are drawn in the augmented signal space to generate the fault dictionary. Wang and Schreiber [Wan79] utilized a complementary signal approach for go/no-go testing of a partitioned network under test. Balivada et al. [BAL96] have studied the effects of various stimuli on the variations in delay, rise time, and over shoot that indicate faulty behavior. M.A. AI-Qutayri [AI92] presented a time-domain go/no-go testing strategy for analog integrated circuit macros. His strategy is based on exciting an analog macro with a pseudo-random binary sequence and measuring the transient response at the external nodes. With an increasing number of macro based designs in application, testing macros becomes attractive and necessary.

Different types of measurements were used in the literature to construct the dictionary. The widely used measurements are node voltage [HOC79][LIN85], magnitude and phase of node voltages [PAW82], and voltage/ current measurements [RUT94]. Power supply current and voltage measurements are also used by Papakostas and Hatzopoulos [PAP94] who suggested power supply current measurements in linear bipolar ICs for fault detection. Somayajula et al. [SOM96] proposed construction of fault dictionaries from the currents in the power supply bus. A ramping power supply is applied at the DC power supply inputs to force the transistors in the circuit to operate in all possible regions. Then, the signatures are clustered into different groups using a Kohenen neural network classifier. Aain et al. [AAI94] suggested testing of analog circuits by power supply voltage control. The power supply voltage was varied and output voltage was measured for the opamp circuits to detect faults, which were otherwise difficult to find with conventional input signal excitation. They also discussed [AAI96] application of AC power supply voltage and compared the fault coverage of voltage level and supply monitoring schemes. In addition, they discussed the effect of changing the power supply frequency on the testing of analog Ics.

Artificial intelligence (AI) and neural network methods and are also used in analog fault diagnosis especially in SBT methodologies [BER96][MAT96][HAT89][MAN90]. Hatzopoulos and Kontoleon [HAT89] proposed a method which provides the knowledge base to the computer with qualitative and quantitative, nominal and faulty, element models and their possible failure symptoms. Manetti et al. [MAN90] proposed methods to generating methods to generate test point selection using AI techniques, based on a knowledge based constituted by simple rules derived from experience and heuristic reasoning. Based on the back propagation paradigm, several authors studied analog fault diagnosis [RUT94][WU94][YU94] [SPI97]. Rutkowski [RUT94] employed backpropagation network for locating faults in a non-linear dc circuit. Yu et al. [YU94] proposed the neural network approach for the fault diagnosis of CMOS Opamps with gate oxide short faults. In this case neural network is trained to respond for the variations in supply current. Wu and Meador [WU94] suggested a feed forward neural network approach for IC fault diagnosis in a large scale production testing environment. However all these methods present the problem of long training time to converge, even with a relatively small number of training samples.

Probabilistic and statistical techniques were proposed by some authors for analog fault diagnosis [KRA63][PRI81][FAV91][EPS93] [CHA97][DEV96]. Kranton and Libenson [KRA63] developed a probabilistic technique for single faults. In their studies, all possible faults were characterized statistically using Monte Carlo simulation and stored as a data base similar to fault dictionary. At the time of testing, the probability for each individual element to be faulty was computed using a limited number of measurement and the stored data base. Epstein et al.[EPS93] presented statistical techniques using discrimination analysis and hypothesis testing for fault detection and classification in linear integrated circuits. Favalli et al [FAV91] presented a probabilistic approach to detect analog faults that depends on the conductances of faulty and fault-free networks. Using this they gave methods to find

detection probability of each fault and the expected coverage of analog faults. Gielen et al [GIE96] suggested to use A-priori simulated probability information combined with actual measurement data to decide whether the circuit was faulty or not.

The research results discussed provide theoretical basis for analog fault diagnosis. The basic idea of analog fault diagnosis is to formulate equations based on circuit topology and voltage/current measurements so that the desired testability is reached. Unfortunately, most algorithms can not avoid the computational complexity problem, therefore they are rarely used in practice. The most practical methods in analog fault diagnosis are simulation and the fault dictionary approach.

A fault dictionary constructs a look up table, which lists each faulty case and nominal case for comparison purpose. The objectives of fault detection or diagnosis must be clear because they are critical aspects for deciding the fault detection or diagnosis capability of the dictionary. They also have an impact on the size of the dictionary and impose a limitation on the dictionary approach. Too broad fault coverage may end up with prohibitive large number of combinations which may not be realized algorithmically, while too narrow fault coverage may not meet the quality target. The anticipated faults and the nominal circuit of the CUT need to be simulated in order to develop sets of stimuli and responses to detect and isolate the faults. To generate a reasonable fault list, physical failures and failure modes have to be related. In order to develop a fault dictionary with real physical meaning, failure modes and physical failures are discussed in the following section.

### 2.3 Failure Modes and Mechanisms for electronic components

In constructing a fault dictionary, fault simulation is widely used in choosing the test strategy. Some methodologies use schematics as the starting point to generate fault lists in fault simulation. For example, when a fault list is generated, every component is either shorted, opened, shorted to power, shorted to ground in single fault situation, or a large number of different fault combinations are considered in multiple fault cases. The disadvantage of doing so is that it neglects the physical layout information of the circuitry and hence it could generate some unrealistic faults in the lists or a prohibitively large fault Therefore, very often a single fault assumption is made. Unfortunately such lists. assumption is often invalid. For instance, a single cut line across a PCB generates multiple faults. The drawback of schematic based fault list generation without layout, material, and process information is that some of the faults generated are not likely to exist in the real world. Therefore, simulation time and effort are wasted. Another problem in schematic based fault generation without layout information is its inaccuracy in fault models. For example, in CMOS short circuit simulation, a short between nodes should be a proper resistor between nodes instead of zero resistance [WAL86], especially in an integrated circuit [HAR94] [OLB96]. Therefore, it is advantageous to study testing by relating the system specifications to details of the layout and process. It is necessary to investigate correlations between fault models and physical failures. Based on the probability of the occurrence of physical failures and the fault behaviors caused by such failures, a realistic fault list can be generated and the fault models can then be built. In what follows, failure mechanisms with electrical behavior and fault models for simulation are discussed.

Let us look at failure modes and mechanism first. A failure mode is the effect by which a failure is observed, while a failure mechanism is the chemical, physical, or metallurgical process which leads to component failure [JEN95]. In electronic components, there are basically different failure modes namely, open circuit, short circuit, degraded performance, and functional failures. The relative occurrence of failure modes in some electronic components were summarized by A. Birolini [BIR94] as shown in Table 2.3.1.

## Table 2.3.1 Relative occurrences of failure modes in some electronic components

## [BIR94]

| Components               | Short % | Open % | Degradation % | Functional % |

|--------------------------|---------|--------|---------------|--------------|

| Digital, bipolar ICs     | 30      | 30     | 10            | 30           |

| Digital MOS ICs          | 20      | 10     | 30            | 40           |

| Linear ICs               | 30      | 10     | 10            | 50           |

| Bipolar transistors      | 70      | 20     | 10            |              |

| Field-effect transistors | 80      | 10     | 10            |              |

| Diodes, general purpose  | 70      | 30     |               |              |

| Zener                    | 60      | 30     | 10            |              |

| HF                       | 80      | 20     |               |              |

| SCRs                     | 20      | 20     | 60            |              |

| Optoelectronic devices   | 10      | 50     | 40            |              |

| Resistors, fixed         | -       | 90     | 10            |              |

| Variable                 | -       | 60     | 20            | 20           |

| Components       | Short % | Open % | Degradation % | Functional % |

|------------------|---------|--------|---------------|--------------|

| Capacitors, foil | 80      | 10     | 10            |              |

| Metal foil       | 40      | 60     |               |              |

| Ceramic          | 50      | 40     | 10            |              |

| Tantalum, dry    | 60      | 20     | 20            |              |

| Aluminum, wet    | 20      | 10     | 70            |              |

| Coils            | 10      | 30     |               | 60           |

| Relays           | 15      | 15     |               | 70           |

| Crystals         | -       | 80     | 20            |              |

Table 2.3.1 shows that most physical failures are open and short faults which are comparatively easier to detect than degradation and functional faults. In PCBs, approximately 75% percent of faults occur at assembly, only 20% percent are component faults, and 5% are PCB faults [Lan88]. An important application of Table 2.3.1 is to calculate test coverage and yield estimation. For instance, if the open fault for a fixed resistor can be detected, 90% test coverage for that resistor is estimated.

In addition to component failures summarized in Table 2.3.1, the failures caused by the manufacturing process are the other important factors. Table 2.3.2 shows the relative percentage of occurrence for a particular manufacturer in its process defects, component defects, and solder defects respectively.

| Process Defects                                                                                | %         | failure mode |  |  |  |

|------------------------------------------------------------------------------------------------|-----------|--------------|--|--|--|

| Wrong parts                                                                                    | 10        | V            |  |  |  |

| missing parts                                                                                  | 7         | open         |  |  |  |

| Misplaced parts                                                                                | 7         | reliability  |  |  |  |

| SMD on edge                                                                                    | 7         | reliability  |  |  |  |

| process damage                                                                                 | 3         | op/sh/v      |  |  |  |

| SMD tombstone                                                                                  | 3         | op           |  |  |  |

| SMD extra placement                                                                            | 3         | leakage      |  |  |  |

| Reversed part                                                                                  | 3         | v/op/sh      |  |  |  |

| SMD inverse parts                                                                              | v/op/sh/r |              |  |  |  |

| Solder 1                                                                                       | Defects   |              |  |  |  |

| No solder                                                                                      | 7         | op           |  |  |  |

| insufficient solder                                                                            | 7         | resistive op |  |  |  |

| Solder balls                                                                                   | 7         | sh           |  |  |  |

| Solder voids                                                                                   | 7         | resistive    |  |  |  |

| Excess solder                                                                                  | 3         | sh           |  |  |  |

| solder short                                                                                   | 2         | sh           |  |  |  |

| Componen                                                                                       | ts Defe   | cts          |  |  |  |

| Poor Sold wet                                                                                  | 10        | resistive sh |  |  |  |

| Defective part                                                                                 | 7         | op/sh/v      |  |  |  |

| open PWB track                                                                                 | 3         | ор           |  |  |  |

| IC lead coplan 2 op                                                                            |           |              |  |  |  |

| Where v=variable resistance or functional degradation,<br>Sh=short, op=open, and r=reliability |           |              |  |  |  |

# Table 2.3.2 Relative indexes of manufacturing process defects for a manufacturer

The actual percentages differ from manufacturer to manufacturer depending on the technology and manufacturing process. For each manufacturer, a table similar to Table 2.3.2 can be used as the reference for deciding the test strategy. More importantly, these figures can be used for finding problems in the manufacturing process. For instance, if one defect occurs more frequently than others, the root cause should be found and process must be improved to reduce the defect rate. As is shown, the failure mode for the listed physical failures can be used to generate a fault list in simulation. In most cases, the faulty behavior of the circuit is caused by open or short. For the wrong parts and misplaced parts which are caused by loading the wrong reel, the failure mode can be open, short, or functional degradation. However, if misplaced parts are to be detected in a ICT or a functional tester, it is too late, because ICT test is after assembly and functional test is after package. Therefore, there may be hundreds of failed parts in the assembly line. As a result, it is better to avoid these faults by bar coding the reels so that each time a reel is loaded, the bar code for the reel is checked first. In summary, the faults can be modeled as open, short, and variable component values. However component value changes are usually significant in these failure modes. As a result, a faulty value with a value ten times larger or ten times smaller is a reasonable assumption in generating the fault list. Open and short faults are only the extreme cases of these two. Therefore, if ten times larger or ten times smaller faults can be covered, the open and short faults can be detected also. Table 2.3.2 address the manufacturing process of PCBs. In what follows, integrated circuits (IC) are discussed.

In an integrated circuit, the failures could be caused by substrate, oxide, metallization,

interconnections, package, overstress [FAN85]. Table 2.3.3 shows the percentage incidence of failure allocation for several IC manufacturers.

| Failures         | Bell TTL | Bell CMOS | Bell MOS | USAF TTL |

|------------------|----------|-----------|----------|----------|

| Substrate        | -        |           |          | 4        |

| Oxide            | 20       | 1         | 75       | 27       |

| Metallisation    | 30       | 34        |          | 4        |

| Interconnections | 37       | 5         | 7        | 9        |

| Package          | -        | -         |          | 15       |

| Not identified   | 9        |           | 1        | 17       |

| Overstress       | 4        | 60        | 17       | 24       |

Table 2.3.3 Percentage incidences of failure allocations

As is shown, the failure allocation depends on technology and process. It also varies from manufacturer to manufacturer. A refined scheme is shown in Table 2.3.4. This table lists the defect, the physical failure mechanism, and the electrical effects for each failure location.

| Location                 | Defect                                                                       | Failure mechanism                                                                                                              | Electrical failure mode                                                                                                                                         |

|--------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Substrate                | Crystal defect close to junction                                             | High generation-<br>recombination<br>Low-resistance paths (CE<br>pipes)<br>Second breakdown<br>alpha particles                 | Refresh time degradation in<br>RAMs<br>Leakage/short circuit<br>Short/open circuit<br>Soft errors                                                               |

| Thin Oxides              | Traps and charges at Si-<br>SiO2<br>Interface<br>Oxide traps                 | Hot carrier injection and trapping                                                                                             | Leakage/characteristic<br>Instabilities and degradation<br>MOS threshold and<br>tansconductance degradation                                                     |

| Thin and<br>Thick oxides | None<br>Pin-holes<br>Other defects/contaminats<br>Contaminants (alkali ions) | High E-field breakdown<br>(eventually ESD)<br>Low E-field breakdown<br>Time dependent breakdown<br>Surface depletion/inversion | Leakage/short circuit<br>Leakage/short circuit<br>Leakage/short circuit<br>Leakage/characteristic<br>Instabilities and degradation<br>parasitic MOS transistors |

| Contacts                 | Surface<br>defects/nonsaturated AI<br>Oxidised surface<br>None               | Metal-Si interdiffusion<br>Electromigration                                                                                    | Leakage/short circuit<br>Open circuit/floating<br>conductors<br>Junction leakage/short circuit<br>Metal open circuits                                           |

| Conductors               | Thinging (High<br>steps.scratches)<br>None<br>None<br>Contaminats            | Joule<br>melting/electromigration<br>Electromigration<br>Overstress<br>Corrosion                                               | Open circuit<br>Open circuit<br>Short/open circuit (Bridging)<br>Open circuit (AI)<br>Short circuit (Au)                                                        |

| Multilar conductors      | AI hillocks                                                                  | Stress relief/electromigration                                                                                                 | Short circuit                                                                                                                                                   |

# Table 2.3.4 IC failures, defects, mechanisms, and electrical failure modes

| Chip-<br>package | Poor' wire bonding                            | Thermal fatigue/mechanical stress         | Open circuit                                     |

|------------------|-----------------------------------------------|-------------------------------------------|--------------------------------------------------|

| connection       | Excess' wire bonding                          | Oxide under pad break<br>AI particles     | Short circuit                                    |

|                  |                                               | Au-AI interdiffusion (purple plague)      | Open circuit                                     |

|                  | Thermal coefficient<br>mismatch between wires | Thermal fatique                           | Open circuit                                     |

|                  | and package<br>Shallow angle of wires         |                                           | Short circuit                                    |

|                  | with substrate<br>Defective die-attach        | Poor thermal conductivity thermal runaway | Characteristic degradation<br>Short/open circuit |

Table 2.3.3 and Table 2.3.4 are used similarly in IC as Table 2.3.1 and 2.3.2 in PCBs. In IC models, short and open should be considered as resistive values according to the technology and process [SAC95]. Failure mechanisms for PCB board and integrated circuits are summarized in this section. The information provided can be used for making test strategy decisions, generating fault lists, and calculating fault coverage in fault simulation. The next chapter will discuss three methods for analog fault diagnosis.

### **Chapter 3 Analog testing**

In this chapter, three test methods are studied. All three methods deal with the fault dictionary approach. The first section discusses combining functional testing and in-circuit-testing into one in manufacturing testing by component verification approach. The second section discusses Mahalanobis distance (MD) and its application to analog fault diagnosis. The proposed MD method can also be used in component verification approach. The third section discusses the reduction of test points using rough set theory and fault-wise table approach.

## 3.1 PCB board testing using the component verification approach

The PCB boards are divided into two different categories. The first kind of PCBs are the complex ones with the above mentioned components plus additional components. These boards usually require the application of the IEEE boundary scan standards. The second category is systems consist of digital cores surrounded by peripheral analog circuitry, such as filters and data converters. The analog and mixed-signal components serve as interfaces between digital processing circuitry and real world signals. The application of such systems include a board with a micro controller and its input and output circuitry. The exemplary circuitry include most data acquisition boards, engine control modules, automotive body functional control modules, ABS modules, etc. The structure of this kind of PCB board is relatively simple. The application of the proposed IEEE P1149.4 standard not only becomes cost prohibitive but also overkill. These boards are just simple enough to be tested effectively through edge connectors. The objective of this chapter is to propose a practical method for such systems with minimum test cost.

Most algorithms developed previously utilize ICT to access test points. Many test point selection algorithms were devoted to selecting a minimum set of points. However, future electronic modules are expected to present access problems for the probes in ICT testers. A way around the access problem is to add more access test points on the PCB boards based on current or new algorithms developed. The disadvantage of this is, mathematically, as the test points increase along with the number of components the cost increases as well. This additional cost can be prohibitive. Therefore, the alternative is to use BIST or test electronic modules through edge connectors only. BIST can be realized by using the proposed IEEE P1149.4 standard which is too expensive for low cost electronic modules used in both automotive and consumer electronics where cost is very important for large quantity production. In order to test the module through edge connectors, the circuitry must be simple enough to be traced from each edge connector.

The driving forces for edge connector testing are the need to find an alternative way for manufacturing in-line tests to replace ICTs, the need to have an algorithmic way of generating manufacturing testing programs, and the need to combine ICT and functional tests into one single station. Even if there are only a few test points left inside the PCB board, an ICT is still needed which results in additional testing and higher costs. So, our purpose is to eliminate the need for ICT.

One of the most successful methodologies used in PCB testing is IEEE standard

1149.1. This requires six more pins to be added to the PCB board and each chip in order to implement even the simplest IEEE standard 1149.4 test bus. It is reasonable to add more pins or BIST, if the board to be tested is complex and expensive (say over \$1000 per board). However, if the board is simple (say below \$100 per board), adding more pins or BIST will significantly increase the board cost so that the IEEE P1149.4 standard could not economically be used. Fortunately, those cheaper boards have simple circuitry and multi-port PCBs. In this case, a technique suitable for PCB testing in data acquisition boards and automotive electronics is studied.

# 3.1.1 Component verification approach [STO97]

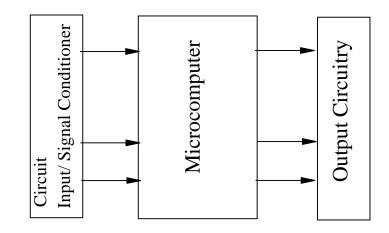

Figure 3.1.1.1 A typical board structure, used especially in automotive

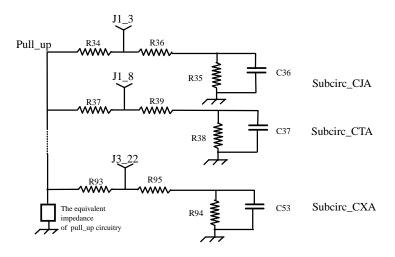

Figure 3.1.1.2 A typical input circuitry

In order to reduce the number of test access points necessary, analog functions are integrated into chips which makes the analog peripheries very small. This is the current trend in electronics. The typical circuit structure is shown in Figure 3.1.1.1 where the micro-controller is in the center of the boards with input circuitry or signal conditioner circuitry and output circuitry at the ends of the boards. The input circuit function is usually used to adjust