#### DYNAMICALLY SELF-RECONFIGURABLE SYSTEMS FOR

MACHINE INTELLIGENCE

A dissertation presented to

the faculty of

the Russ College of Engineering and Technology of Ohio University

In partial fulfillment

of the requirements for the degree

Doctor of Philosophy

Haibo He

August 2006

This dissertation entitled

#### DYNAMICALLY SELF-RECONFIGURABLE SYSTEMS FOR

#### MACHINE INTELLIGENCE

by

#### HAIBO HE

has been approved for

the School of Electrical Engineering and Computer Science

and the Russ College of Engineering and Technology by

Janusz A. Starzyk

Professor of Electrical Engineering and Computer Science

Dennis Irwin

Dean, Russ College of Engineering and Technology

# Abstract

# HE, HAIBO, Ph.D., August 2006, Electrical Engineering and Computer Science DYNAMICALLY SELF-RECONFIGURABLE SYSTEMS FOR MACHINE INTELLIGENCE (170 pp.)

Director of Dissertation: Janusz A. Starzyk

This dissertation is focused on the development of system level architectures and models of dynamically self-reconfigurable systems for machine intelligence. This research is significant for building brain-like intelligent systems. Although the development of deep submicron very large scale integration (VLSI) system, nanotechnology and bioinformatics facilitate building such intelligent systems, yet it is very challenging to study how these kinds of complex, reconfigurable systems can self-develop their connectivity structures, accumulate knowledge, make associations and predictions, dynamically interact with environment, and self-control to accomplish desired tasks.

A new framework of "learning-memory-prediction" for machine intelligence is proposed in this research, and it serves as the foundation for building intelligent systems through learning in dynamic value systems, memorizing in self-organizing networks, and predicting in hierarchical structures. These systems are characterized by on-line data driven learning, distributed structure of processing components with local and sparse interconnections, dynamic reconfigurability, self-organization, and active interaction with environment. Learning is the fundamental element for biologically intelligent systems. The proposed online value system is able to learn and dynamically estimate the value of any multi-dimensional data set, and such value system can be used in reinforcement learning. Feedback mechanism is introduced in the self-organizing learning system to allow the machine to be able to memorize information in its distributed processing elements and make associations. After the information is learned and stored in the associative memory, a biologically-inspired anticipation-based temporal sequence learning architecture is proposed. All systems proposed in this research are hardware-oriented. A novel computing paradigm that can achieve low power consumption for designing large scale, high density intelligent systems is proposed, and a brief description of the system level hardware architecture for prototyping and testing of the proposed systems is also presented.

Intelligent systems have wide applications from military security systems to civilian daily life. In this research, different application problems, including pattern recognition, classification, image recovery, and sequence learning, are presented to show the capability of the proposed systems in learning, memory, and prediction.

Approved:

Janusz A. Starzyk

Professor of Electrical Engineering and Computer Science

## Acknowledgements

I would like to take this chance to express my deepest gratitude to many people's support and help for my doctoral study in Athens.

Firstly, I would like to thank my advisor, Professor Janusz A. Starzyk, for all his supervision and advice for my research. He introduced this amazing research topic to me, and after all these years of study and research in this area, I find that nothing would be more interesting and rewarding than to devote my entire future career to this field. Throughout my doctoral research, he not only delivered the latest knowledge in this area to me and supervised my dissertation research, but also educated me about how to conduct research and how to be a creative, thoughtful, committed, and high integrity person. All of these have made a remarkable influence on my life, and I firmly believe that I will continue to benefit from these throughout my life. I will cherish forever all the happy time with him, all the meetings, conversations and discussions regarding research as well as other things, and all of these memories will become my lifetime fortune.

Secondly, I want to sincerely thank all my committee members for their suggestions and advice throughout my dissertation research: Professor Jeffrey Dill, Professor Robert Curtis, Professor Savas Kaya and Professor Xiaoping Shen. Their knowledge and comments are very important and helpful to me in developing the research presented in this dissertation.

During my four years of study in Athens, I enjoyed a happy time in our "family", the VLSI and intelligent systems research lab. I would like to thank all my officemates and teammates for their valuable comments on research, and their kind help in my daily life: Yinyin, Lily, Zhen, Mingwei, and James. We are just like a family, and I will never forget the happy time together.

Last but not least, I would like to extend my deepest gratitude to my beloved parents and sister for all their support and encouragement for me throughout all these years. They are always my strongest support, and I would like to share every single step in my life together with them.

| Acknowledgements         List of Tables         List of Figures         List of Abbreviations         Chapter 1         Introduction         1.1 Motivation         1.2 Related work: learning, memory and prediction         1.3 Significance of Research         1.4 Research goals and objectives         1.5 Dissertation Organization | 10 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| List of Figures<br>List of Abbreviations<br>Chapter 1<br>Introduction                                                                                                                                                                                                                                                                      |    |

| List of Abbreviations<br>Chapter 1<br>Introduction                                                                                                                                                                                                                                                                                         | 11 |

| Chapter 1         Introduction         1.1 Motivation         1.2 Related work: learning, memory and prediction         1.3 Significance of Research         1.4 Research goals and objectives         1.5 Dissertation Organization                                                                                                       |    |

| Introduction         1.1 Motivation         1.2 Related work: learning, memory and prediction         1.3 Significance of Research         1.4 Research goals and objectives         1.5 Dissertation Organization                                                                                                                         | 13 |

| <ul> <li>1.1 Motivation</li> <li>1.2 Related work: learning, memory and prediction</li> <li>1.3 Significance of Research</li> <li>1.4 Research goals and objectives</li></ul>                                                                                                                                                              | 15 |

| <ul> <li>1.2 Related work: learning, memory and prediction</li> <li>1.3 Significance of Research</li> <li>1.4 Research goals and objectives</li></ul>                                                                                                                                                                                      | 15 |

| <ul><li>1.3 Significance of Research</li><li>1.4 Research goals and objectives</li><li>1.5 Dissertation Organization</li></ul>                                                                                                                                                                                                             | 15 |

| <ul><li>1.4 Research goals and objectives</li><li>1.5 Dissertation Organization</li></ul>                                                                                                                                                                                                                                                  | 17 |

| 1.5 Dissertation Organization                                                                                                                                                                                                                                                                                                              | 25 |

|                                                                                                                                                                                                                                                                                                                                            | 26 |

| Chapter 2                                                                                                                                                                                                                                                                                                                                  | 27 |

|                                                                                                                                                                                                                                                                                                                                            | 31 |

| Value System for Machine Learning                                                                                                                                                                                                                                                                                                          | 31 |

| 2.1 Introduction                                                                                                                                                                                                                                                                                                                           | 31 |

| 2.2 Online dynamic curve fitting                                                                                                                                                                                                                                                                                                           | 33 |

| 2.3 Three curve fitting and voting scheme                                                                                                                                                                                                                                                                                                  | 34 |

| 2.4 System architecture                                                                                                                                                                                                                                                                                                                    | 38 |

| 2.5 Summary                                                                                                                                                                                                                                                                                                                                | 41 |

| Chapter 3                                                                                                                                                                                                                                                                                                                                  | 43 |

| Self-Organizing Associative Memory                                                                                                                                                                                                                                                                                                         | 43 |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                           | 43 |

| 3.2 Probability based associative learning                                                                                                                                                                                                                                                                                                 | 43 |

| 3.2.1 Structure of individual processing elements                                                                                                                                                                                                                                                                                          | 43 |

| 3.2.2 Self-determination of the function value                                                                                                                                                                                                                                                                                             | 45 |

| 3.2.3 Signal strength                                                                                                                                                                                                                                                                                                                      | 46 |

| 3.2.4 Probability based associative learning algorithm                                                                                                                                                                                                                                                                                     | 48 |

| 3.2.4.1 Example PE and its associations                                                                                                                                                                                                                                                                                                    | 48 |

| 3.2.4.2 Probability based associative learning algorithm                                                                                                                                                                                                                                                                                   | 49 |

| 3.3 Self-organizing associative memory structure and operation                                                                                                                                                                                                                                                                             | 54 |

| 3.3.1 Network structure                                                                                                                                                                                                                                                                                                                    | 54 |

| 3.3.2 Network operation                                                                                                                                                                                                                                                                                                                    | 55 |

| 3.3.2.1 Feedforward operation                                                                                                                                                                                                                                                                                                              | 55 |

| 3.3.2.2 Feedback operation                                                                                                                                                                                                                                                                                                                 |    |

| 3.4 Summary                                                                                                                                                                                                                                                                                                                                |    |

# **Table of Contents**

| apter 4                                                                           | 62  |

|-----------------------------------------------------------------------------------|-----|

| Anticipation-Based Temporal Sequences Learning in Hierarchical Structure          | 62  |

| 4.1 Introduction                                                                  | 62  |

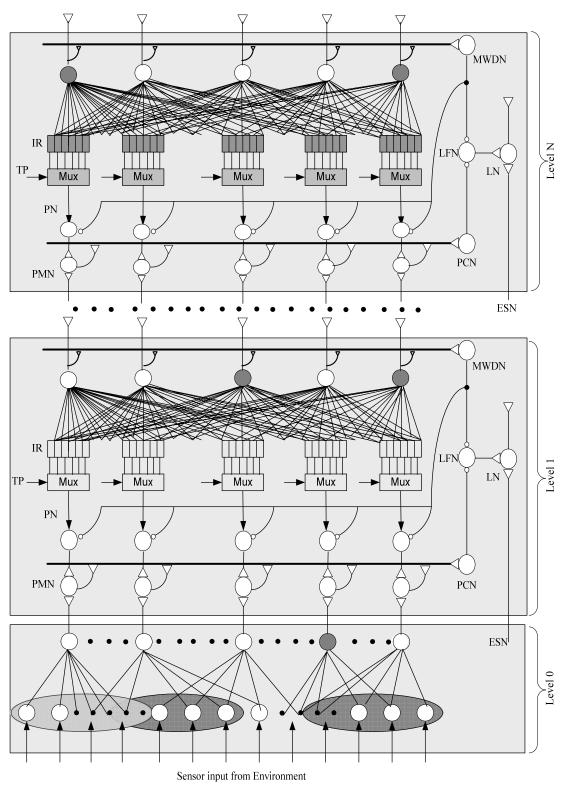

| 4.2 System architecture                                                           | 62  |

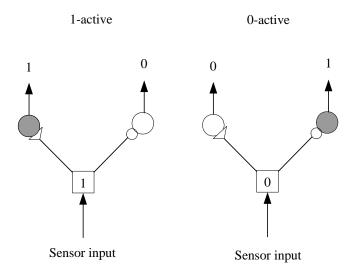

| 4.3 Level 0: A modified Hebbian learning mechanism                                | 65  |

| 4.4 Level 1 to level N: Sequence learning and prediction                          | 69  |

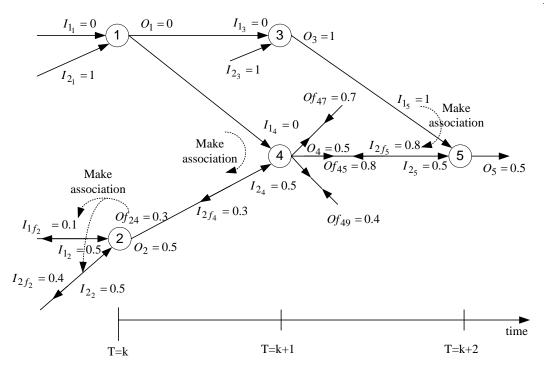

| 4.4.1 Storing input sequences                                                     | 69  |

| 4.4.2 Predicting the input sequences                                              | 73  |

| 4.4.2.1 Prediction mechanism                                                      | 73  |

| 4.4.2.2 Activation of a prediction neuron                                         | 78  |

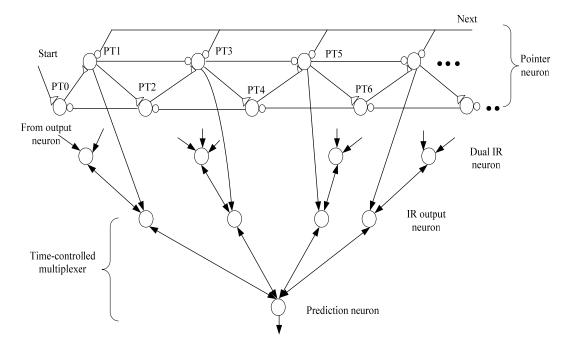

| 4.4.2.3 Time controlled multiplexer                                               | 79  |

| 4.5 Retrieval of the stored sequences                                             | 80  |

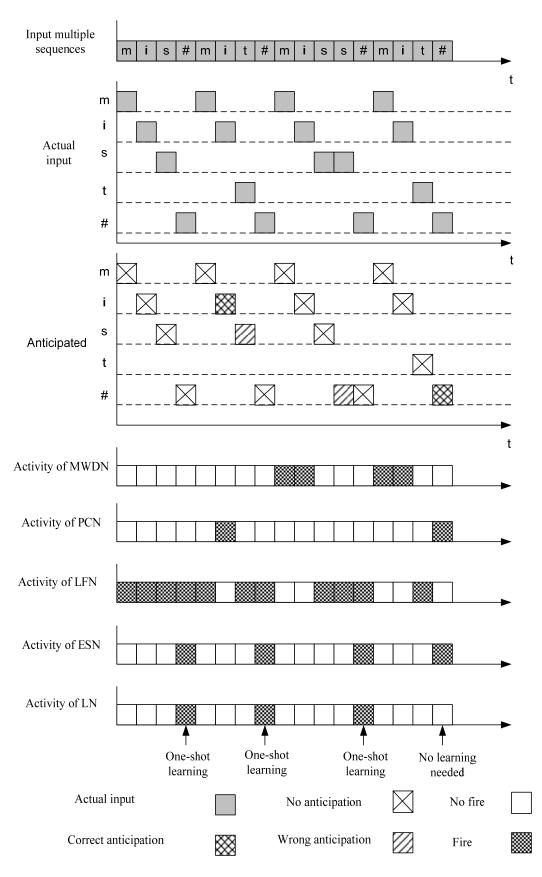

| 4.6 Example of anticipation based sequence learning                               | 81  |

| 4.7 Discussion                                                                    | 86  |

| 4.8 Summary                                                                       | 90  |

| or ton E                                                                          | 02  |

| apter 5                                                                           |     |

| Application Research                                                              |     |

| 5.1 Introduction                                                                  |     |

| 5.2 Self-organizing learning array for power quality classification               |     |

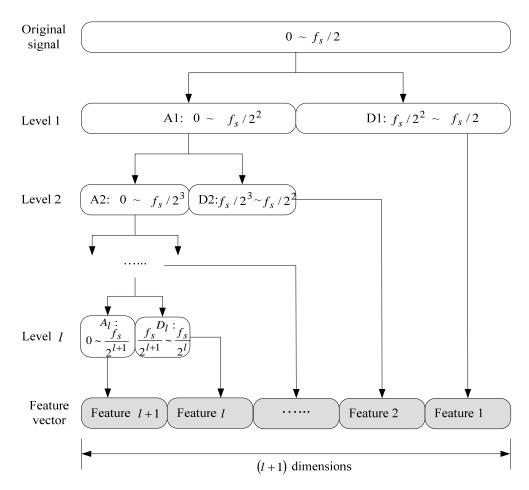

| 5.2.1 Wavelet based feature extraction                                            |     |

| 5.2.2 Simulation and analysis                                                     |     |

| 5.2.2.1 Data generation                                                           |     |

| 5.2.2.2 Simulation results                                                        |     |

| 5.2.2.3 Discussion                                                                |     |

| 5.2.3 Noise analysis                                                              |     |

| 5.3 Self-organizing associative memory for pattern recognition and image recovery |     |

| 5.3.1 Hetero-associative memory: Iris database classification                     |     |

| 5.3.2 Auto-associative memory: image recovery                                     |     |

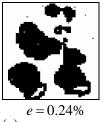

| 5.3.2.1 Panda image recovery                                                      |     |

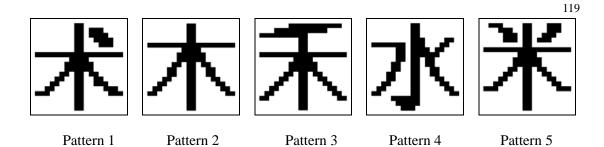

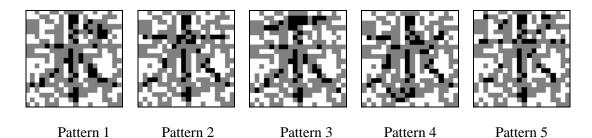

| 5.3.2.2 Chinese character recognition and recovery                                |     |

| 5.3.3 Discussion                                                                  | 120 |

| 5.4 Temporal sequence learning                                                    | 121 |

| 5.5 Summary                                                                       | 124 |

| apter 6                                                                           | 125 |

| Low Power Design and Hardware Architecture                                        |     |

| 6.1 Introduction                                                                  |     |

| 6.2 Low power design                                                              |     |

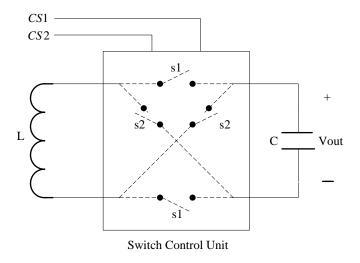

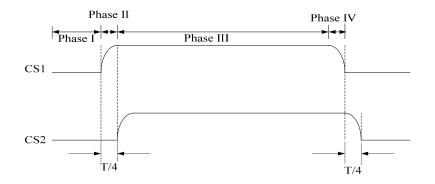

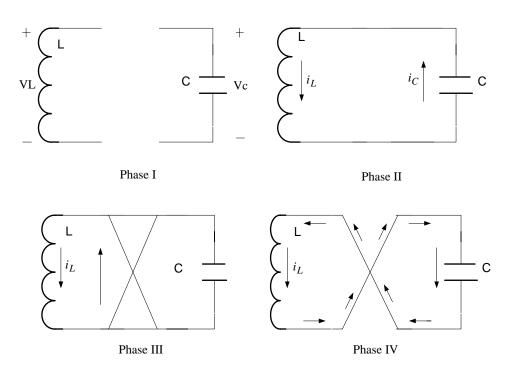

| 6.2.1 Low power switched inductor-capacitor (SLC) architecture                    |     |

| 6.2.2 Simulation results                                                          |     |

| 6.2.2.1 Inverting logic construction                                              | 132 |

| 6.2.2.2 Non-inverting logic                                                       |     |

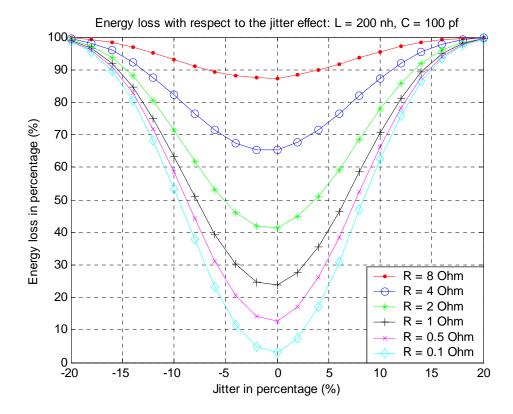

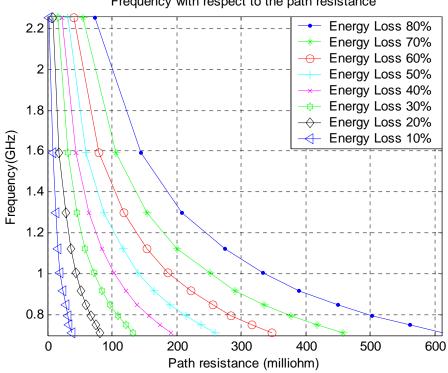

| 6.2.2.3 Energy loss and timing analysis                                           |     |

|                                                            | 9   |

|------------------------------------------------------------|-----|

| 6.2.2.4 Discussion                                         | 140 |

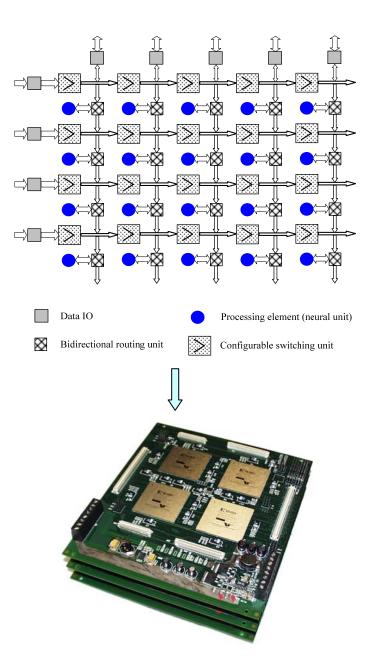

| 6.3 Programmable hardware for intelligent systems          | 142 |

| 6.4 Looking ahead                                          | 144 |

| 6.5 Summary                                                | 147 |

| Chapter 7                                                  |     |

| Conclusions and Future Research                            |     |

| 7.1 Conclusions                                            | 148 |

| 7.2 Original Contributions                                 |     |

| 7.3 Future research                                        | 151 |

| Bibliography                                               | 154 |

| Appendix A: Source Code and Data Sets Used in Dissertation |     |

# List of Tables

Table

•

| Table 3-1 Self-determination of function value F                                    | 45  |

|-------------------------------------------------------------------------------------|-----|

| Table 3-2 Two examples of setting F value                                           | 46  |

| Table 5-1 Power quality distance model [Gal 04]                                     | 96  |

| Table 5-2 Classification results for SOLAR based on wavelet feature extraction      | 100 |

| Table 5-3 Classification results reported in [Gal 04]: Inductive interface approach | 100 |

| Table 5-4 Classification results based on SVM                                       | 101 |

| Table 5-5 Wavelet characteristics                                                   | 104 |

| Table 5-6 Averaged classification results for different wavelets                    | 105 |

| Table 5-7 Performance of different wavelets                                         | 106 |

| Table 5-8 Wavelet family hypothesis test                                            | 107 |

| Table 5-9 Comparison of the classification performance on Iris database             | 115 |

| Table 5-10 Image recovery error information                                         | 117 |

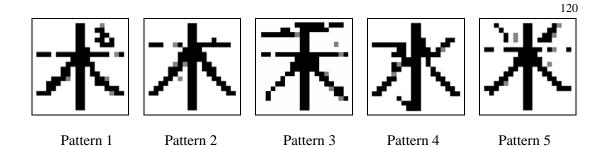

| Table 5-11 Testing error bits and missing bits information                          | 120 |

Page

# List of Figures

11

| Figure 1-1 Dissertation organization                                                         | 28   |

|----------------------------------------------------------------------------------------------|------|

| Figure 2-1 Single curve fitting                                                              | 35   |

| Figure 2-2 Three curve fitting (TCF) scheme                                                  | 36   |

| Figure 2-3 Three curve fitting results                                                       | 37   |

| Figure 2-4 Pipelined value system architecture                                               | 39   |

| Figure 2-5 Detailed structure of data PE                                                     | 41   |

| Figure 3-1 Individual PE interface model                                                     | 44   |

| Figure 3-2 An example of input space distribution                                            | 45   |

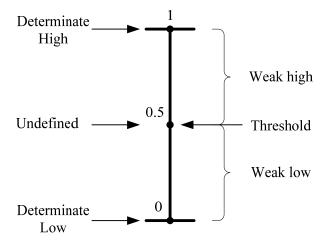

| Figure 3-3 Signal strength and its semi-logic value                                          | 47   |

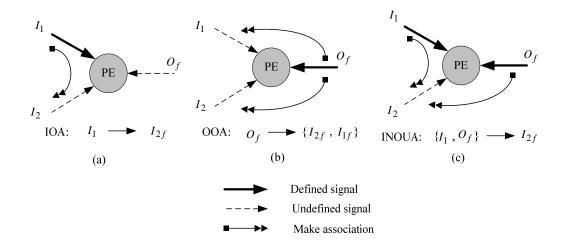

| Figure 3-4 Three types of associations of processing element                                 | 48   |

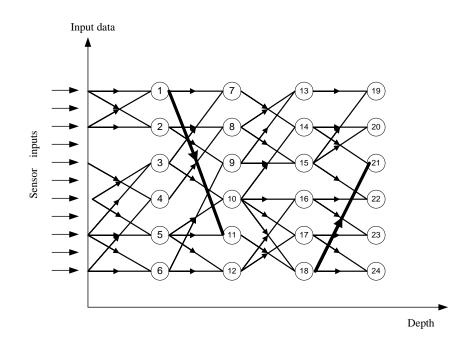

| Figure 3-5 An example of feedforward operation network                                       | 55   |

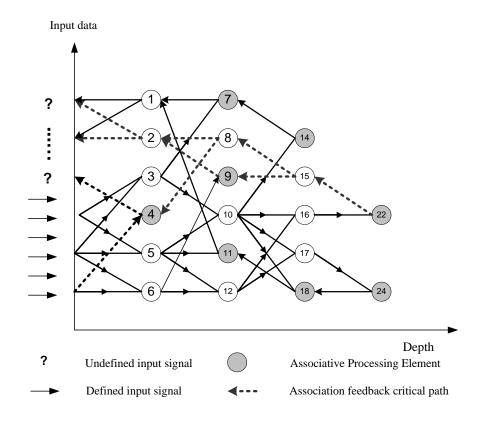

| Figure 3-6 Example of feedback structure in testing stage                                    | 57   |

| Figure 3-7 Associative memory feedback mechanism                                             | 58   |

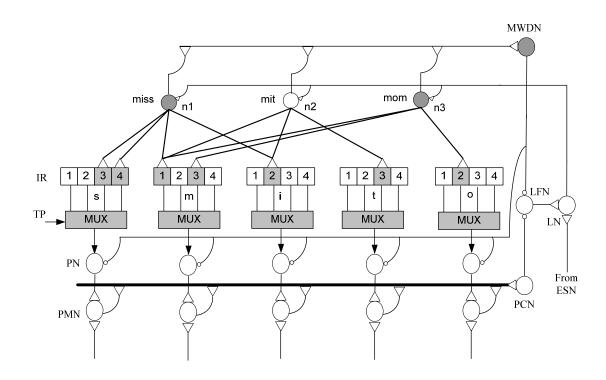

| Figure 4-1 Hierarchical organization of sequences                                            | 63   |

| Figure 4-2 System architecture of anticipation-based hierarchical temporal sequence learning | 64   |

| Figure 4-3 Two-active area neuron firing mechanism                                           | 66   |

| Figure 4-4 Hierarchical structure of the modified Hebbian learning                           | 67   |

| Figure 4-5 Storage of sequence in input register                                             | 70   |

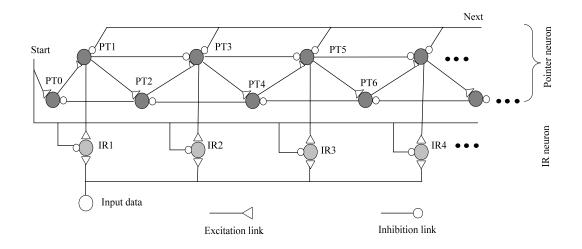

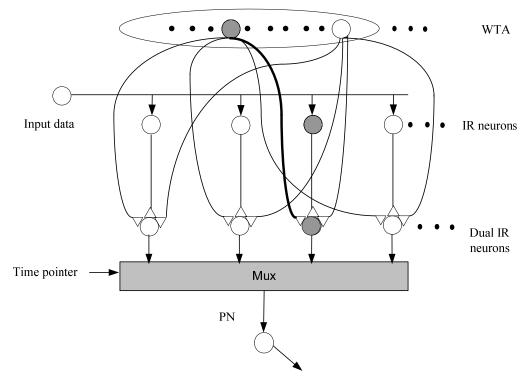

| Figure 4-6 Structure of input register                                                       | 70   |

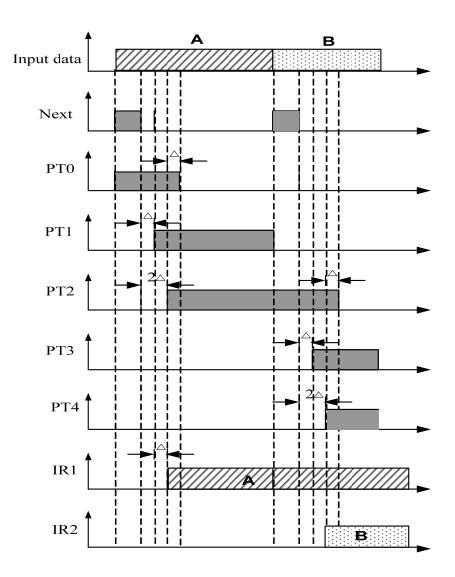

| Figure 4-7 Timing diagram of neurons firing in the IR                                        | 72   |

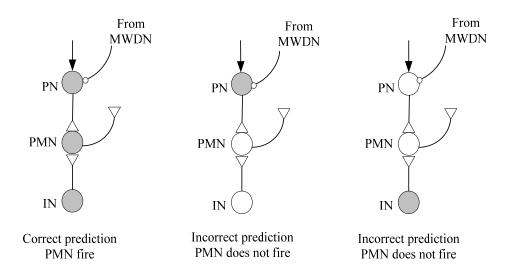

| Figure 4-8 Firing mechanism of PMN                                                           | 75   |

| Figure 4-9 Prediction mechanism                                                              | 75   |

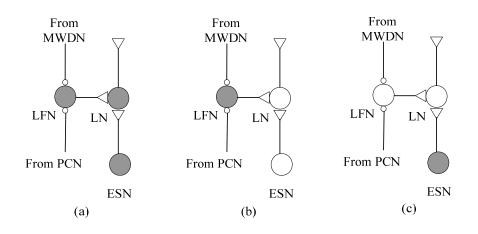

| Figure 4-10 Firing mechanism of learning neuron                                              | 76   |

| Figure 4-11 LTM and multiple winners                                                         | 77   |

| Figure 4-12 Activation of prediction neuron                                                  | 79   |

| Figure 4-13 Time-controlled multiplexer                                                      | 80   |

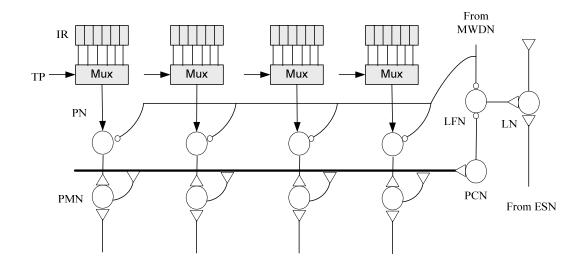

| Figure 4-14 Learning and anticipation of multiple sequences                                  | 83   |

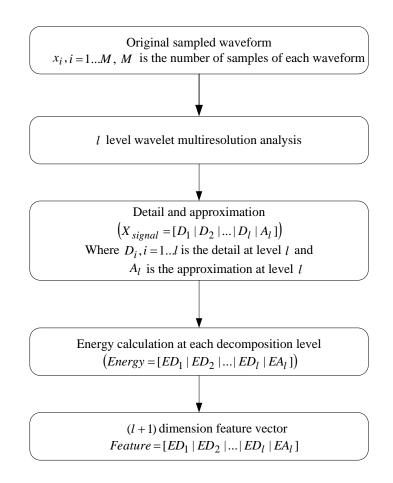

| Figure 5-1 MRA analysis and feature extraction                                               | 94   |

| Figure 5-2 Wavelet based feature extraction                                                  | 95   |

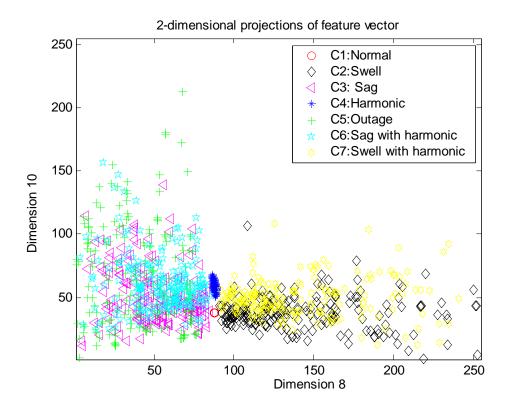

| Figure 5-3 Two dimensional projections of the feature vector: dimensional 8 and 10           | 98   |

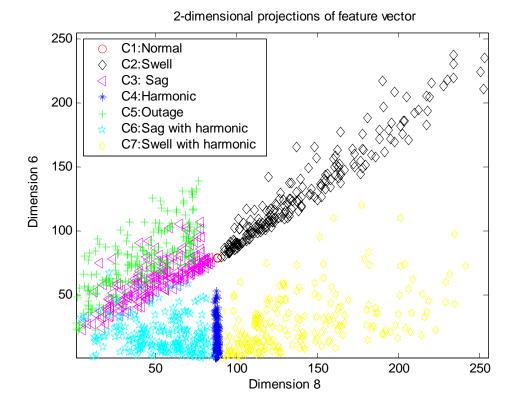

| Figure 5-4 Two dimensional projections of the feature vector: dimensional 8 and 6            | 98   |

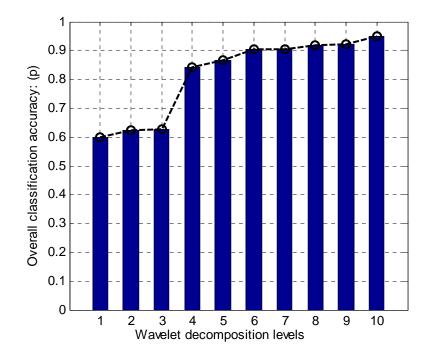

| Figure 5-5 Relationship between the wavelet decomposition levels and classification accuracy | .103 |

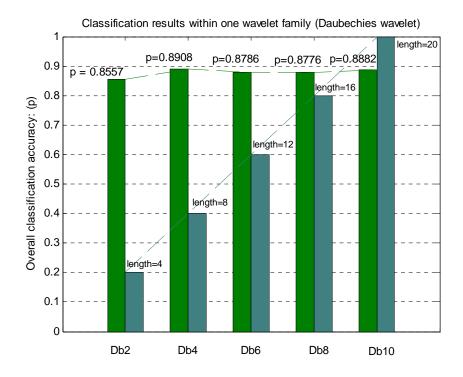

| Figure 5-6 Classification results and their corresponding wavelet filter length              | .108 |

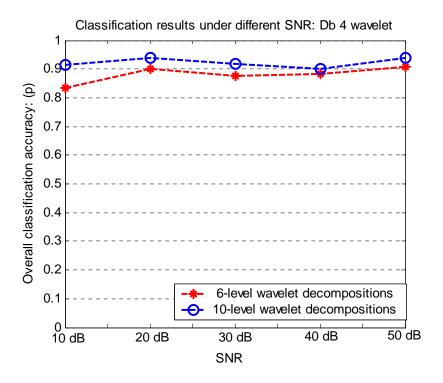

| Figure 5-7 Classification results under different SNR condition                              | .109 |

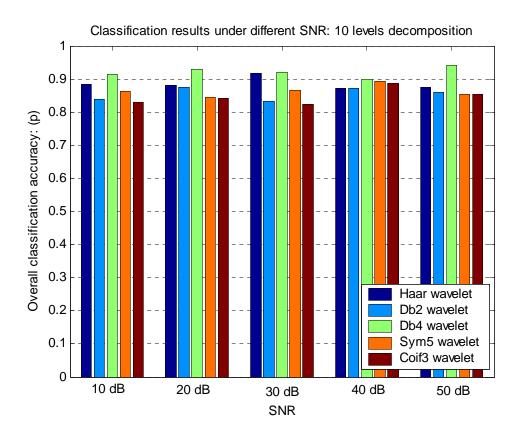

| Figure 5-8 Different wavelet classification results under different SNR conditions           | .110 |

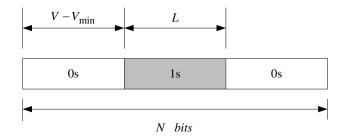

| Figure 5-9 N input bits sliding bar coding mechanism [Sta 06a]                               | .112 |

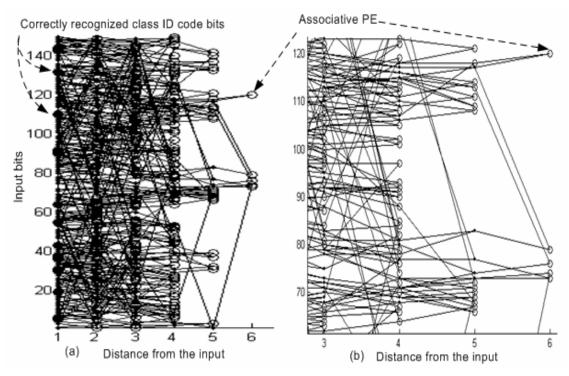

| Figure 5-10 Associative PEs and their inter connection structure                             | .114 |

| Figure 5-11 The 64x64 binary panda image                                                     | .116 |

| Figure 5-12 Testing image (block half) and recovered image                                   | .117 |

| 12                                                                          |  |

|-----------------------------------------------------------------------------|--|

| Figure 5-13 Training patterns: Five black-white Chinese characters          |  |

| Figure 5-14 Testing patterns with 50% pixels (200 pixels) blocked           |  |

| Figure 5-15 Recovered Chinese testing pattern                               |  |

| Figure 5-16 Simulation results for the temporal sequence learning model     |  |

| Figure 5-17 Prediction result based on hint                                 |  |

| Figure 6-1 Proposed SLC architecture for low power design                   |  |

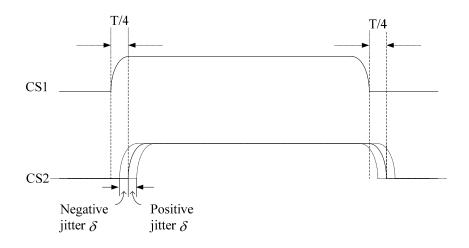

| Figure 6-2 Control signals of CS1 and CS2                                   |  |

| Figure 6-3 Operation phases of the proposed circuit                         |  |

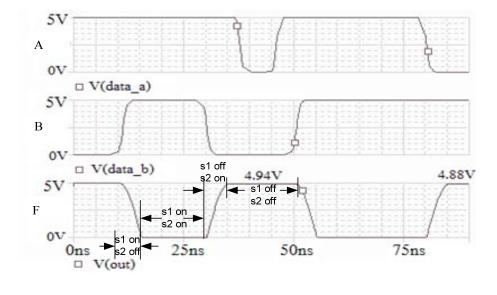

| Figure 6-4 $F = \overline{A \bullet B}$ output waveform                     |  |

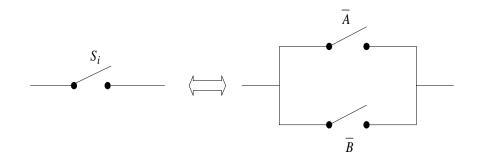

| Figure 6-5 Switch $S_i$ replaced by path of complementary switches          |  |

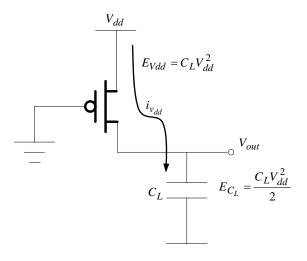

| Figure 6-6 Equivalent circuit in the charging load capacitor phase [Rab 03] |  |

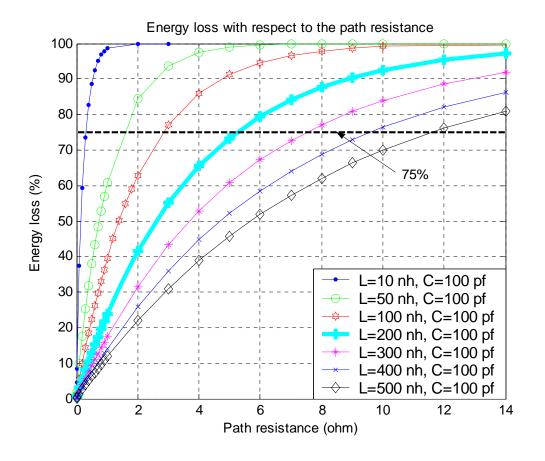

| Figure 6-7 Energy loss with respect to the path resistance                  |  |

| Figure 6-8 Control signal jitter effect                                     |  |

| Figure 6-9 Energy loss with respect to jitter effect                        |  |

| Figure 6-10 Frequency relationship with the path resistance                 |  |

| Figure 6-11 System level hardware architecture [Sta 03a] & [Sol 06]144      |  |

# List of Abbreviations

| AA:    | Auto-Associative                        |

|--------|-----------------------------------------|

| AI:    | Artificial Intelligence                 |

| BAM:   | Bidirectional Associative Memories      |

| BDNN:  | Bayesian Decision-based Neural Network  |

| BRU:   | Bidirectional Routing Unit              |

| CMOS:  | Complementary Metal Oxide Semiconductor |

| CNN:   | Cellular Neural Networks                |

| CSU:   | Configurable Switching Unit             |

| DNN:   | Dual-weight Neural Network              |

| DPN:   | Data Processing Network                 |

| DV:    | Differential Voting                     |

| FPGA:  | Field-Programmable Gate Array           |

| HA:    | Hetero-Associative                      |

| HANN:  | Hetero-Associative Neural Networks      |

| HSLM:  | Hierarchical Sequence Learning Machine  |

| IC:    | Integrated Circuit                      |

| INOUA: | Input–Output Association                |

| IOA:   | Input Only Association                  |

| IPN:   | Information Processing Network          |

| IR:    | Input Register                          |

| LFN:   | Learning Flag Neuron                    |

| LN:    | Learning Neuron                         |

| LSE:   | Least Square Error                      |

| LTM:   | Long Term Memories                      |

| MANN:  | Multi-Associative Neural Network        |

| MRA:   | Multiresolution Analysis                |

| MUX:   | Multiplexer                             |

|        |                                         |

| MWDN:  | Multiple Winner Detection Neuron   |

|--------|------------------------------------|

| OOA:   | Output Only Association            |

| PCN:   | Prediction Checking Neuron         |

| PE:    | Processing Elements                |

| PMN:   | Prediction Matching Neuron         |

| PN:    | Prediction Neuron                  |

| P-NET: | Projective Networks                |

| PQ:    | Power Quality                      |

| RAM:   | Random Access Memory               |

| RBF:   | Radial Basis Function              |

| RL:    | Reinforcement Learning             |

| SCU:   | Switch Control Unit                |

| SLC:   | Switched Inductor-Capacitor        |

| SNR:   | Signal to Noise Ration             |

| SOAM:  | Self-Organizing Associative Memory |

| SOLAR: | Self-Organizing Learning Array     |

| SOM:   | Self-Organizing Map                |

| SS:    | Signal Strength                    |

| STM:   | Short-Term Memory                  |

| SVM:   | Support Vector Machine             |

| SWTA:  | Stiff Winner Take All              |

| TCF:   | Three Curve Fitting                |

| TP:    | Time Pointer                       |

| VLSI:  | Very Large Scale Integration       |

| WTA:   | Winner Take All                    |

## **Chapter 1**

# Introduction

#### **1.1 Motivation**

With the development of deep submicron very large scale integration (VLSI) systems, nanotechnology and bioinformatics, it is possible to build complex dynamically self-reconfigurable systems for machine intelligence. However, there is still no clear picture about how to design the truly brain-like intelligent machines. The biggest challenge comes from how to develop the system level models and architectures that are able to learn, process information, make associations and predictions to accomplish desired tasks, which are the critical elements for any biological intelligent systems.

Traditional structures for artificial intelligence, for instance, neural networks, were introduced with the hope to model functions of the human brain. However, very little progress was made towards implementation of structures and distributed learning algorithms, which would yield essential features of neural processing observable in a living brain. People agreed that human brains and computers use fundamentally different ways in handling various problems [Haw 04]. That is why a three-year old baby can easily watch, listen, learn, and remember various external environment information and adjust her behavior, while the most sophisticated computer can not. In such sense, modern computers are just computational machines without intelligence. The question is: how does one develop the system level models and architectures that are able to mimic the brain intelligence?

Recently, a new theoretical framework titled "memory-prediction" was proposed for designing real intelligent machines by J. Hawkins [Haw 04]. This theoretical framework provides a new solution for how to understand the memory and prediction, which are widely considered to be critical elements of human intelligence. In this dissertation, "learning" is added to this framework to present a complete picture for designing brain-like machine intelligence. While [Haw04] focused on understanding the intelligent framework based on the neocortex, the "learning-memory-prediction" framework proposed in this dissertation research is focused on developing system level models and architectures for dynamically self-reconfigurable systems that are able to mimic the brain-intelligence. The major advantage of such systems over the traditional hardware with embedded software systems is that they can dynamically self-reconfigure their structures in interaction with the external environment to learn, remember and predict information, therefore guiding the machine to achieve its goals. These kinds of systems have wide applications including dynamically adaptive control, intelligent robotics, automatic target recognition and tracking, image and signal processing, biological research, data mining, and decision-support systems.

Another motivation for designing brain-like intelligent systems comes from the development of the reconfigurable computing and VLSI technologies. With the capability of fabricating millions of transistors in a tiny silicon area, it is technologically possible for engineers to implement an integrated "silicon brain". Therefore, it is critical to integrate knowledge from neuroscience, bioinformatics and engineering design to develop a truly intelligent machine. To this end, we need to develop the system level models and

architectures that not only can learn, remember and anticipate, but are also hardware oriented, fault tolerant and scalable to large systems.

#### 1.2 Related work: learning, memory and prediction

As one of the most sophisticated, challenging, rewarding and significant interdisciplinary research areas, designing of intelligent systems has attracted extensive attention both in science and engineering. In this section, I will give a brief review of the state-of-the-art research achievements for understanding, modeling and designing of intelligent systems in learning, memory and prediction.

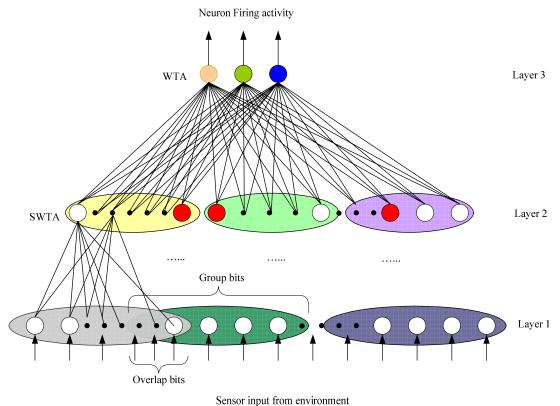

The ability of self-organization is critical for intelligent systems to learn and process information from the external environment. A self-organizing learning array (SOLAR) system was proposed by J. A. Starzyk [Sta 05a]. As a parallel learning architecture, SOLAR provides a general learning mechanism with sparsely, adaptive interconnections, data-driven learning, and multilayer structures. Neurons in SOLAR exchange information during learning, and have the ability to self-organize by adapting their functionality and interconnection weights in response to the information received.

The SOLAR structure proposed in [Sta 05a] is a supervised learning mechanism and shows solid performance for classification problems. However, the intelligent systems should also be able to learn without supervision, which means that there is no instructor telling the machine what it should or should not do. The intelligent machine should learn through its experience interacting with the external environment in order to maximize the reward for its actions and thus achieve its goal. Reinforcement learning (RL) is this type of un-supervised learning that learns by optimizing the expected reward it receives when interacting with the environment [Sut 98]. Value system is an important element for the RL. The machine should have an internal biologically plausible organization that streamlines reward and punishment signals from environment to build its internal value system, is able to evaluate signals coming from environment according to its value system, and plans its actions to optimize the expected rewards. Although it is very important to estimate the value signal accurately and dynamically, it is very difficult to do so in complex, uncertain environment for the following reasons:

- Limited availability of information;

- Time variation of the information included in data;

- High information redundancy;

- High dimensionality of the data set;

Many results for using value systems in reinforcement learning have been reported in recent literature. For instance, [Bab 03] proposed a fuzzy-based navigation system for two mobile robots using distributed value function reinforcement learning. This approach enables the robots to learn a value function, which estimates the future rewards for both robots. In this way, cooperation between the two robots is maintained and each robot learns to execute the actions that are good for both of them. In [Hua 02b], a robotic value system was proposed by integrating novelty and reinforcement learning. This system includes sensory inputs, a cognitive mapping module, a value system, and an action network. In this dissertation research, a value system for machine learning is investigated. The proposed value system is

an online dynamic network, which can dynamically estimate the value of multidimensional data set.

The SOLAR structure implemented in [Sta 05a] utilizes a feedforward mechanism for the machine to learn the information from environment. This concept is further advanced in this dissertation research to include both feedforward and feedback mechanisms in hierarchical organization to learn and memorize information: self-organizing associative memory (SOAM). This introduced the second element of the proposed framework: associative memory.

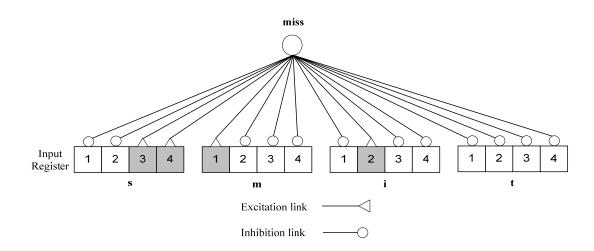

Associative memory is of critical importance for human intelligence. There are two types of associative memories: hetero-associative (HA) and auto-associative (AA) memory. HA memory makes associations between paired patterns, such as words and pictures, while AA memory associates a pattern with itself, recalling stored patterns from fractional parts of the pattern as in image recovery. Due to the importance of the associative memory for machine intelligence, such systems have been extensively studied. Among HA studies, Salih et al. proposed a new approach for bidirectional associative memories (BAM) using feedback neural networks [Sal 00]. The perceptron training algorithm was used to solve a set of linear inequalities for the BAM neural network design. In [Cha 03], Chang et al. proposed adaptive local training rules for second-order asymmetric bidirectional associative memory. In [Wan 99], Wang presented a multi-associative neural network (MANN) and showed its application to learning and retrieving complex spatio-temporal sequences. Simulation results show that this system is characterized by fast and accurate learning, and has the ability to store and retrieve a large number of complex sequences of spatial patterns. Hopfield's paper [Hop 82] is a classic reference among AA studies. Since that paper, many research results have been reported. Vogel presented an algorithm for auto-associative memory in sparsely connected networks [Vog 98]. The resulting networks have large information storage capacities relative to the number of synapses per neuron. Vogel et al. derived a lower bound on the storage capacities of two-layer projective networks (P-nets) with binary Hebbian synapses [Vog 97]. It is reported that given a 1% tolerance for activation of spurious neurons, the P-net with 1000 synapses per neuron may store more than  $1.5 \times 10^6$  training vectors with 20 active neurons per vector. In [Wu 00], an efficient learning algorithm for feedforward associative memory is proposed. This memory uses a winner take all (WTA) mechanism and involves a two-layer feedforward neural network. Recently, Wang et al. proposed an enhanced fuzzy morphological auto-associative memory based on the empirical kernel map [Wan 05].

It is believed that the human brain employs both hetero-associative and auto-associative memory for learning, action planning, and anticipation [Riz 01] [Bro 95] [Mur 97]. The memory formed in the human brain is self-organized and data driven. Self-organization is responsible for formation of hierarchically organized interconnected structures not only in the human brain but also in the nervous systems of lower vertebrates [Mal 03]. In this research, a self-organizing associative memory capable of both hetero-associative and auto-associative learning is designed and analyzed. The SOAM is a hierarchically organized associative memory, with sparse and local connections, self-organizing processing elements (PE), and probabilistic synaptic transmissions. Initially, all PEs in the network are identical and record their input data distribution using probability estimators. Using associations observed in the input data, the network self-organizes defining transfer functions of its PEs. Both feedforward and feedback mechanisms are used to transform signals and make associations.

After the information is stored in the memory, the prediction mechanism is introduced for the intelligent systems to be able to learn and predict temporal sequences. Temporal sequence learning is presumably among the most important components of human intelligence, as most human intelligence behaviors are in the sequential format. For instance, the natural language processing, speech recognition, reasoning and planning are all based on sequential memory. Over the past decade, models and mechanisms for temporal sequence learning have attracted considerable attention. R. Sun and C. L. Giles offer a useful review of the characteristics, problems, and challenges for sequence learning from recognition and prediction to sequential decision making [Sun 01].

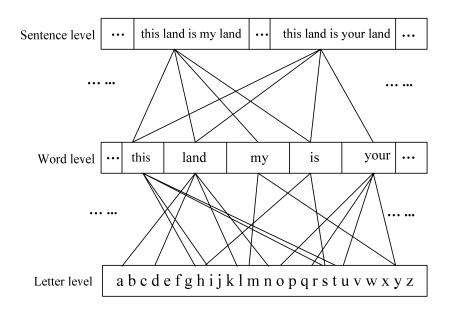

D. Wang and M. A. Arbib proposed a complex temporal sequence learning model based on short-term memory (STM) [Wan 90a]. In their paper, two special types of neurons are proposed for complex temporal sequence learning. The first one is the dual neuron, which is used to store a signal for a short period of time. Unlike the traditional binary signal values used in many neural network models, the output of a dual neuron is a graded signal. The second neuron is the sequence detecting neuron. After learning, this sequence detecting neuron fires in response to the previous sequence of patterns, not just the previous pattern. It thereby overcomes a limitation of networks that cannot reliably recall sequences that share common patterns. The same authors presented a framework of learning, recognition and reproduction of complex temporal sequences in [Wan 93]. In this model, sequences are acquired by the attention learning rule, which combines Hebbian learning and a normalization rule with sequential system activation. Time intervals between sequence components do not affect recognition. A global inhibitor is proposed to enable the model to learn context lengths required to disambiguate associations in complex sequence reproduction. In order to overcome the capacity limitation of STM, a hierarchical sequence recognition model based on the chunking notion is proposed in [Wan 93]. For instance, in a letter-word-sentence hierarchical structure, a unit for a given word is activated at the end of the presentation of that word, and the model learns the sequence of letters of that word based on the letter units active at that time. Once the word structure has been learned, the same mechanism can be applied to train a higher hierarchical level on the sequence of words. One more issue addressed in [Wan 93] is interval maintenance. This is achieved by coding intervals by connection weights from the detector layer to the input layer.

In [Wan 95], a neural network model capable of learning and generating complex temporal patterns by self-organization was proposed. This model actively regenerates the next component in a sequence and compares the anticipated component with the next input. A mismatch between what the model anticipates and the actual input triggers one-shot learning. Although the anticipation mechanism improves the learning efficiency of this model, it needs several training sweeps to learn a sequence. As the number of training sweeps required depends on the degree of complexity of the sequences, it is not very efficient for highly complex sequences.

Another paper [Wan 96] focused on the learning of the multiple temporal sequences and "catastrophic interference." It is showed that the anticipation model proposed in [Wan 95] is capable of incremental learning with retroactive interference but without catastrophic interference. In addition, a chunking mechanism was included in this model to detect repeated subsequences between and within sequences, thereby substantially reducing the amount of retraining in sequential training.

L. Wang proposed the use of associative memory to learn and retrieve spatio-temporal sequences in [Wan 98] and [Wan 99]. In [Wan 98], the associative memory model includes three major components: a voting network, a parallel array of hetero-associative neural networks (HANN), and delayed feedback lines from the output of the system to the associative neural network layers. The delayed sequence of hetero-associators "votes" on the next output at each time step. After learning, the system can retrieve the entire sequence from a small cue sequence. Since the model in [Wan 98] assumes that each HANN only learns hetero-associations between single spatial patterns and does not learn to associate multiple patterns in groups, this model was further extended to include associations of one pattern with multiple patterns in [Wan 99]. The proposed model in [Wan 99] has the advantages of short learning time and accurate retrievals, and the ability to store a large number of complex sequences. However, in both of the models the required number of networks (HANNs in [Wan 98] and MANNs in [Wan 99]) for learning and retrieving a sequence significantly increases with the complexity of the sequence.

In [Wan 01], a dual-weight neural network (DNN) scheme for fast learning, recognition, and reproduction of temporal sequences was developed. In a DNN, each neuron is linked to other neurons by long-term excitatory weights and short-term inhibitory weights. Fast learning is achieved by employing a two-pass training rule to encode the temporal distance between two arbitrary pattern occurrences. Based on this, the DNN was extended to a more generalized model, DNN2, which incorporates a self-organizing algorithm. In this way, the DNN2 can achieve autonomous temporal sequence recognition and reproduction.

A hierarchical structure is important for sequence learning. For instance, in [Man 97], a linear-time algorithm called SEQUITUR was proposed for identifying hierarchical structure in sequences. The main idea of this algorithm is that phrases which appear more than once can be replaced by a grammatical rule that generates the phrase, and that this process can be continued recursively, producing a hierarchical representation of the original sequences. Although [Man 97] is not focused on sequence retrieval, it presents the idea of hierarchical representation of sequences, which is used in many research efforts that model sequence learning. For instance, D. George and J. Hawkins [Geo] discussed the problem of hierarchical structure for temporal sequence learning targets on invariant pattern recognition. It is concluded in [Geo] that the neocortex solves the invariance problem in a hierarchical structure. Each region in the hierarchy learns and recalls sequences of inputs, and temporal sequences at each level of the hierarchy become the spatial inputs to the next higher regions.

In this dissertation research, an anticipation based sequence learning neural structure is proposed. Hierarchical organization, prediction mechanism, and one-shot learning characterize this model. In the lowest level of the hierarchy, a modified Hebbian learning mechanism is used for pattern recognition. Prediction is an essential element of this temporal sequence learning model. By correct prediction, the machine indicates that it knows the current sequence and does not require additional learning. When the prediction is incorrect, one-shot learning is executed and the machine learns the new input sequence as soon as the sequence is completed.

#### **1.3 Significance of Research**

Significance of the research presented in this dissertation stems from the following needs and observations:

- It is important to understand how a brain-like complex system can be self-organized to develop its connectivity structure, build the mechanisms for association and anticipation, interact with external environment, accumulate knowledge through experience, formulate goals for its actions, and self-control to achieve its goals. To this end, the proposed "learning-memory-prediction" framework provides a foundation for designing the intelligent systems with such capabilities;

- It is critical to design system level models and architectures that are able to mimic such intelligent mechanisms. The proposed dynamic value learning system, self-organizing associative memory, and anticipation based sequence learning network provide a solution for designing necessary elements of such brain-like intelligent systems. In the proposed systems, the complexity of the network organization is self-decided by the system according to the information it receives, rather than by the arbitrary choice of a designer; as is the case of artificial neural networks. These characteristics make the proposed models in this research more like a "living-brain"; it can grow in complexity and ability to model external environment according to the information it receives, and it can accumulate such

knowledge. This is a fundamental difference in comparison to the fixed or pre-defined neural network structure;

• It is essential to develop new computing paradigm that can achieve extremely low power consumption for hardware implementation of such large scale integrated intelligent systems. Without careful consideration of the low power consumption, the designed intelligent system will not be able to function properly. Therefore, the proposed low power design scheme in this dissertation provides a possible solution for the future implementation of such large scale high density intelligent systems;

#### 1.4 Research goals and objectives

As most of the state-of-the-art research in the effort of designing intelligent systems is focused on individual elements for learning, memory, and prediction, it is the goal of this dissertation research to develop mechanisms and organization for elements of intelligence and to provide a framework to integrate these individual elements together with the aim of designing brain-like intelligent systems.

To accomplish this research goal, I will focus on the designing of system level models and architectures for building dynamically self-reconfigurable systems for machine intelligence. The underlying foundation of building such brain-like intelligent systems is based on the proposed "learning-memory-prediction" framework. It is the objective of this research to justify such an integrated theoretical framework for designing real intelligent systems, and under this foundation, to develop the network models and architectures that:

- Are able to self-organize their connectivity structure and dynamically reconfigure to learn, process information, accumulate knowledge, and make associations and predictions;

- Are able to learn without a supervisor, learn through interaction with environment without software rules or a global learning algorithm, and learn through experiences to accomplish desired tasks;

- Are scaleable to very large systems, and are fault tolerant and modular for easy implementation in hardware, such as reconfigurable computing field-programmable gate array (FPGA) technology, dedicated analog or digital VLSI technology, or future system level technology (modular blocks represented by SOLAR systems or nanotechnology).

## **1.5 Dissertation Organization**

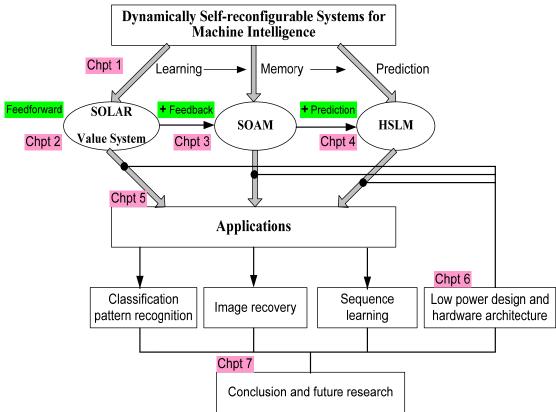

Figure 1-1 illustrates the overall organization of this dissertation.

Figure 1-1 Dissertation organization

Chapter 1 presents the motivations, significance, and objective of this research. This chapter also provides a brief review of the state-of-the-art work in the area of learning, memory, and prediction. In addition, this chapter provides an overview and organization of the whole dissertation.

Chapter 2 focuses on the learning scheme. A brief review of the SOLAR and reinforcement learning is given in this chapter. It introduces one of the critical elements in the learning procedure: value learning system. A novel architecture of the dual-network online value system is proposed in this chapter, and this system can dynamically estimate the value of incoming multidimensional data sets from external environment. In the SOLAR learning system, information is only propagated forward, and this is not sufficient for the intelligent systems to select, evaluate, and memorize useful information. Therefore, a feedback mechanism is introduced in the self-organizing network and this leads to the organization of SOAM in Chapter 3.

Chapter 3 discusses in detail the proposed self-organizing associative memory architecture, which is a hierarchically organized memory network with sparse and local interconnections. Both feedforward and feedback mechanisms are used to transform signals and make associations. This associative memory provides a mechanism for the intelligent system to be able to associatively recover a complete picture from partial information (auto-association), or associate one piece of information with another one (hetero-association). After the information is stored in the memory structure, the intelligent systems should be able to make predictions to learn and retrieve temporal sequences. This leads to the hierarchical sequence learning machine (HSLM) introduced in Chapter 4.

Chapter 4 focuses on the system level architecture of the proposed temporal sequence learning neural network. This network is hierarchically organized and is efficient in both learning effort and storage capacity. At each hierarchical level, a winner-take-all structure is used to select the firing neurons at this level, and the firing neurons in one level provide the input to the neurons on the next hierarchical level. A prediction mechanism is proposed in this model for efficient anticipation based learning. As long as all predictions are correct, no learning takes place. Otherwise, a learning signal is issued at the end of a sequence and a one-shot learning is executed to learn the new sequence.

Chapter 5 discusses different application problems for the proposed dynamically self-reconfigurable systems. The application areas studied in this dissertation include pattern

recognition and classification, image recovery, and temporal sequence learning. Through these application problems, it is clearly shown that the proposed models have the abilities to learn, process information, and make associations and predictions to solve practical problems.

Chapter 6 discusses the low power design of the large scale, high density intelligent systems. Power consumption will be a major design issue for such complex dynamically reconfigurable systems. In this chapter, a novel switched inductor-capacitor (SLC) architecture is proposed to reduce the dynamic power consumption. Finally, a brief description of the hardware architecture based on the reconfigurable FPGA technology is presented in this chapter. This FPGA system will provide a platform for prototyping and testing of the proposed models and architectures in this dissertation.

Chapter 7 summarizes the whole dissertation work, restates the novelty and original contributions of this dissertation work, and discusses future research directions.

# **Chapter 2**

# Value System for Machine Learning

#### **2.1 Introduction**

A new machine learning concept, the self-organizing learning array was recently proposed in [Sta 05a]. As a general learning mechanism, SOLAR has several fundamental advantages over the traditional neural network based learning scheme, including online data-driven learning, local and sparse interconnection, and entropy based learning. While the learning in Kohonen's self-organizing map (SOM) [Koh 95] is performed in the entire input data space, individual neurons in SOLAR learn information from their local input space. In addition, the interconnect structure in SOLAR can be dynamically reconfigured according to the information each neuron receives in the learning process. This provides SOLAR with more flexibility in the learning process compared to the fixed interconnection structure (defined by templates) in cellular neural networks (CNN) [Man 99].

The SOLAR architecture presented in [Sta 05a] uses supervised learning, which means a teacher (instructor) is needed to tell the machine what is good and what is bad. However, a supervisor is not always available in many learning environments [Sut 98]. For instance, when a one-year old baby stands alone in a baby-cart and plays with toys, turns around and looks at the fantasy world around him, there is no explicit teacher telling him about the information he is observing, processing and perceiving. However, learning does occur in this process. By the interaction with the external environment, the baby can process information it receives, adjust its behavior and learn how to achieve his goals [Haw 04]. This kind of learning is a combination of reinforcement learning [Sut 98], anticipation, and novelty detection.

Learning from active interaction with the external uncertain environment is the foundation of reinforcement learning [Sut 98], which is also believed to be the foundation of learning for most of the biologically intelligent systems. People learn through interacting with the external environment, accumulate knowledge through experiences, and adjust behavior (action) to achieve their goals (maximize the rewards signal). A typical reinforcement learning system includes the external environment, a policy, a reward function, and a value function. Among all these elements, R. S. Sutton presented that value function is of critical importance and almost all reinforcement learning algorithms are based on estimating the state-action values [Sut 98]. Based on the information an intelligent system receives from the environment, it should be able to evaluate the signals according to the value system, and adjust its actions to maximize its rewards.

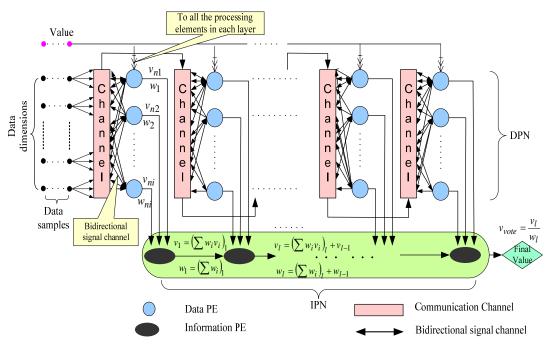

Although it is very important to estimate the value signal accurately and dynamically, it is very difficult to do so in practical applications. In this chapter, an online value system is proposed to dynamically evaluate the value signal for multi-dimensional data sets. Dynamic curve fitting is the core module for this value learning system. Based on this scheme, a three curve fitting (TCF) method is proposed to improve the fit to a statistically distributed high dimensional data set. The proposed value system model has a pipelined architecture and uses two networks: a data processing network (DPN) and an information processing network (IPN).

### 2.2 Online dynamic curve fitting

Consider dynamic adjustment of the fit function described by a linear combination of the selected base functions  $\varphi_i$ , i = 1, 2, ..., q, where q is the number of base functions. The objective of the fit function is to fit values from the received data samples. Assume that each processing element will dynamically adjust its fit function to minimize the least square error (LSE) of the function approximating values of all training data x and y as follows:

$$Y = a_1 * \varphi_1 + a_2 * \varphi_2 + \dots + a_q * \varphi_q \tag{2.1}$$

where  $\varphi_i$ , i = 1, 2, ..., q, is the base function. The number of base functions can be adjusted according to the accuracy required and the data noise level.

Using the least square solution, the coefficients  $a_1, a_2, ..., a_q$  can be determined by pseudo inversion. To do this dynamically, it is necessary to accumulate function values and their combinations for different input samples. Equation (2.1) can be represented as follows:

$$Y = \begin{bmatrix} \varphi_1 & \varphi_2 & \dots & \varphi_q \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \\ \dots \\ a_q \end{bmatrix} = \Phi * A$$

(2.2)

then the coefficients of the approximating function are obtained from

$$\begin{bmatrix} a_{1} \\ a_{2} \\ \dots \\ a_{q} \end{bmatrix} = (\Phi^{T} \Phi)^{-1} \Phi^{T} Y$$

$$= \begin{bmatrix} \sum_{i=1}^{n} \Phi_{1i} \Phi_{1i} & \sum_{i=1}^{n} \Phi_{1i} \Phi_{2i} & \dots & \sum_{i=1}^{n} \Phi_{1i} \Phi_{qi} \\ \sum_{i=1}^{n} \Phi_{1i} \Phi_{2i} & \sum_{i=1}^{n} \Phi_{2i} \Phi_{2i} & \dots & \sum_{i=1}^{n} \Phi_{2i} \Phi_{qi} \\ \dots & \dots & \dots & \dots & \dots \\ \sum_{i=1}^{n} \Phi_{1i} \Phi_{qi} & \sum_{i=1}^{n} \Phi_{2i} \Phi_{qi} & \dots & \sum_{i=1}^{n} \Phi_{qi} \Phi_{qi} \end{bmatrix}^{-1} \left\{ \begin{bmatrix} \sum_{i=1}^{n} \Phi_{1i} Y_{i} \\ \sum_{i=1}^{n} \Phi_{2i} Y_{i} \\ \dots \\ \sum_{i=1}^{n} \Phi_{1i} \Phi_{qi} & \sum_{i=1}^{n} \Phi_{2i} \Phi_{qi} & \dots & \sum_{i=1}^{n} \Phi_{qi} \Phi_{qi} \end{bmatrix}^{-1} \left\{ \begin{bmatrix} \sum_{i=1}^{n} \Phi_{1i} Y_{i} \\ \sum_{i=1}^{n} \Phi_{2i} Y_{i} \\ \dots \\ \sum_{i=1}^{n} \Phi_{qi} Y_{i} \end{bmatrix} \right\}$$

(2.3)

where *n* is the number of data points. For online implementation, this requires storage of  $s = \frac{q(q+1)}{2} + q$ values of different combinations in equation (2.3)  $\left[\sum_{n=1}^{n} q_{n} - q_{n}\right]$

$$\begin{cases} \sum_{i=1}^{n} \Phi_{ki} \Phi_{mi} \\ & \text{where } k, m = 1, \dots, q \\ \sum_{i=1}^{n} \Phi_{ki} Y_{i} \end{cases}$$

(2.4)

As new samples arrive, these *s* values are updated, and equation (2.3) is solved for new coefficients  $a_1, a_2, ..., a_q$ . In general, for *q* base functions one may need to store *s* combinations and invert  $q \times q$  matrix ( $\Phi^T \Phi$ ) to update coefficients of the approximating equation.

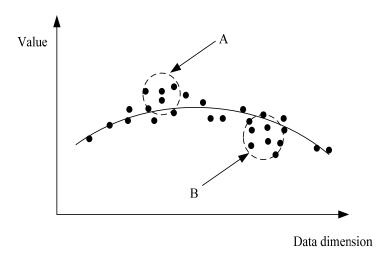

## 2.3 Three curve fitting and voting scheme

Further investigation of the above online curve fitting scheme shows its limitations. This is illustrated in Figure 2-1, which gives a general idea of a single curve fit to noisy data by individual PE. For noisy data values, the single curve fitting technique can not reflect the statistical distribution of the data values in areas A and B, which will cause poor value fitting in these areas. One can compute a standard deviation of the approximated data from the curve fit, but this only gives a uniform measure of statistical errors that does not reflect the different quality of approximation in different regions of the input space.

Figure 2-1 Single curve fitting

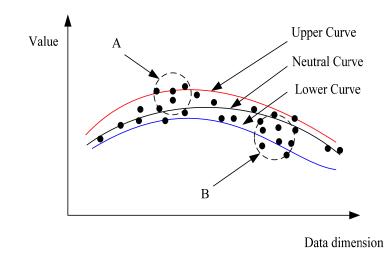

In order to overcome this limitation, a three curve fitting and differential voting (DV)

scheme are proposed. Figure 2-2 shows the concept of the TCF scheme.

Figure 2-2 Three curve fitting (TCF) scheme

For the same data distribution as in Figure 2-1, there are three curves fitting to these data samples values in the following way:

*Neutral Curve*: it fits to all the data samples in the input space, and is the same as the curve in Figure 2-1.

*Upper Curve*: it only fits to the data points which are above the neutral curve.

Lower Curve: it only fits to the data points which are below the neutral curve.

As we can see from Figure 2-2, the neutral curve can provide a rough estimation of the fitted value, and the upper and lower curves can provide its statistical distribution information. Therefore, these upper and lower curves characterize a statistical deviation of the approximated data from the least square fit value. Next, it will be shown how to use this information to get the final estimated value by the differential voting.

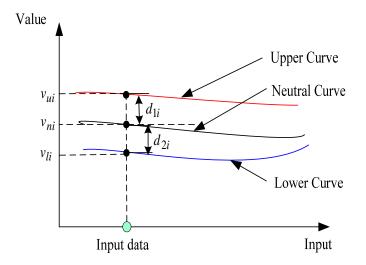

Assume that there are total k processing elements in the network. During training, based on the incoming data samples, each processing element will update its own coefficients of the three curves. During testing, when one testing sample is input to the network, each

processing element will provide the estimated value for this sample based on the three fitting curves built during the training stage. Figure 2-3 shows the results of PE *i* when the incoming samples are fitted, where  $v_{ui}$  is the value estimated by the upper curve,  $v_{ni}$  is the value estimated by the neutral curve, and  $v_{li}$  is the value estimated by the lower curve. In order to reflect the statistical distribution characteristics of the data points, the standard deviation of the estimated value is defined in the following way.

$$d_{1i} = |v_{ni} - v_{ui}|$$

$$d_{2i} = |v_{ni} - v_{li}|$$

$$d_{i} = \frac{d_{1i} + d_{2i}}{2}$$

(2.5)

Figure 2-3 Three curve fitting results

Each  $d_i$  reflects how good the estimated value  $v_{ni}$  computed by its PE is compared to its true value. Small values of  $d_i$  mean the estimated value  $v_{ni}$  is obtained with greater confidence and should carry higher weight in the final voting scheme. On the other hand, when  $d_i$  is large, it means that the estimated value  $v_{ni}$  is not so good and should contribute less to the final voting result. Based on this, the weights for each PE is derived by the following equation (2.6)

$$w_i = \frac{1}{d_i} \tag{2.6}$$

so the final value in differential voting is obtained by

$$v_{vote} = \frac{\sum_{i=1}^{k} (v_{ni} w_i)}{\sum_{i=1}^{k} w_i}$$

(2.7)

## 2.4 System architecture

Figure 2-4 shows the system architecture of the proposed dual network value system. This system has two network structures: a DPN and an IPN. The DPN is responsible for the incoming numerical data processing, including input data space transformation and online dynamic data fitting. The IPN is in charge of the final evaluation of the results provided by DPN. Each data processing element will conduct the three curve fitting scheme as discussed in Section 2.3, and will output the fitted values of  $v_{ni}$ ,  $v_{ui}$  and  $v_{li}$  for information processing elements. These values will provide a rough estimation of the true value as well as its statistical distribution information. Based on this information, each information PE will vote on the final value based on the DV scheme as presented in equations (2.5) ~ (2.7).

Figure 2-4 Pipelined value system architecture

A novel communication channel structure based on the shift-register is presented in Figure 2-4. Each data PE has a set of inputs, and they are pseudo randomly connected to their local channel. The PEs are more likely to be connected to their local neighbors, although some of them may still reach distant PEs.

This architecture processes the information in a way similar to the pipelined shift-register structure. In the first clock cycle, the data is available in the first layer channel, and the first layer data PEs will read this data as their inputs. After processing, PEs will output the transformed data into the same location in the input channel. At the same time, they will also output their estimated value  $v_{ni}$  and its corresponding weight  $w_i$  to the information PE in IPN network. The information PE will combine these local values and their weights according to the following equations and pass them to the next layer of information PE at the next clock cycle.

40

$$v_{l} = \left(\sum w_{i} v_{i}\right)_{l} + v_{l-1}$$

(2.8)

$$w_l = \left(\sum w_i\right)_l + w_{l-1} \tag{2.9}$$

here the subscript "l" means the information from channel layer l. Therefore,  $v_l$ and  $w_l$  are the combined value and weight information for layer l.

When the next clock cycle arrives, the transformed data (the output data of the PEs in the first layer channel) is shifted to the next layer channel as the input data to the data PEs in the second layer, while another set of input data samples can be sent to the first layer channel. Meanwhile, the information PEs in the second layer will combine the information from the second layer with that passed from the previous layer.

All processing elements in the system are active during all clock cycles making this architecture suitable for the dynamic online processing. Finally, when the data reaches the final layer, the final voted value is computed as

$$v_{vote} = \frac{v_l}{w_l} \tag{2.10}$$

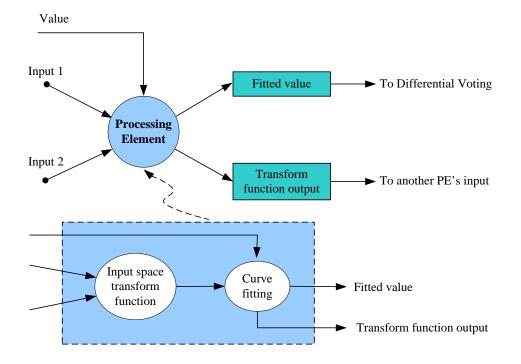

Figure 2-5 shows the local organization and connectivity structure of one data processing element to illustrate how the individual data PE works in the system. During the training stage, the input multidimensional data samples and their corresponding true values are provided as inputs to the local channel. Each PE will use a set of input space transform functions to combine the information from different inputs. Based on the proposed curve fitting technique, each PE will modify its curve fitting coefficients every time a new sample is received. Each PE will also output the numerical value obtained by the input space transformation function. This output will be used as the input of the data processing element

in the next layer after shifting is performed in the routing channel. After training, each data PE has its TCF coefficients determined based on the characteristics of training information.

Figure 2-5 Detailed structure of data PE

In the testing stage, when a testing sample is applied to the inputs of the first layer processing elements of the value system, each data PE will output the three fitted values  $v_{ni}, v_{ui}$  and  $v_{li}$  according to its own fitting curves. All of this information will go to the information processing network for final voting based on the differential voting scheme.

## 2.5 Summary

This chapter presents a novel value system for machine learning. The ability to learn is the foundation of the biological intelligent systems, and forms the first element of the proposed "learning-memory-prediction" framework for machine intelligence. In a supervised learning process, the machine learns the information from a knowledgeable teacher with an explicitly stated goal. However, supervisory learning is not always available, nor is it necessary for biological intelligent systems to learn and process information. Reinforcement learning does not have the requirements of supervised learning. In RL, the machine learns through interaction with the external environment, accumulates knowledge and plans its action to maximize the reward signal and to achieve the goal of its operation. Value system is one of the critical elements for RL. Based on the dynamic curve fitting technology, the proposed value system can accurately and dynamically estimate the value signal for multi-dimensional data set. This value system has two networks (DPN and IPN), and has an efficient pipelined architecture suitable for hardware implementation.

In the value system, signals only propagate forward for the machine to learn the information received from environment. However, this is not enough for building intelligent systems. Feedback is introduced in the learning mechanism for the machine to be able to remember the information in its distributed elements, which leads to the second element of the proposed framework: associative memory.

# **Chapter 3**

# **Self-Organizing Associative Memory**

## **3.1 Introduction**

Biological intelligent systems use a different memory organization than that of digital computers. Their memory is characterized by associations and self-organization, is data driven, has hierarchical structure, and uses distributed information storage. This chapter focuses on the second element of the "learning-memory-prediction" framework: associative memory. In this chapter, the feedforward network presented in [Sta 05a] is further advanced to include a feedback mechanism to learn and remember information from the environment [Sta 06b]. This self-organizing associative memory has a hierarchical organization and can self-adjust its association depth according to the complexity of different application problems. In addition, this memory structure is capable of both auto-association and hetero-association, which co-exist in human brain [Riz 01] [Bro 95] [Mur 97].

## 3.2 Probability based associative learning

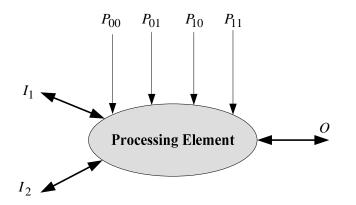

#### **3.2.1 Structure of individual processing elements**

The proposed self-organizing associative memory consists of a multilayer array of processing elements. Figure 3-1 gives the interface model of an individual PE, which consists of two inputs ( $I_1$  and  $I_2$ ) and one output (O). All the inputs and the output are bidirectional,

allowing signals to propagate forward and backward. Each PE stores observed probabilities  $p_{00}$ ,  $p_{01}$ ,  $p_{10}$  and  $p_{11}$  corresponding to four different combinations of inputs  $I_1$  and  $I_2$  ( $\{I_1I_2\} = \{00\}, \{01\}, \{10\}, \{11\}\}$ ), respectively. These probabilities specify data distribution in each PE's input space, and are used to make associations.

Figure 3-1 Individual PE interface model

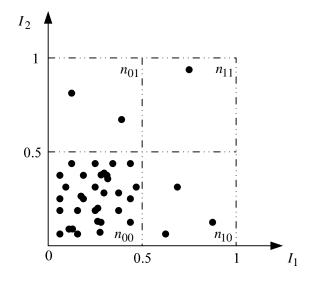

Figure 3-2 gives an example of possible distribution of the observed input data points.

Probabilities are estimated from  $p_{00} = \frac{n_{00}}{n_{tot}}$ ,  $p_{01} = \frac{n_{01}}{n_{tot}}$ ,  $p_{10} = \frac{n_{10}}{n_{tot}}$ ,  $p_{11} = \frac{n_{11}}{n_{tot}}$ , where  $n_{00}$ ,  $n_{01}$ ,  $n_{10}$  and  $n_{11}$  are the number of data points located in  $I_1 < 0.5 \& I_2 < 0.5$ ,  $I_1 < 0.5 \& I_2 < 0.5$ ,  $I_1 > 0.5 \& I_2 < 0.5$  and  $I_1 > 0.5 \& I_2 > 0.5$ , respectively. The value  $n_{tot}$  is the total number of data points defined as  $n_{tot} = n_{00} + n_{01} + n_{10} + n_{11}$ . An efficient algorithm for dynamic estimation of these probabilities without division on unlimited number of input data is proposed in [Sta 04]. Such an estimation is good for on-line learning and hardware implementation. This research takes advantage of the results presented in [Sta 04], and assumes that on-line probability estimation is inexpensive from a hardware point of view.

Figure 3-2 An example of input space distribution

## 3.2.2 Self-determination of the function value

Based on the observed probability distribution  $p_{00}$ ,  $p_{01}$ ,  $p_{10}$  and  $p_{11}$  of an individual PE as in Figure 3-2, each PE decides its output function value F by specifying its truth table as shown in Table 3-1.

| Probability           | <i>P</i> <sub>00</sub> | <i>p</i> <sub>01</sub> | <i>p</i> <sub>10</sub> | <i>p</i> <sub>11</sub> |

|-----------------------|------------------------|------------------------|------------------------|------------------------|

| $I_1$                 | 0                      | 0                      | 1                      | 1                      |

| <i>I</i> <sub>2</sub> | 0                      | 1                      | 0                      | 1                      |

| Function value        | $f_{00}$               | $f_{01}$               | $f_{10}$               | $f_{11}$               |

Table 3-1 Self-determination of function value F

The output function values  $f_{00}, f_{01}, f_{10}$  and  $f_{11}$  are decided as follows:

(1) The input,  $(I_1, I_2)$ , that is associated with the largest probability,  $p_{ij}$ , (i, j = 0, 1),

is assigned a corresponding output function F value of 0.