# Energy Efficient Digital Baseband Modulator for Cable Terminal Systems Targeted on Field Programmable Gate Array

A thesis presented to

the faculty of the

Fritz J. and Dolores H. Russ

College of Engineering and Technology of

Ohio University

In partial fulfillment

of the requirement for the degree

Master of Science

Feng Wang

June 2004

This thesis entitled

Energy Efficient Digital Baseband Modulator for Cable Terminal Systems Targeted on Field Programmable Gate Array

by Feng Wang

has been approved for

the School of Electric Engineering and Computer Science

and the Russ College of Engineering and Technology by

Janusz A. Starzyk

Professor of School of Electrical Engineering and Computer Science

R. Dennis Irwin Dean, Fritz J. and Dolores H. Russ College of Engineering and Technology

# Abstract

Feng Wang. M.S. June 2004. Electrical Engineering and Computer Science

# Energy Efficient Digital Baseband Modulator for Cable Terminal Systems Targeted on Field Programmable Gate Array (100 pp.)

Director of Thesis: Janusz A. Starzyk

This thesis presents design and research in energy efficient digital baseband modulator for cable terminal systems targeted on field programmable gate array (FPGA). The design specifications of the individual processing blocks of digital baseband modulator are reviewed. Existing low power design techniques at algorithm and architecture levels are examined and their effectiveness for low power design on FPGA is investigated based on the power dissipation characteristics of the FPGA. Low power design strategy for the digital modulator is then derived. Finally, the implementation options for several key modules are investigated and the design space of power and area product is explored. In this design, a new parallel finite field multiplier is proposed, the interleaving algorithm is reformulated and rescheduling is used in the TCM modulator to achieve the low power goal. The results of this research show that most of the low power design techniques, except parallelizing, are very effective for energy efficient design in FPGA.

Approved:

Janusz A. Starzyk Professor, EECS

# Acknowledgments

My thesis research could not be accomplished without the help and support from the others. First and foremost, I would like to thank my research advisor Professor Janusz A. Starzyk for his extraordinary help and guidance since I joined the VLSI group. His profound insights into abstract problems and exceptional capabilities to solve them with mathematical model helped me at various time of this thesis work. His high standards of professional conduct and performance serve as a role model for me. Without his financial support, I could not finish my study here. I would also like to thank Professor Jeffrey C. Dill, Professor Xiaoping Shen, and Professor Savas Kaya for reviewing this thesis and providing helpful comments. Also Professor Jeffrey C. Dill's lectures built my coding theory background, which is critical for this thesis work.

Next, I would like to thank my friends in VLSI group. I'd like to thank Zhen Zhu. Zhen's wide knowledge of communication theory and extraordinary skills in the Matlab programming helped me out in various times during the project. I would also like to thank Yinyin Liu for her useful advice in thesis writing. During my two years study in VLSI group, I learned a lot from the other members in the group: Haibo He, Zhineng Zhu, and Mingwei Ding.

Finally, my parents, older brother and my girlfriend, have always been the best support in my life. I would like to express my appreciation to them. My mother's unconditional love

and continual encouragement have been the source of my strength for years even after she passed away. I dedicate this thesis to you with all my love.

# **Table of Contents**

| ABSTRAC   | СТ                                                             | 3  |

|-----------|----------------------------------------------------------------|----|

| ACKNOW    | VLEDGMENTS                                                     | 4  |

| TABLE O   | DF CONTENTS                                                    | 6  |

| LIST OF F | FIGURES                                                        | 9  |

| LIST OF 1 | TABLES                                                         | 11 |

| SYMBOLS   | S AND ABBREVIATIONS                                            | 12 |

| CHAPTER   | R 1 INTRODUCTION                                               | 14 |

| 1.1       | MOTIVATION                                                     | 14 |

| 1.2       | RESEARCH GOALS                                                 | 16 |

| 1.3       | THESIS ORGANIZATION                                            | 16 |

| CHAPTER   | <b>R 2</b> SPECIFICATION FOR DIGITAL BASEBAND MODULATOR DESIGN | 18 |

| 2.1       | INTRODUCTION                                                   | 18 |

| 2.2       | MPEG-2 TRANSPORT LAYER                                         | 19 |

| 2.3       | MPEG-2 TRANSPORT FRAMING                                       | 20 |

| 2.4       | FORWARD ERROR CORRECTION                                       | 21 |

| 2.4.1     | Reed-Solomon coding                                            | 23 |

| 2.4.2     | 2 Interleaving                                                 | 25 |

| 2.4.3     | 8 Randomization                                                | 28 |

| 2.4.4     | Trellis coded modulator                                        | 29 |

| 2.5       | MODULATION AND DEMODULATION                                    | 41 |

| 2.5.1     | QAM characteristics                                            | 41 |

| СНАРТЕБ   | R 3 LOW POWER DESIGN                                           | 43 |

| 3.1    | INTRODUCTION                                        | 7<br>43 |

|--------|-----------------------------------------------------|---------|

| 3.2    | SOURCES OF POWER CONSUMPTION                        | 43      |

| 3.3    | Low power design techniques                         | 46      |

| 3.3.   | 1 Algorithm level optimization                      | 46      |

| 3.3.   | 2 Architectural level optimization                  | 48      |

| 3.4    | LOW POWER DESIGN STRATEGY FOR THE DIGITAL MODULATOR | 50      |

| СНАРТН | ER 4 LOW POWER DESIGN OF DIGITAL MODULATOR          | 51      |

| 4.1    | INTRODUCTION                                        | 51      |

| 4.2    | REED SOLOMON ENCODER                                | 51      |

| 4.3    | TRELLIS CODED MODULATION                            | 65      |

| 4.4    | Interleaver design                                  | 70      |

| 4.5    | MPEG FRAMER                                         | 79      |

| СНАРТИ | ER 5 SIMULATION AND RESULTS                         | 86      |

| 5.1    | INTRODUCTION                                        | 86      |

| 5.2    | RS ENCODER                                          | 86      |

| 5.3    | TRELLIS CODED MODULATION                            | 87      |

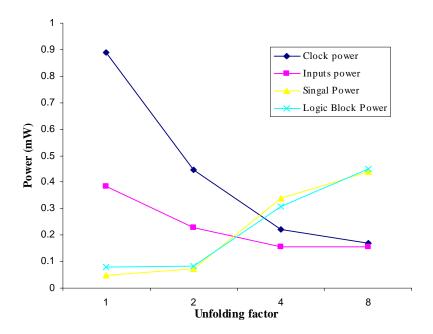

| 5.3.   | 1 Data parser                                       | 87      |

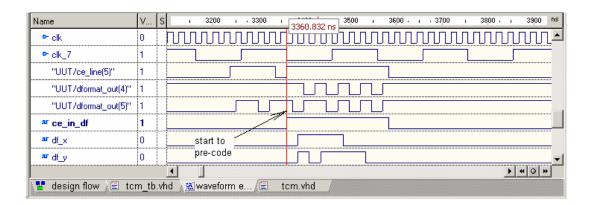

| 5.3.   | 2 Differential pre-coder                            | 88      |

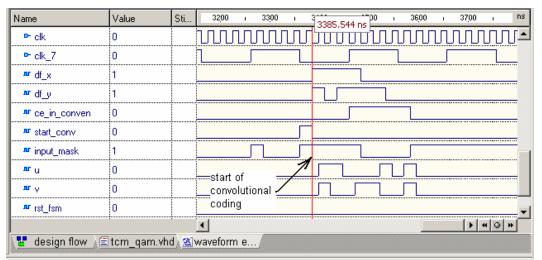

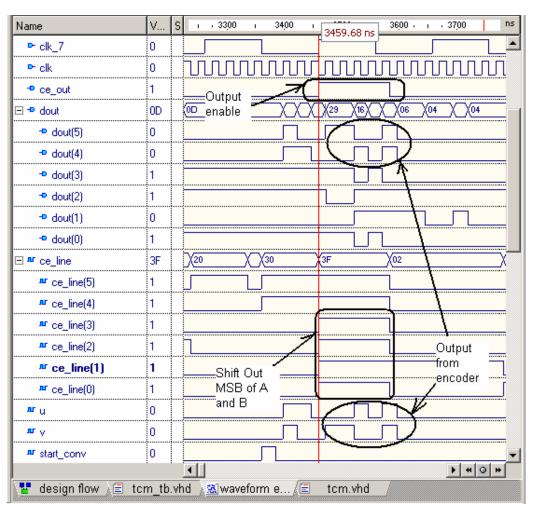

| 5.3.   | 3 Binary convolutional coder                        | 89      |

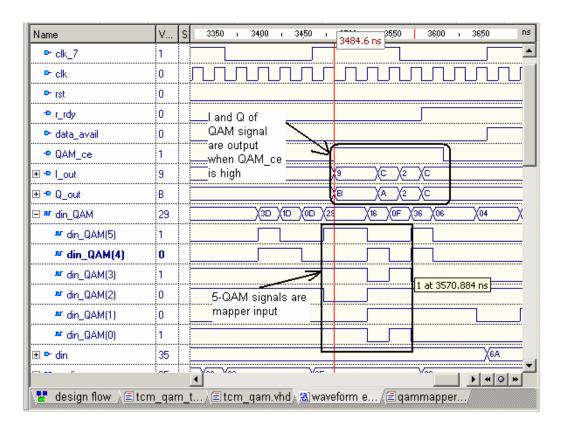

| 5.3.   | 4 QAM mapper                                        | 91      |

| 5.4    | INTERLEAVER DESIGN                                  | 92      |

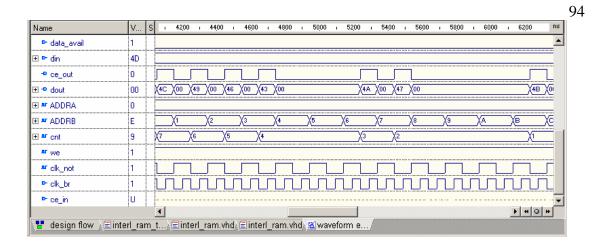

| 5.5    | RANDOMIZER                                          | 94      |

| 5.6    | MPEG FRAMER                                         | 95      |

| СНАРТИ | ER 6 CONCLUSIONS AND FUTURE WORK                    | 96      |

| 6.1    | Conclusions                                         | 96      |

| 6.2     | Future work | 8<br>98 |

|---------|-------------|---------|

| REFEREN | NCES        |         |

# List of Figures

| Fig. 2.1 Cable transmitter block diagram                                    | 19 |

|-----------------------------------------------------------------------------|----|

| Fig. 2.2 Checksum generator for the MPEG-2 sync byte encoder [ITU J.83]     | 21 |

| Fig. 2.3 Forward Error Correction block diagram                             | 22 |

| Fig. 2.4 Interleaving functional block diagram [ITU J.83]                   | 26 |

| Fig. 2.5 Block diagram of 7-bit symbol randomizer                           | 28 |

| Fig. 2.6 64-QAM trellis coded modulator block diagram [ITU J.83]            | 30 |

| Fig. 2.7 64-QAM trellis group [ITU J.83]                                    | 31 |

| Fig. 2.8 256-QAM trellis coded modulator block diagram [ITU J.83]           | 33 |

| Fig. 2.9 256-QAM sync and non-sync trellis group [ITU J.83]                 | 34 |

| Fig. 2.10 Block diagram of the differential pre-encoder [ITU J.83]          | 35 |

| Fig. 2.11 Punctured Binary Convolutional Coder [ITU J.83]                   | 37 |

| Fig. 2.12 64-QAM constellation [ITU J.83]                                   | 39 |

| Fig. 2.13 256-QAM constellation [ITU J.83]                                  | 40 |

| Fig. 4.1 Block diagram for the extended RS Solomon encoder                  | 53 |

| Fig. 4.2 Block diagram of the array multiplier over GF (2 <sup>7</sup> )    | 56 |

| Fig. 4.3 Block diagram of the multiplier (C=A*alpha^52) over GF(2^7)        | 62 |

| Fig. 4.4 Block diagram of the convolutional coder                           | 66 |

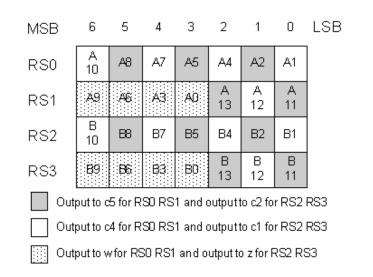

| Fig. 4.5 RS symbols to Trellis Group bit ordering                           | 66 |

| Fig. 4.6 Block diagram of the data formatter using direct map method        | 67 |

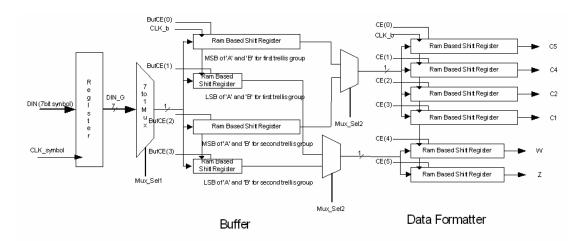

| Fig. 4.7 Block diagram of the modified data formatter                       | 69 |

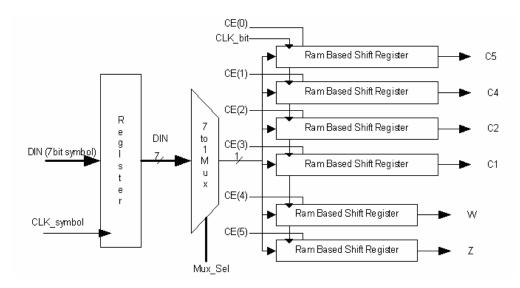

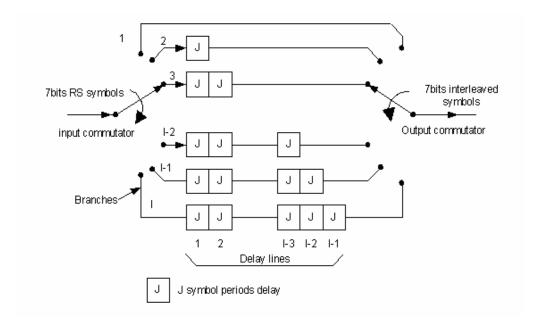

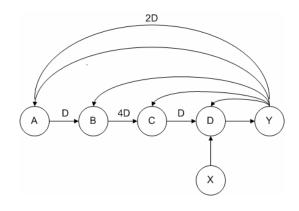

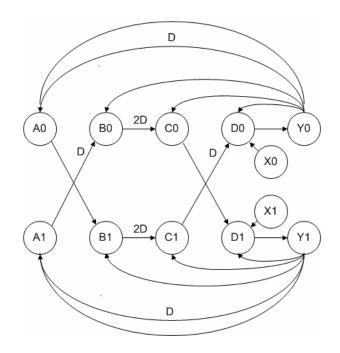

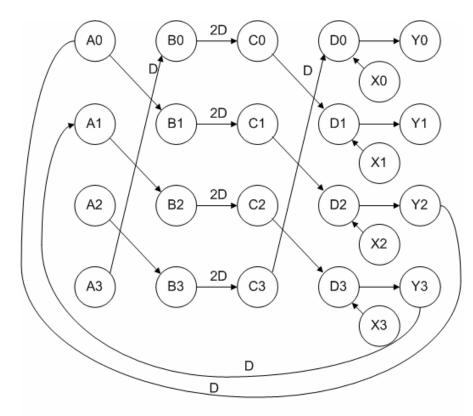

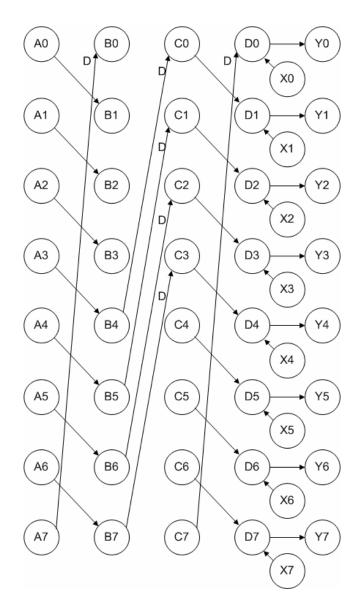

| Fig. 4.8 ITU J.83 convolutional interleaver (I, J) functional block diagram | 71 |

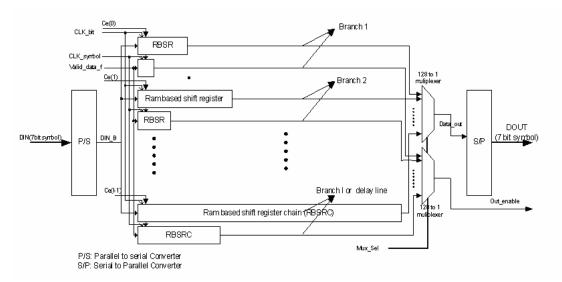

|                                                                                         | 10   |

|-----------------------------------------------------------------------------------------|------|

| Fig. 4.9 Block diagram of the interleaver using the RAM based shift register            | -    |

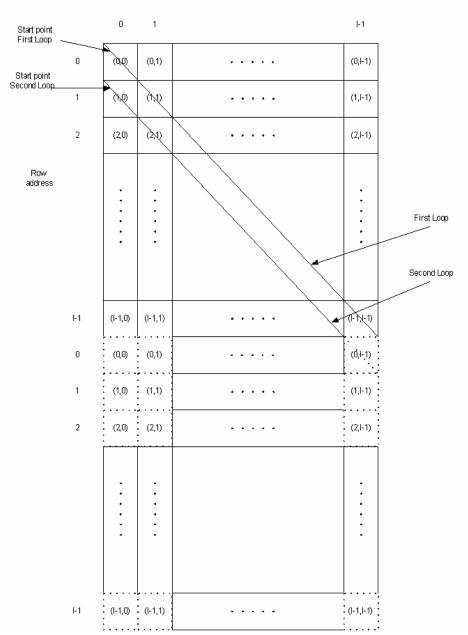

| Fig. 4.10 Memory map of the Interleaver using matrix format                             | . 76 |

| Fig. 4.11 Replicating the data path in (a) by factor 2 in (b), 4 in (c) and 8 in (d) 80 | )-82 |

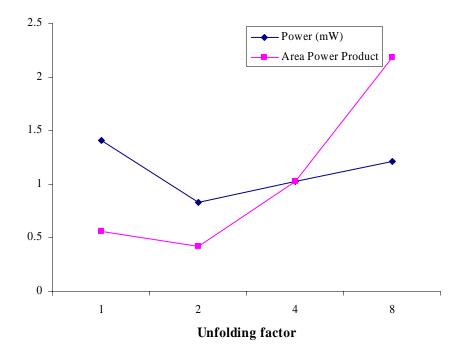

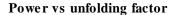

| Fig. 4.12 Performance of the parallelizing the design by a factor of 1, 2, 4 and 8      | . 83 |

| Fig. 4.13 Power of the parallelizing the design by a factor of 1, 2, 4 and 8            | . 84 |

| Fig. 5.1 Simulation waveforms of RS encoder                                             | . 87 |

| Fig. 5.2 Simulation waveforms of data parser                                            | . 88 |

| Fig. 5.3 Simulation waveforms of differential pre-coder                                 | . 89 |

| Fig. 5.4 Simulation waveforms of differential pre-coder                                 | . 90 |

| Fig. 5.5 Simulation waveforms of formation of the 5QAM symbols                          | . 91 |

| Fig. 5.6 Simulation waveforms of formation of the 5QAM symbols                          | . 92 |

| Fig. 5.7 Signal waveforms at the interleaving starts                                    | . 93 |

| Fig. 5.8 Signal waveforms at the interleaving ends                                      | . 94 |

| Fig. 5.9 Simulation waveform of randomizer                                              | . 94 |

# List of Tables

| Table 2.1 Level 1 interleaving [ITU J.83]                                      | 27 |

|--------------------------------------------------------------------------------|----|

| Table 2.2 Level 2 interleaving [ITU J.83]                                      | 27 |

| Table 2.3 Cable transmission format [ITU J.83]                                 | 41 |

| Table 2.4 Variable interleaving modes [ITU J.83]                               | 42 |

| Table 3.1 Capacitance of the resources of Virtex II (2v1000FG256-5) [ Shang02] | 45 |

| Table 4.1 Performance of RS encoders using different multipliers               | 64 |

| Table 4.2 Comparison between two methods in area and power                     | 70 |

# Symbols and Abbreviations

| ASIC   | Application Specific Integrated Circuit           |  |

|--------|---------------------------------------------------|--|

| ATM    | Asynchronous Transfer Mode                        |  |

| CAD    | Computer Aided Design                             |  |

| CLB    | Configurable Logic Block                          |  |

| DFG    | Data Flow Graph                                   |  |

| DOCSIS | Data Over Cable Service Interface Specification   |  |

| FEC    | Forward Error Correction                          |  |

| FPGA   | Field Programmable Gate Array                     |  |

| GF     | Galois Field                                      |  |

| IP     | Intellectual Property                             |  |

| ITU    | International Telecommunication Union             |  |

| LFSR   | Linear Feed Shift Register                        |  |

| LSB    | Least Significant Bit                             |  |

| LUT    | Look Up Table                                     |  |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |  |

| MPEG   | Moving Picture Experts Group                      |  |

| MSB    | Most Significant Bit                              |  |

| PN     | Pseudorandom Noise                                |  |

| QAM    | Quadrature Amplitude Modulation                   |  |

| RAM    | Random Access Memory                              |  |

| RISC  | Reduced Instruction Set Computer    |

|-------|-------------------------------------|

| RS    | Reed-Solomon                        |

| ТСМ   | Trellis Coded Modulation            |

| VHDL  | VHSIC Hardware Description Language |

| VHSIC | Very High Speed Integrated Circuit  |

| VLSI  | Very Large Scale Integration        |

# **Chapter 1** Introduction

#### **1.1 Motivation**

Cable communications system has become the major technology for the broadband internet access. Data Over Cable Service Interface Specification (DOCSIS) compatible cable modem chips from Broadcom and Texas Instruments dominate this competitive market. Xilinx has recently released Intellectual Property (IP) core for the key module, International Telecommunication Union (ITU) J.83 modulator, targeted on FPGA device to allow the other vendors to integrate this broadband access module to their products.

This thesis approaches the cable terminal system design on FPGA from the perspective that low power is most desirable feature. A number of choices, including full custom, standard cell, and FPGA, exist when implementing a digital integrated circuit design. Full custom design is time consuming and can achieve highest performance with fixed functionalities. The standard cell library approaches shorten the design cycle by scarificing performance. The FPGA based design has same critical advantages over these two methods by offering higher flexibility and shorter design time. With reprogrammable features, the design bugs can be fixed with minimal effort and cost. This greatly reduces the design cost and time, especially for low volume design.

Moore's law, which is often stated as the doubling of transistor performance and quadrupling of the number of devices on a chip every three years, has been achieved through scaling of the MOSFET [Doyle02]. Design density and speed are gained through the advances in the semiconductor process technology. Though the performance of the programmable logic lags behind the full custom design [Kusse98], the high performance and high density FPGA embedded with RISC processor is available, for example, in Xilinx Virtex II. Area and speed may then not be the first design priority for the FPGA in many applications, such as cable communication terminal system, and the low-power design becomes a dominant cost factor. As a result, new applications emerge by applying the low power design technology to FPGA based design. For instance, in cable telephone, a desirable feature is obtaining the power from the cable.

FPGAs are traditionally considered as power-hungry devices since their programmability is provided by a large amount of the routing resources and switches that consume a lot of dynamic switching power. Low power design for VLSI has received a lot of attention due to the proliferation of mobile and portable devices. Nevertheless, research in low power FPGA design has only recently gained its popularity due to its unique features in terms of flexibility and signal processing capabilities [Kusse98, George99]. However, its energy inefficiency is a limiting factor for the wide acceptance in mobile and portable applications. In addition, it is difficult to estimate the power consumption during the early phase of the design due to the lack of detailed information about the FPGA circuits. Thus the low power design of FPGA remains a challenging problem.

#### **1.2 Research goals**

The goal of this research is to apply the existing low design techniques to digital modulator design on FPGA and to gain a better understanding of the effectiveness of these design methods. The research is focused on the design of several key modules of the digital modulator and optimizing the design for low power purpose at the algorithm and arithmetic levels.

### **1.3 Thesis organization**

This thesis is organized into six chapters. Chapter 2 presents the system specifications of the digital baseband modulator and describes the components for this digital baseband modulator according to the ITU J.83 standard. In this chapter, the framing structure, channel coding, and channel modulation for a digital multi-service television distribution system that is specific to a cable channel is presented. The chapter also covers the features of both 64- and 256-QAM modulation schemes.

Chapter 3 discusses the sources of power dissipation, reviews the existing low power design techniques at the algorithmic and the architectural levels, examines their applicability to FPGA technology and finally derives the design strategy for this digital modulator design.

Chapter 4 applies the low power design techniques to the design of the several key modules including MPEG framer, Reed Solomon Encoder, interleaver, and TCM modulator. Design space is explored and several new structures are proposed.

Chapter 5 provides the simulation results of designed circuits, verifying their performance according to specifications.

Chapter 6 gives a conclusion of the work done, summarizes major results obtained for the thesis and discusses the future work.

# Chapter 2 Specification for Digital Baseband Modulator Design

## 2.1 Introduction

The specification of the ITU Recommendation J.83 Annex B is presented in this chapter. This specification describes the framing structure, channel coding, and channel modulation for a digital multi-service television distribution system that is specific to a cable channel.

Two types of the modulation schemes are used, Quadrature Amplitude Modulation (QAM) with 64-point signal constellation (64QAM) and with 256-point signal constellation. In this chapter, the common features and differences of both modulation schemes are presented.

The design of the modulation, interleaving and coding is based upon testing and characterization of cable systems in North America using 6MHz channeling [ITU J.83]. Concatenated coding schemes, including two encoders and an interleaver are used in Forward Error Correction (FEC) due to their high bit error rate performances with low complexity and low overhead.

MPEG-2 transport layer data stream is the input to this digital modulator. But the synchronization of the MPEG stream is independent from the FEC synchronization,

which can avoid the interference with ATM synchronization. There are two modes supported: Mode 1 has a symbol rate of 5.057 Msymbols/s and it is used for 64-QAM; Mode 2 has a symbol rate of 5.361 Msymbols/s and is typically employed for 256-QAM [ITU J.83]. This system can be easily upgraded to higher order QAM extensions.

The appropriate error correction and demodulation are determined by the expected channel error statistics and distortion characteristics. The cable channel is primarily regarded as a bandwidth-limited linear channel, with a balanced combination of white noise, interference, and multi-path distortion and the QAM technique used, together with adaptive equalization and concatenated coding is well suited to this application and channel [ITU J.83].

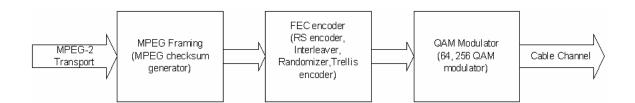

The block diagram of the whole digital modulator is shown in Fig.2.1. The specification of each processing block is presented as follows.

Fig. 2.1 Cable transmitter block diagram

#### 2.2 MPEG-2 transport layer

The MPEG-2 transport layer is defined in Reference [ITU H.222]. Each frame in the transport layer for MPEG-2 has 4 bytes header, which contains one synchronization byte

$47_{\text{HEX}}$ , three bytes service identification, scrambling and control information, and 184 bytes of data.

# 2.3 MPEG-2 transport framing

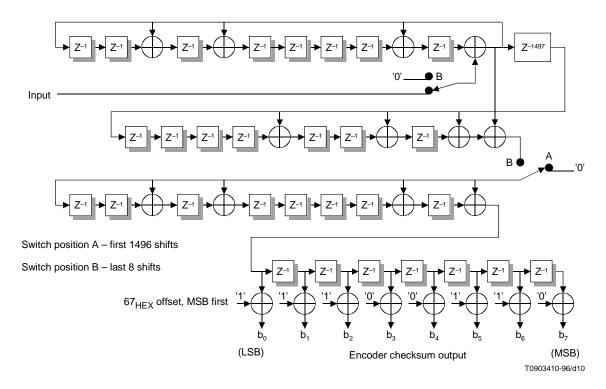

The MPEG transport framing provided a synchronization mechanism for the robust communication in this layer. Out of the 188-byte data steame in serial format, most significant bit (MSB) is first processed by this block. In addition to the sync byte, a parity checksum is used to improve the delineation functionality and add the additional error detection capability. This checksum is calculated over the 187 bytes following the sync byte. Linear Feedback Shift Register (LFSR) f(x) is used to generate this checksum. According to specifications provided in [ITU J.83], the LFSR is based on the following equations:

$$f(x) = [1 + x^{1496}b(x)]/g(x)$$

(2.1)

Where  $g(x) = 1 + x + x^5 + x^6 + x^8$  and  $b(x) = 1 + x + x^3 + x^7$

The structure of this checksum generation function is shown in Fig. 2.2. All the additional operations are modulo 2 and the LFSR is reset to all zeros before the processing of a new frame. The 187-byte data is fed into the LFSR in a serial fashion, the MSB first at the bit rate. The feedback network implements the g(x). An offset of  $67_{HEX}$  is added to this checksum result for improved autocorrelation properties, and causes a  $47_{HEX}$  result to be produced during a syndrome decode operation when a valid code word is presented [ITU J.83]. The 8-bit checksum is appended to the 187-byte data and transmitted in MSB first.

Fig. 2.2 Checksum generator for the MPEG-2 sync byte encoder [ITU J.83]

#### 2.4 Forward error correction

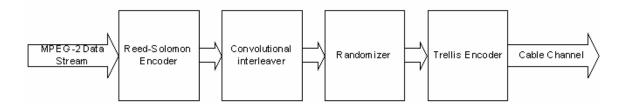

Two levels of coding, an inner coder and outer coder, are employed in the Forward Error Correction (FEC) to achieve high error correcting performance. The inner coder interfaced with the modulator and the channel is configured to correct most of the channel errors, and the outer coder with a high code rate reduced the probability of error to the specified level [Sklar01]. Interleaving and randomization are used between the inner and outer coder to prevent the degradation of error correcting performance caused by correlated errors among successive symbols. Then the overall implementation complexity is reduced to achieve a low error rate by using the concatenated coding scheme. As shown in Fig.2.3, the FEC consists of four processing blocks: Reed Solomon encoding, Convolutional interleaving, Randomizer, and Trellis encoder. FEC has its own synchronization mechanism and is independent from the input data protocols.

Fig. 2.3 Forward Error Correction block diagram

Two types of coding schemes and interleaving techniques are employed to ensure the reliability of the data transmission over the cable channel:

- Extended (128, 122) Reed Solomon (RS) coder Provides block encoding and has the capability of correcting up to three symbols within an RS block.

- Convolutional interleaver The input symbols delayed by different length result in spreading the errors over several code words. RS encoding together with interleaving provide for the correction of the burst errors that decoder can not correct [Sklar01]

- Randomizer Randomizes the data over the channel adding the additional information to allow effective QAM demodulator synchronization [ITU J.83].

• Trellis Encoder – Provides convolutional encoding.

#### 2.4.1 Reed-Solomon coding

Reed-Solomon codes are block-based error correcting codes and their error correcting ability is determined by the bit redundancy, (n, k). Reed-Solomon code can correct up to (n-k)/2 symbol errors. Reed-Solomon codes are particularly well suited to correct the burst errors and are widely applied in communication. A systematic RS coder (128, 122) over Galois Field (GF) (128) is employed to code the data of MPEG transport layer. This extended RS code can correct up to t=3 symbols errors contained in a codeword, where 2t = 128-122. Both 64-QAM and 256-QAM use this RS code.

The implementation of the extended RS encoder is described as follows. The extended RS code over GF(128) is constructed with the systematic encoder. The primitive polynomial used to generate all the elements over GF(128) is:

$$p(x) = x^7 + x^3 + 1 \tag{2.2}$$

The (128,122) RS codeword is generated using the generating polynomial:

$$g(x) = (x+\alpha)(x+\alpha^{2})(x+\alpha^{3})(x+\alpha^{4})(x+\alpha^{5})$$

=  $x^{5} + \alpha^{52}x^{4} + \alpha^{116}x^{3} + \alpha^{119}x^{2} + \alpha^{61}x + \alpha^{15}$  (2.3)

Where, the primitive element  $\alpha$  is a root of a primitive polynomial of the field, i.e.  $p(\alpha) = 0$  [ITU J.83]. The message block including 122, 7-bit symbols can be expanded in a polynomial format as follows

$$m(x) = m_{121} x^{121} + m_{120} x^{120} + \dots + m_1 x^1 + m_0$$

(2.4)

First, five parity symbols can be obtained as

$$r(x) = r_4 x^4 + r_3 x^3 + r_2 x^2 + r_1 x + r_0$$

(2.5)

Then, the first parity symbols in a systematic Reed-Solomon codeword are given by the remainder of  $m(x) \cdot x^5 \mod g(x)$ .

The message block appended with the five parity symbols forms a new polynomial referred to as an even multiple of the generator polynomial, and can be represented as the following polynomial:

$$c(x) = m_{121} x^{126} + m_{120} x^{125} + \dots + m_1 x^6 + m_0 x^5 + r_4 x^4 + r_3 x^3 + r_2 x^2 + r_1 x + r_0$$

(2.6)

The extended parity symbol  $c_{128}$  is generated by evaluating the code word at the sixth power of  $\alpha$  [ITU J.83].

$$c_{128} = c(\alpha^6) \tag{2.7}$$

The code c(x) appended with this extended parity symbol forms the final 128 symbol Reed-Solomon block:

$$code(x) = xc(x) + c_{128}$$

=  $m_{121} x^{127} + m_{120} x^{126} + \dots + m_1 x^7 + m_0 x^6 + r_4 x^5 + r_3 x^4 + r_2 x^3 + r_1 x^2 + r_0 x + c_{128}$  (2.8)

The codeword of this (128, 122) RS encoder is transmitted in the order of MSB first,  $m_{121}m_{120}...m_1m_0r_4r_3r_2r_1r_0c_{128}$  with  $m_{121}$  transmitted as the first bit. 24

#### 2.4.2 Interleaving

The Forney Convolutional interleaver, employed between the RS encoder and the randomizer, has the capability to correct the burst errors. The convolutional interleaver is used for both 64-QAM and 256-QAM.

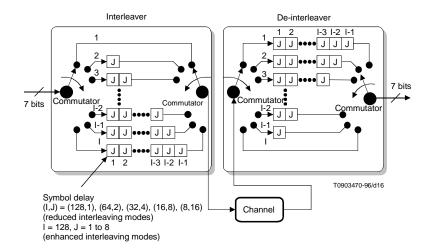

Fig.2.4 shows the operation of the convolutional interleaver. The input symbols from RS encoder appear at the input commutator and the interleaved data is output from the output commutator. An (I, J) interleaver, has I branches. Each branch has a bank of registers (the width of the register is 7, the same as the RS symbol size) and each register has a delay of J symbol periods. Symbol period is given and equals to 7 bit clock periods. The register clock depends on its width. Clock for register width of 7 is 7 clock periods, while for a register width of 1 equals 1 clock period. There is no register at the first branch, labeled with 1. The k-th branch has (k-1) registers and the corresponding path delay equals (k-1)\*J symbol periods delay. The input and output commutator can be referred to as the interleaving commutator. These two interleaving commutators are reset to the top-most branch and move to the next branch at the RS symbol frequency. After reaching the last branch, the interleaving commutators rotate back to the top-most branch. A series of bad symbols caused by the burst noise in the channel are spread over many RS blocks by the de-interleaver, such that the resultant symbol errors per block are within the range of the RS decoder correction capability [ITU J.83].

Fig. 2.4 Interleaving functional block diagram [ITU J.83]

Two distinct operating modes, level 1 and level 2, provide two distinct levels of interleaving capability. In level 1, a single interleaving depth (128, 1) is used in the 64-QAM modulation schemes. The level 2 shall encompass 64-QAM and 256-QAM transmission, and will for both modulation schemes be capable of supporting variable interleaving [ITU J.83]. The interleaving depths is enlarged and reduced by a certain factor. For instance, the reduced modes are (64,2), (32, 4), ..., (8, 16). The synchronization bytes of the FEC frame contains the interleaving configuration parameters, which are available for the deinterleaver at the receiver side.

Table 2.1 describes the interleaver parameters for level 1 operation, with associated latency and burst protection [ITU J.83]. Table 2.2 describes the decoding of the 4-bit in-

band control word into the I and J interleaving parameters for level 2 operation, also with associated burst protection and latency [ITU J.83].

| Control<br>word<br>(4 bits) | I (# of taps) | J (increment) | Burst<br>protection | Latency |

|-----------------------------|---------------|---------------|---------------------|---------|

| Xxxx                        | 128           | 1             | 95 μs               | 4.0 ms  |

Table 2.1 Level 1 interleaving [ITU J.83]

| Control<br>word<br>(4 bits) | I (# of<br>taps) | J (increment) | Burst<br>protection<br>64-QAM/256-QAM | Latency<br>64-QAM/256-QAM |

|-----------------------------|------------------|---------------|---------------------------------------|---------------------------|

| 0001                        | 128              | 1             | 95 μs /66 μs                          | 4.0 ms/2.8 ms             |

| 0011                        | 64               | 2             | 47 μs /33 μs                          | 2.0 ms/1.4 ms             |

| 0101                        | 32               | 4             | 24 µs /16 µs                          | 0.98 ms/0.68 ms           |

| 0111                        | 16               | 8             | 12 μs /8.2 μs                         | 0.48 ms/0.33 ms           |

| 1001                        | 8                | 16            | 5.9 μs /4.1 μs                        | 0.22 ms/0.15 ms           |

| 1011                        | Reserved         |               |                                       |                           |

| 1101                        | Reserved         |               |                                       |                           |

| 1111                        | Reserved         |               |                                       |                           |

| 0000                        | 128              | 1             | 95 μs /66 μs                          | 4.0 ms/2.8 ms             |

| 0010                        | 128              | 2             | 190 µs /132 µs                        | 8.0 ms/5.6 ms             |

| 0100                        | 128              | 3             | 285 μs /198 μs                        | 12 ms/8.4 ms              |

| 0110                        | 128              | 4             | 379 µs /264 µs                        | 16 ms/11 ms               |

| 1000                        | 128              | 5             | 474 μs /330 μs                        | 20 ms/14 ms               |

| 1010                        | 128              | 6             | 569 μs /396 μs                        | 24 ms/17 ms               |

| 1100                        | 128              | 7             | 664 µs /462 µs                        | 28 ms/19 ms               |

| 1110                        | 128              | 8             | 759 μs /528 μs                        | 32 ms/22 ms               |

Table 2.2 Level 2 interleaving [ITU J.83]

#### 2.4.3 Randomization

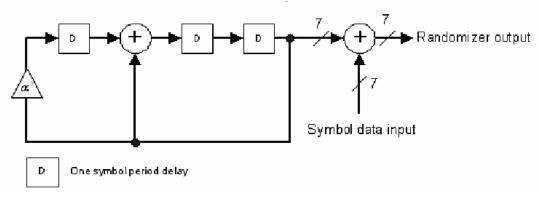

As shown in Fig.2.5, the randomizer is the third function block in the FEC block diagram. The randomizer provides for even distribution of the symbols in the constellation, which enables the demodulator to maintain proper lock [ITU J.83]. 7-bit Pseudorandom Noise (PN) sequence is added to the data symbols to generate a random transmitted sequence.

For both 64- and 256-QAM, the randomizer is reset to all ones during the FEC frame trailer, so the randomization is not applied to the trailer. The randomizer can be represented as a polynomial over the GF(128). It can be realized as a feed back network with the finite field addition and delay terms. The randomizer is first initialized to be in "111\_1111" state. All the operations are performed over the GF(128).

$$f(x) = x^3 + x + \alpha^3$$

(2.9)

where  $\alpha$  is an root of the primitive polynomial  $p(x) = x^7 + x^3 + 1$  and  $p(\alpha) = 0$ .

Fig. 2.5 Block diagram of 7-bit symbol randomizer

#### 2.4.4 Trellis coded modulator

Trellis coded modulation (TCM) scheme has the high spectral efficiencies. This efficiency is achieved by expanding the size of the signal constellation, instead of expanding the bandwidth, which results in a high code performance.

# 2.4.4.1 64-QAM modulation mode

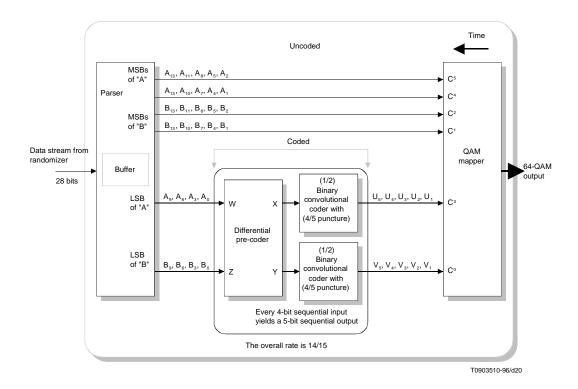

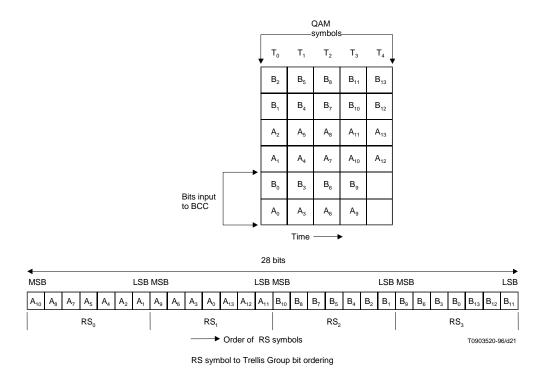

As shown in Fig.2.6, 64 QAM Trellis coded modulator is composed of four types of function blocks: Parser, differential pre-coder, binary puncture convolutional coder and QAM mapper. 28 bits data stream from the randomizer form an input group and the modulator generates 30 bits QAM symbols. So the overall code rate for this modulator is 14/15.

28 bits data groups consist of four 7-bit symbols referred to as 'A' and 'B' as shown in Fig. 2.7. The first two RS symbols are labeled as 'A' and the remaining two RS symbols are labeled as 'B'. The LSB of 'A' and 'B' are first differentially pre-coded and then fed into the binary puncture convolutional coder. The convolutional coder generates two groups of five code bits, which are labeled as U5 U4 U3 U2 U1 and V5 V4 V3 V2 V1 from four input bits. These two five bits data streams are sent to the QAM mapper. The MSB of 'A' and 'B' are uncoded and sent to the QAM mapper directly. The whole bit stream is aligned with the 7-bit RS symbol and is serialized MSB first.

Fig. 2.6 64-QAM trellis coded modulator block diagram [ITU J.83]

Fig. 2.7 64-QAM trellis group [ITU J.83]

## 2.4.4.2 256-QAM modulation mode

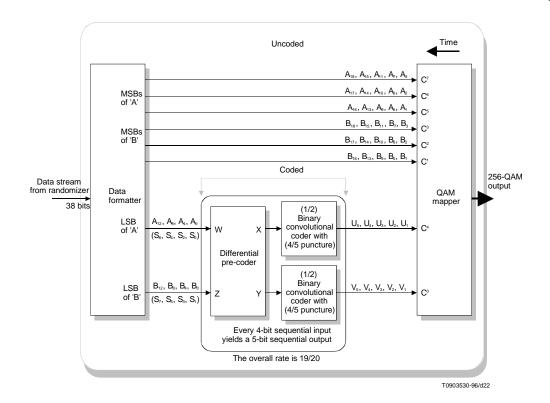

256-QAM trellis coded modulator is shown in Fig.2.8. As the 64-QAM modulator, 256-QAM modulator consists of four function blocks: data formatter, differential pre-coder, binary puncture convolutional coder and QAM mapper. There is slight difference between the 256-QAM and 64-QAM modulator. 38 bits data stream from the randomizer forms an input group. The modulator generates 40 bits 5-QAM symbols, so the overall code rate for this modulator is 19/20.

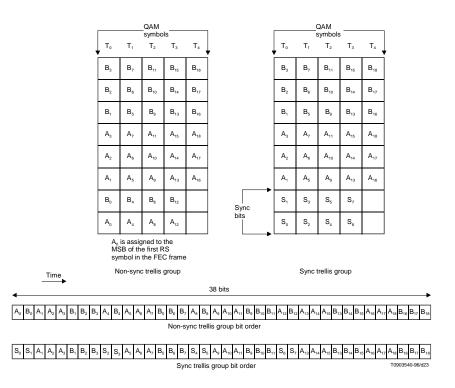

As shown in Fig. 2.9, the input 38 bits data have two different formats, which can be defined as non-sync group and sync group. In a non-sync group, only data bits form the input 38 bits data group. For a sync group, 30 bits data and 8 bits sync byte, which appear at the end of the FEC frame, contribute to the 38 bits data group. The MSB of the 'A' and 'B' are uncoded and fed into the QAM mapper directly. The so-called LSB of 'A' and 'B' are first differentially pre-coded and then sent to the binary puncture convolutional coder. The convolutional coder generates two groups of five code bits, which are labeled as U5 U4 U3 U2 U1 and V5 V4 V3 V2 V1 from four input bits. These two five bits data streams are sent to the QAM mapper. The difference between 64-QAM modulator and 256-QAM modulator lies in the first functional block. Data formatter, instead of data parser is used in 256-QAM modulator, to deal with non-sync group and sync group data formats. For the non-sync group the first bit of the RS symbol bit stream forms the LSB of 'A' and the second bit of the RS symbol bit stream is referred to as the LSB of 'B'. For sync group, the 0<sup>th</sup>, 2<sup>nd</sup>, 4<sup>th</sup> and 6<sup>th</sup> bit of sync byte forms the 'LSB' of A and 1<sup>st</sup>, 3<sup>rd</sup>, 5<sup>th</sup>, 7<sup>th</sup> bits are referred as the 'LSB' of 'B'. The bit stream is aligned with the 7-bit RS symbol and is serialized with the MSB first.

Fig. 2.8 256-QAM trellis coded modulator block diagram [ITU J.83]

Fig. 2.9 256-QAM sync and non-sync trellis group [ITU J.83]

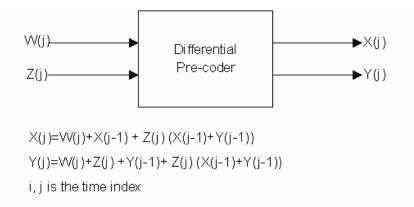

## 2.4.4.3 Rotationally invariant pre-coding

As shown in Fig.2.10, differential pre-encoder is employed to take advantage of the "rotationally invariant" property of the nonlinear, trellis encoder. For a code with 90° invariant property, the correct sequence can be recovered after decoding even if the decoder locks on the wrong phase (multiple of 90°). It is a desirable feature for a robust modem. Non-rotationally invariant coding requires resynchronization of the FEC when

the carrier phase tracking changes quadrant alignment, leading to a burst of errors at the FEC output [ITU J.83].

Both 64-QAM and 256-QAM modulation schemes use the rotationally invariant encoding. In Fig. 2.6, the inputs to the differential encoder are the  $3^{rd}$  and the  $6^{th}$  of 6-bit symbols, and C<sup>3</sup> and C<sup>0</sup> are the outputs of the differential encoder bits in 64-QAM; in Fig. 2.8 the inputs to the differential encoder are the  $4^{th}$  and the  $8^{th}$  of 6-bit symbols, and C<sup>4</sup> and C<sup>0</sup> is the output of the differential encoder bits in 256 QAM.

Fig. 2.10 Block diagram of the differential pre-encoder [ITU J.83]

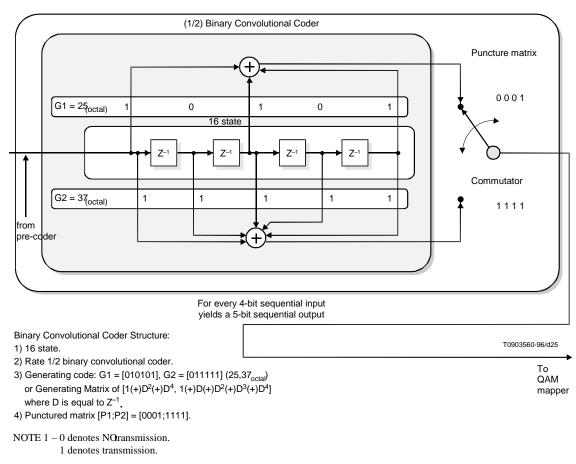

# 2.4.4.4 Binary Convolutional Coder

Fig. 2.11 shows the binary non-systematic convolutional coder with constraint length equal to 4. There are two output branches, so the code rate is  $\frac{1}{2}$ . The generators that characterize the encoding functions are G1 = 010 101 and G2 = 011 111 (25,37<sub>octal</sub>). Four

data bits form a trellis group and are fed into this encoder at the bit rate. When the first bit is shifted into the encoder, encoded data bits are output from both upper and lower branches. Before the last data bit shifts out of the shift registers, the encoder generates eight bits data on both output branches. The output switch samples the data bits at the output branches according to the puncture matrix. The puncture matrix defines when the data sampled will be transmitted. The puncture matrix for this convolutional coder is  $\begin{bmatrix} P_1 \\ P_2 \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 1 \\ 1 & 1 & 1 & 1 \end{bmatrix}$  ("0" denotes NO transmission, "1" denotes transmission). It means the output switch is reset to the upper branch when the first bit is shifted into the encoder and move to the lower branch when all the four bits are shifted into the encoder. The puncture matrix essentially converts the rate 1/2 encoder to the rate 4/5, since only 5 of the 8 encoded bits are retained after puncturing [ITU J.83].

NOTE 2 - (+) denotes XOR operation.

Fig. 2.11 Punctured Binary Convolutional Coder [ITU J.83]

### 2.4.4.5 QAM constellation mapping

For 64-QAM, 6-bit data from the MSB of 'A' and 'B' and outputs of convolutional encoder are converted to the 6-bit constellation symbol according to Fig. 2.12 in the QAM mapper.

For 256-QAM, 8-bit data from the MSB of 'A' and 'B' and outputs of convolutional encoder are converted to the 6-bit constellation symbol according to Fig. 2.13 in the QAM mapper.

|         |         |         | (       | ລ<br><b>↑</b> |         |         |         |                                                                                             |

|---------|---------|---------|---------|---------------|---------|---------|---------|---------------------------------------------------------------------------------------------|

| 110,111 | 111,011 | 010,111 | 011,011 | 100,101       | 101,111 | 110,101 | 111,111 | C <sup>5</sup> C <sup>4</sup> C <sup>3</sup> , C <sup>2</sup> C <sup>1</sup> C <sup>0</sup> |

| 110,100 | 111,000 | 010,100 | 011,000 | 100,000       | 101,010 | 110,000 | 111,010 |                                                                                             |

| 100,111 | 101,011 | 000,111 | 001,011 | 000,101       | 001,111 | 010,101 | 011,111 |                                                                                             |

| 100,100 | 101,000 | 000,100 | 001,000 | 000,000       | 001,010 | 010,000 | 011,010 |                                                                                             |

| 010,011 | 011,001 | 000,011 | 001,001 | 000,001       | 001,101 | 100,001 | 101,101 | > !                                                                                         |

| 010,110 | 011,100 | 000,110 | 001,100 | 000,010       | 001,110 | 100,010 | 101,110 |                                                                                             |

| 110,011 | 111,001 | 100,011 | 101,001 | 010,001       | 011,101 | 110,001 | 111,101 |                                                                                             |

| 110,110 | 111,100 | 100,110 | 101,100 | 010,010       | 011,110 | 110,010 | 111,110 | T090357                                                                                     |

Fig. 2.12 64-QAM constellation [ITU J.83]

|       |       |       |       |       |       |       | (     | 2<br>• |       |       |       |       |       |       |       | C7C6C<br>C3C2C |

|-------|-------|-------|-------|-------|-------|-------|-------|--------|-------|-------|-------|-------|-------|-------|-------|----------------|

| 1110, | 1111, | 1110, | 1111, | 1110, | 1111, | 1110, | 1111, | 0000,  | 0011, | 0100, | 0111, | 1000, | 1011, | 1100, | 1111, | 0.020          |

| 1111  | 1101  | 1011  | 1001  | 0111  | 0101  | 0011  | 0001  | 1111   | 1111  | 1111  | 1111  | 1111  | 1111  | 1111  | 1111  |                |

| 1100, | 1101, | 1100, | 1101, | 1100, | 1101, | 1100, | 1101, | 0000,  | 0011, | 0100, | 0111, | 1000, | 1011, | 1100, | 1111, |                |

| 1110  | 1100  | 1010  | 1000  | 0110  | 0100  | 0010  | 0000  | 1100   | 1100  | 1100  | 1100  | 1100  | 1100  | 1100  | 1100  |                |

| 1010, | 1011, | 1010, | 1011, | 1010, | 1011, | 1010, | 1011, | 0000,  | 0011, | 0100, | 0111, | 1000, | 1011, | 1100, | 1111, |                |

| 1111  | 1101  | 1011  | 1001  | 0111  | 0101  | 0011  | 0001  | 1011   | 1011  | 1011  | 1011  | 1011  | 1011  | 1011  | 1011  |                |

| 1000, | 1001, | 1000, | 1001, | 1000, | 1001, | 1000, | 1001, | 0000,  | 0011, | 0100, | 0111, | 1000, | 1011, | 1100, | 1111, |                |

| 1110  | 1100  | 1010  | 1000  | 0110  | 0100  | 0010  | 0000  | 1000   | 1000  | 1000  | 1000  | 1000  | 1000  | 1000  | 1000  |                |

| 0110, | 0111, | 0110, | 0111, | 0110, | 0111, | 0110, | 0111, | 0000,  | 0011, | 0100, | 0111, | 1000, | 1011, | 1100, | 1111, |                |

| 1111  | 1101  | 1011  | 1001  | 0111  | 0101  | 0011  | 0001  | 0111   | 0111  | 0111  | 0111  | 0111  | 0111  | 0111  | 0111  |                |

| 0100, | 0101, | 0100, | 0101, | 0100, | 0101, | 0100, | 0101, | 0000,  | 0011, | 0100, | 0111, | 1000, | 1011, | 1100, | 1111, |                |

| 1110  | 1100  | 1010  | 1000  | 0110  | 0100  | 0010  | 0000  | 0100   | 0100  | 0100  | 0100  | 0100  | 0100  | 0100  | 0100  |                |

| 0010, | 0011, | 0010, | 0011, | 0010, | 0011, | 0010, | 0011, | 0000,  | 0011, | 0100, | 0111, | 1000, | 1011, | 1100, | 1111, |                |

| 1111  | 1101  | 1011  | 1001  | 0111  | 0101  | 0011  | 0001  | 0011   | 0011  | 0011  | 0011  | 0011  | 0011  | 0011  | 0011  |                |

| 0000, | 0001, | 0000, | 0001, | 0000, | 0001, | 0000, | 0001, | 0000,  | 0011, | 0100, | 0111, | 1000, | 1011, | 1100, | 1111, | <b>→</b> 1     |

| 1110  | 1100  | 1010  | 1000  | 0110  | 0100  | 0010  | 0000  | 0000   | 0000  | 0000  | 0000  | 0000  | 0000  | 0000  | 0000  |                |

| 1110, | 1101, | 1010, | 1001, | 0110, | 0101, | 0010, | 0001, | 0000,  | 0001, | 0000, | 0001, | 0000, | 0001, | 0000, | 0001, |                |

| 0001  | 0001  | 0001  | 0001  | 0001  | 0001  | 0001  | 0001  | 0001   | 0011  | 0101  | 0111  | 1001  | 1011  | 1101  | 1111  |                |

| 1110, | 1101, | 1010, | 1001, | 0110, | 0101, | 0010, | 0001, | 0010,  | 0011, | 0010, | 0011, | 0010, | 0011, | 0010, | 0011, |                |

| 0010  | 0010  | 0010  | 0010  | 0010  | 0010  | 0010  | 0010  | 0000   | 0010  | 0100  | 0110  | 1000  | 1010  | 1100  | 1110  |                |

| 1110, | 1101, | 1010, | 1001, | 0110, | 0101, | 0010, | 0001, | 0100,  | 0101, | 0100, | 0101, | 0100, | 0101, | 0100, | 0101, |                |

| 0101  | 0101  | 0101  | 0101  | 0101  | 0101  | 0101  | 0101  | 0001   | 0011  | 0101  | 0111  | 1001  | 1011  | 1101  | 1111  |                |

| 1110, | 1101, | 1010, | 1001, | 0110, | 0101, | 0010, | 0001, | 0110,  | 0111, | 0110, | 0111, | 0110, | 0111, | 0110, | 0111, |                |

| 0110  | 0110  | 0110  | 0110  | 0110  | 0110  | 0110  | 0110  | 0000   | 0010  | 0100  | 0110  | 1000  | 1010  | 1100  | 1110  |                |

| 1110, | 1101, | 1010, | 1001, | 0110, | 0101, | 0010, | 0001, | 1000,  | 1001, | 1000, | 1001, | 1000, | 1001, | 1000, | 1001, |                |

| 1001  | 1001  | 1001  | 1001  | 1001  | 1001  | 1001  | 1001  | 0001   | 0011  | 0101  | 0111  | 1001  | 1011  | 1101  | 1111  |                |

| 1110, | 1101, | 1010, | 1001, | 0110, | 0101, | 0010, | 0001, | 1010,  | 1011, | 1010, | 1011, | 1010, | 1011, | 1010, | 1011, |                |

| 1010  | 1010  | 1010  | 1010  | 1010  | 1010  | 1010  | 1010  | 0000   | 0010  | 0100  | 0110  | 1000  | 1010  | 1100  | 1110  |                |

| 1110, | 1101, | 1010, | 1001, | 0110, | 0101, | 0010, | 0001, | 1100,  | 1101, | 1100, | 1101, | 1100, | 1101, | 1100, | 1101, |                |

| 1101  | 1101  | 1101  | 1101  | 1101  | 1101  | 1101  | 1101  | 0001   | 0011  | 0101  | 0111  | 1001  | 1011  | 1101  | 1111  |                |

| 1110, | 1101, | 1010, | 1001, | 0110, | 0101, | 0010, | 0001, | 1110,  | 1111, | 1110, | 1111, | 1110, | 1111, | 1110, | 1111, |                |

| 1110  | 1110  | 1110  | 1110  | 1110  | 1110  | 1110  | 1110  | 0000   | 0010  | 0100  | 0110  | 1000  | 1010  | 1100  | 1110  |                |

Fig. 2.13 256-QAM constellation [ITU J.83]

### 2.5 Modulation and demodulation

## 2.5.1 QAM characteristics

The cable transmission format is summarized in Table 2.3 for 64-QAM and 256-QAM and Table 2.4 contains a summary of the pertinent characteristics of the variable interleaving modes [ITU J.83].

| Parameter                    | 64-QAM format                                                              | 256-QAM format                                              |  |  |

|------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------|--|--|

| Modulation                   | 64-QAM, rotationally invariant coding                                      | 256-QAM, rotationally invariant coding                      |  |  |

| Symbol size                  | 3 bits for "I" and 3 bits for "Q"<br>dimensions                            | 4 bits for "I" and 4 bits for "Q"<br>dimensions             |  |  |

| Transmission band            | 54 to 860 MHz                                                              | 54 to 860 MHz                                               |  |  |

| Channel spacing              | 6 MHz                                                                      | 6 MHz                                                       |  |  |

| Symbol rate                  | 5.056941 Msps ± 5 ppm                                                      | 5.360537 Msps ± 5 ppm                                       |  |  |

| Information bit rate         | 26.97035 Mbps ± 5 ppm                                                      | 38.81070 Mbps $\pm$ 5 ppm                                   |  |  |

| Frequency response           | Square root raised cosine filter<br>(Roll-off ≈ 0.18)                      | Square root raised cosine filter (Roll-off $\approx 0.12$ ) |  |  |

| FEC framing                  | 42-bit sync trailer following 60 RS<br>blocks                              | 40-bit sync trailer following 88 RS<br>blocks               |  |  |

| QAM constellation<br>mapping | 6 bits per symbol                                                          | 8 bits per symbol                                           |  |  |

| NOTE – These values are      | e specific to 6 MHz channel spacing. Ad<br>channel spacing are under study |                                                             |  |  |

| Table 2.3 Cable transmission format | [ITU I 83] |

|-------------------------------------|------------|

| Table 2.5 Cable transmission format | 110 5.05   |

|              | Level 1                              | Level 2                                                               |

|--------------|--------------------------------------|-----------------------------------------------------------------------|

| QAM format   | 64-QAM (see Table 2.3)               | 64- or 256-QAM<br>(see Table 2.3)                                     |

| Interleaving | Fixed interleaving $I = 128$ $J = 1$ | Variable interleaving I =<br>128,64,32,16,8<br>J = 1,2,3,4,5,6,7,8,16 |

Table 2.4 Variable interleaving modes [ITU J.83]

# **Chapter 3** Low Power Design

#### 3.1 Introduction

In this chapter, sources of the power consumption for FPGA are examined based on the existing research work [Shang02, Kusse98] and the existing low power design techniques [Chandrakasan95], and their applicability to the low power FPGA design is investigated. Finally, the low power design strategy for the digital modulator is derived.

#### **3.2** Sources of power consumption

First, the power dissipation of the Xilinx Virtex II is discussed by reviewing Shang's recent work [Shang02]. Good understanding of the sources of the power consumption in FPGA is fundamental for the low power FPGA design and it will guide us in the right direction to develop the effective methods for low-power FPGA design.

Before presenting Shang's research results, we first briefly introduce the architecture of Xilinx Virtex chip. The detailed information can be found in Virtex datasheet [Xilinx00]. Virtex FPGA consists of two major types of resources: configurable logic blocks (CLB), and routing resources. CLBs are the computational elements or logic parts of the FPGA, and they are connected by the routing resources. The routing resources include three

types of wires (long lines, hex lines and double lines) and the switches. The long lines can distribute the signals across the device in two directions: vertical and horizontal; the hex lines route signals to every third or sixth CLB blocks in all four directions; the double lines route signals to every first or second CLB block in all four directions [Xilinx00]. The switches connect the CLB's inputs and outputs to these lines and are referred to as the input crossbar and the output crossbar [Shang02]. Also, there are some dedicated global routing resources for the global clock distribution, local routing resources for the carry propagation and the local clock, and direct connect lines.

In the digital CMOS circuits, two types of power consumption, static and dynamic power consumption, exist. Since the design of low power FPGA devices is beyond the research scope of this thesis, only the dynamic power consumption is considered. The dynamic power consumption in the digital CMOS circuits results from charging and discharging the capacitances and can be modeled as [Rabaey02]:

$$P_{dynamic} = \alpha_{0 \to 1} C_L V_{dd} V_{swing} f_{clk}$$

(3.1)

Where  $C_L$  is the capacitance,  $V_{swing}$  is the voltage swing,  $f_{clk}$  is the clock frequency and  $\alpha_{0->1}$  is the switching factor. [Shang02] broke down the sources of the dynamic power dissipation and calculated the corresponding capacitance for each resource. Due to his privileged access to the FPGA schematic, he obtained the results on the transistor level by simulation and confirmed these results by measurements. His results of the effective capacitance of each resource are shown in the Table 3.1.

| Туре             | Resource of Virtex II | Capacitance (PF)   |

|------------------|-----------------------|--------------------|

|                  | IXbar                 | 9.44               |

| Interconnect     | OXbar                 | 5.12               |

| Per CLB          | Double                | 13.20              |

| I EI CLD         | Hex                   | 18.40              |

|                  | Long(*)               | <mark>26.10</mark> |

| Logia            | LUT inputs            | 26.40              |

| Logic<br>Per CLB | FF inputs             | 2.88               |

| rei CLD          | Carray                | 2.68               |

| Clocking         | Global wiring(*)      | <mark>300</mark>   |

| Clocking         | Local                 | 0.72               |

Table 3.1 Capacitance of the resources of Virtex II (2v1000FG256-5) [Shang02]

\* the value may change with the types of the device

Two conclusions can be drawn from the above table. First, the capacitance of the interconnection is comparable to that of the computational element in a CLB. Second, the capacitance of the interconnect line is not proportional to its length. The capacitance of a double line, which extends between two CLB blocks, is almost half of the capacitance of the long line, which goes across the whole chip, in device 2v1000FG256-5; and the capacitance of a double line is close to that of the hex line, which spans six CLB blocks. For the small devices, the long line capacitance of the long line capacitance between the capacitance of the lines.

It is also reported in [Shang02] that 60% of power is dissipated in the interconnection by experiments with a set of typical designs. Clocking and logic resources consume 14% and 16% of the total power separately. Another important factor that impacts the dynamic

power consumption is the switch factor [Shang02]. Actually, the dynamic or switching power consumption of all these resources varies significantly with the switching activities. As in the VLSI, the clock distribution network is also a primary component of power dissipation.

## 3.3 Low power design techniques

Existing low power design techniques at two levels used in VLSI are explored and their effectiveness in low power FPGA design is examined in this section based on distribution of dynamic power dissipation in FPGA. The logic level design optimization of FPGA is performed during the synthesis, mapping and placing processes, which is done by Computer Aided Design (CAD) tools, and circuits level design involves the design of the FPGA device itself, so only the algorithmic and architectural levels optimization for low power are discussed in this section.

#### **3.3.1** Algorithm level optimization

The most effective method for low power is performing optimization at the algorithm level. At the algorithm level, the optimization may involve performing algorithm modification, selecting new arithmetic operation or applying transformation described in [Chandrakasan95]. For instance, converting the complex arithmetic operations such as

multiplication and division to simple actions like addition and shifting can reduce the area many times as compared to typical implementation [Starzyk04].

This reduction in area results in the decrease of the effective capacitance, and thus the low power goal is achieved. Another way of reducing power through algorithmic modification is exploiting the advantages of constant values in arithmetic operations [Chandrakasan95]. This low power design technique is used in the design of Reed Solomon (RS) encoder. The finite field multiplication is the bottleneck of the high performance RS encoder. The fixed coefficient not only makes the pipelining of the design possible, but also minimizes the total number of the partial products in the new proposed structure.

Exploiting algorithm parallelism is an effective way in low power design for VLSI [Chandrakasan95]. Parallelizing the design to low power works in VLSI due to the power supply's quadratic impact on the power consumption. However, since the FPGA device is given before the design and the power supply is fixed, then the power supply reduction to low the power consumption is not applicable to FPGA design [Kusse98]. Yet, by properly exploring the concurrency in the data path on the algorithm level, the amount of the logic CLBs resources and interconnections may be reduced. This results from the logic combination by the LUT since each LUT can accommodate any four-input function. The optimum number of replications can be found by exploring the area power product in the design space. The example of this exploration is presented, in the design of message

checksum block of the digital modulator, where concurrency of the algorithm can be revealed by unfolding technique. Parallelizing the design speeds up the design, and the reduction of the area due to logic combination and less interconnection load may lower the power dissipation.

In addition, the algorithm can be reformulated to simplify the control structure and to reduce the amount of the interconnection, which is the dominating factor of the power dissipation in FPGA. This style is suitable for the low power FPGA design. The design example of such algorithm reformulation is presented in the interleaver design.

#### **3.3.2** Architectural level optimization

Techniques of optimizing architecture for low power are examined in this section. In VLSI, parallel architectures can be employed to speed up the design. This creates an opportunity to slow down processing in each parallel block by reducing the supply voltage and thus saving the power. This effective approach results from the power's quadratic dependence on the supply voltage. As discussed in the algorithm level optimization section, the design space can be explored to obtain the optimum number of replications. Combining logic blocks by introducing parallelism on the architectural level reduces total effective capacitance improving the overall performance. At some optimum

number of replication, the total effective capacitance decreases when the logic reduction due to logic combination by LUT dominates.

Pipelining the architecture used successfully in low power VLSI is also suitable for the low power design in FPGA. The increase in effective capacitance introduced by pipeline registers is merely 11% percent. This is because each output of the CLB has an optional registered output and the effective capacitance of this flip-flop is approximately 11% percent of the total logic capacitance, according to the effective capacitance in Shang's table (Table 3.1). The data transfer frequency however can be reduced by a much higher factor and this results in a significant power savings. In addition, the pipelining has the lower area cost advantage over parallelizing. Therefore, the pipelined design is an effective low power design technique for FPGA

Another category for low power design in VLSI at the architectural level is minimizing the switching activities by choosing a proper binary number representation, for instance, switching 2's complement to sign-magnitude representation when the probability of data changing around zero is high [Chandrakasan95]. In addition, resynchronizations can be used to balance the signal paths to minimize the glitching activity [Chandrakasan95]. Due to the similar reasons, all these are suitable to low power FPGA design.

#### **3.4** Low power design strategy for the digital modulator

Considering the application characteristics specifies the low power design strategy. Maintaining a given level of throughput is a common design concept in signal processing and other dedicated applications, in which there is no advantage in performing computing faster than some given rate, since the hardware will simply have to wait until further processing is required [Chandrakasan95]. However, scaling down the power supply voltage used in VLSI to slow down data transfer rate is not applicable to the low power FPGA design. Thus, the low power design strategy for the digital modulator targeted on FPGA is accomplished by slowing down the clock frequency, as well as minimizing the effective switching capacitances by design optimization at the algorithm and architectural levels.

## **Chapter 4** Low Power Design of Digital Modulator

## 4.1 Introduction

In this chapter, the low power design techniques are applied to the design of the several key modules including Reed Solomon Encoder, interleaver, TCM modulator and MPEG framer.

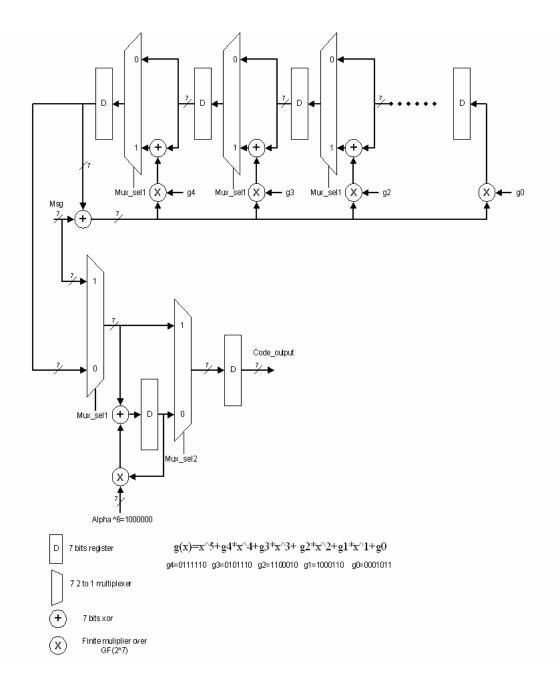

## 4.2 Reed Solomon encoder

The implementation of extended Reed Solomon (RS) encoder is discussed in this section. A systematic (128,122) encoder over GF(2^7) is used in the modulator. Its generator polynomial is  $g(x)=x^5+g4*x^4+g3*x^3+g2*x^2+g1*x^1+g0$ , where g4=alpha^52, g3=alpha^116, g2=alpha^119, g1=alpha^61 and g0=alpha^15, where alpha is the root of the primitive polynomial p(x), i.e. p(alpha)=0. The primitive polynomial  $p(x)=x^7+x^3+1$  generates all elements of GF(2^7).

The straightforward method to implement this Reed Solomon encoder uses a feed back network with finite field arithmetic operations. The block diagram of the encoder is shown in Fig. 4.1. Two types of operations are involved - one is addition, which is simply XOR operation using the standard basis to represent the finite field elements; another one is multiplication, implemented by the finite field multiplier. The multiplier is the key element and has a great impact on the performance of the RS encoder. The first parity symbols in a systematic Reed-Solomon codeword are given by the remainder of  $m(x) \cdot x^5 \mod g(x)$ . The extended parity symbol  $c_{128}$  is generated by evaluating the code word at the sixth power of  $\alpha$  [ITU J.83]. So when mux\_sel1=1, the first five parity symbols are generated; when mux\_sel1=0, they are shifted out and at the same time the extended parity symbols are calculated. Finally, the extended parity symbols are transmitted when mulx\_sel2=0.

Fig. 4.1 Block diagram for the extended RS Solomon encoder

A number of architectures of this finite field multiplier were available [Berlekamp82] [Massey86, Jain98, Mastrovito91 and Sunar99]. Berlekamp and Massey-ommru bit serial multiplier, Mastrotio bit parallel and semi-systolic array multipliers are the four major types of architectures. Bit serial structure is too slow for this design, though it has the area advantage over parallel structure. Bit parallel structure has higher performance, and thus lowers the speed requirement to lower the power. Two recently proposed parallel structures are investigated, and a new structure based on the fixed coefficient is proposed as follows.

First, Jain's parallel array-type multiplier is considered. Any nonzero elements in the finite field can be represented in two forms, the exponential form and the polynomial form. Using the polynomial representation based on the standard basis, the finite filed multiplication involves two types of operations, one is a polynomial multiplication and another is a modulo operation. In this structure, the multiplication and the modulo operation are executed alternatively. The algorithm and its implementation in the VLSI are discussed in Sunar's paper [Sunar99]. The notation in this part is adopted from Jain's paper [Jain98].

Let  $C = AB \mod p(x)$ , where  $A, B, C \in GF(2^m)$  and p(x) is a primitive polynomial over  $GF(2^m)$ . The polynomial representation is used, so

$$A = a_{m-1}\alpha^{m-1} + a_{m-2}\alpha^{m-2} + \dots + a_1\alpha^1 + a_0$$

(4.1)

$$B = b_{m-1}\alpha^{m-1} + b_{m-2}\alpha^{m-2} + \dots + b_1\alpha^1 + b_0$$

(4.2)

$$C = c_{m-1}\alpha^{m-1} + c_{m-2}\alpha^{m-2} + \dots + c_1\alpha^1 + c_0$$

(4.3)

$$p(x) = \alpha^{m} + p_{m-1}\alpha^{m-1} + p_{m-2}\alpha^{m-2} + \dots + p_{1}\alpha^{1} + p_{0}$$

(4.4)

Then,  $C = b_{m-1}[A\alpha^{m-1} \mod p(x)] + \dots + b_2[A\alpha^2 \mod p(x)] + b_1[A\alpha \mod p(x)] + b_0A$

We define

$$A^{(k)} = A\alpha^k \mod p(x) = a_{m-1}^{(k)}\alpha^{m-1} + a_{m-2}^{(k)}\alpha^{m-2} + \dots + a_1^{(k)}\alpha^1 + a_0^{(k)}$$

, then

$A^{(k)} = A^{(k-1)} a \mod p(x)$ . Also define  $C^{(k)} = A^{(k-1)} b_{k-1} + C^{(k-1)}$  with  $C^{(0)} = 0$ , then the final results of the multiplication is  $C^{(m)}$ . The algorithm developed by Jain can be described as the follows:

1) At the first m-1 steps (step 0 to step m-2),  $A^{(k)}$  and  $C^{(k)}$  are computed, where k changes from 1 to m-1

$$a_{i}^{(k)} = \begin{cases} a_{i-1}^{(k-1)} + a_{m-1}^{k-1} p_{i}, 1 \le i \le m-1 \\ a_{m-1}^{k-1} p_{i}, & i = 0 \end{cases}$$

(4.5)

$$c_i^{(k)} = a_i^{(k-1)} b_{k-1} + c_i^{(k-1)}$$

(4.6)

2) At step m-1, the final result  $C^{(m)}$  of the multiplication is obtained with

$$c_i^{(m)} = a_i^{(m-1)} b_{m-1} + c_i^{(m-1)}$$

(4.7)

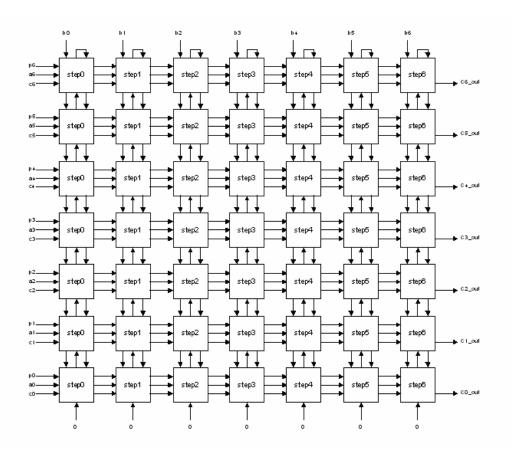

As is shown in Fig 4.2, the block diagram of the multiplier over  $GF(2^7)$  is derived from the above algorithm for this RS encoder design. The square block implements equations (4.5) and (4.6), the inputs p6 to p0, b6 to b0, and a6 to a0 are the coefficients of p(x), B and A respectively. The final results c6\_out to c0\_out were obtained at the output of the final stage blocks (step6) as shown in Fig. 4.2.

Fig. 4.2 Block diagram of the array multiplier over GF (2^7)

Although the pipelining of this array multiplier can improve the performance by a factor of m, for GF (2<sup>m</sup>), the feed back network in RS encoder make pipelining very difficult. In addition, pipelining of this structure requires fixed multiplicand B. I implemented this architecture to compare with the approach developed in this thesis. As demonstrated in next section, this new proposed approach yields smaller area and lower power dissipation.

The proposed structure is very similar to the one described by Mastrovito [Mastrovito91]. However, the proposed multiplier has a significant advantage over Mastrovito's design, namely it is not limited to trinomial. Both the Mastrovito's and the new proposed multiplier are fully parallel structures. In both of them, two fundamental operations, multiplication and modulo operation, are performed separately. The Mastrovito's multiplier can be used only in case when the primitive polynomial is  $x^m+x^{1+1}$ . Sunar extended the Mastrovito's multiplier to the all trinomials and we refer to it as the modified Mastrovito's multiplier. Fortunately, the modified Mastrovito's multiplier can be used for the primitive polynomial in our design, since  $p(x) = x^7+x^3+1$  is a trinomial.

In what follows, I describe the theory and the basic operation of Sunar's multiplier, which is commonly used in error correction processing. For the multiplier over GF(2<sup>m</sup>), this method constructs the multiplication matrix by pre-calculating higher order elements  $x^m, x^{m+1}, ..., x^{2m-2}$  modulo p(x) using several equations. The notation in this part is adopted from [Sunar99].

Let  $C = AB \mod p(x)$ , where  $A, B, C \in GF(2^m)$  and p(x) is a primitive polynomial over  $GF(2^m)$ . The polynomial representation is used, so

$$A = a_{m-1}\alpha^{m-1} + a_{m-2}\alpha^{m-2} + \dots + a_1\alpha^1 + a_0$$

(4.7)

$$B = b_{m-1}\alpha^{m-1} + b_{m-2}\alpha^{m-2} + \dots + b_1\alpha^1 + b_0$$

(4.8)

$$C = c_{m-1}\alpha^{m-1} + c_{m-2}\alpha^{m-2} + \dots + c_1\alpha^1 + c_0$$

(4.9)

$$p(x) = \alpha^{m} + p_{m-1}\alpha^{m-1} + p_{m-2}\alpha^{m-2} + \dots + p_{1}\alpha^{1} + p_{0}$$

(4.10)

The multiplication matrix Z will be constructed in terms of the coefficients of A and the procedure for the construction is shown as follows.

$$\begin{bmatrix} c_{0} \\ c_{1} \\ c_{2} \\ \vdots \\ c_{m-2} \\ c_{m-1} \end{bmatrix} = \begin{bmatrix} z_{0} & 0 & 0 & 0 & \cdots & 0 \\ z_{1} & z_{0} & 0 & 0 & \cdots & 0 \\ z_{2} & z_{1} & z_{0} & 0 & \ddots & \vdots \\ \vdots & \vdots & \vdots & z_{0} & 0 & \vdots \\ z_{m-2} & z_{m-3} & z_{m-4} & \cdots & z_{0} & 0 \\ z_{m-1} & z_{m-2} & z_{m-3} & z_{m-4} & \cdots & z_{0} \end{bmatrix} \begin{bmatrix} b_{0} \\ b_{1} \\ b_{2} \\ \vdots \\ b_{m-2} \\ b_{m-1} \end{bmatrix}$$

(4.11)

The matrix Z equals to X+Y,

nd

$$X = \begin{bmatrix} a_{0} & 0 & 0 & 0 & \cdots & 0 \\ a_{1} & a_{0} & 0 & 0 & \cdots & 0 \\ a_{2} & a_{1} & a_{0} & 0 & \ddots & \vdots \\ \vdots & \vdots & \vdots & a_{0} & 0 & \vdots \\ a_{m-2} & a_{m-3} & a_{m-4} & \cdots & a_{0} & 0 \\ a_{m-1} & a_{m-2} & a_{m-3} & a_{m-4} & \cdots & a_{0} \end{bmatrix}$$

(4.12)

A

$Y = \sum_{i=0}^{k-1} T\left[\uparrow i(m-n)\right] + \sum_{i=0}^{k-1} U\left[\to i(m-n)\right], \text{ where } T\left[\uparrow k\right] \text{ represents the matrix shift up by k}$

rows and  $T[\rightarrow k]$  shift left by k columns,  $k = \left\lfloor \frac{m-2}{m-n} \right\rfloor + 1$ , and the matrixes T and U are

$$\mathbf{T} = \begin{bmatrix} 0 & a_{m-1} & a_{m-2} & a_{m-3} & \cdots & a_1 \\ 0 & 0 & a_{m-1} & a_{m-2} & \cdots & a_2 \\ 0 & 0 & 0 & a_{m-1} & \ddots & \vdots \\ \vdots & \vdots & \vdots & 0 & a_{m-1} & \vdots \\ 0 & 0 & 0 & \cdots & 0 & a_{m-1} \\ 0 & 0 & 0 & 0 & \cdots & 0 \end{bmatrix}$$

(4.13)

$$\mathbf{U} = \begin{bmatrix} 0 & 0 & 0 & 0 & 0 & 0 \\ \vdots & \vdots & \ddots & \ddots & \cdots & \vdots \\ 0 & 0 & 0 & 0 & \cdots & 0 \\ 0 & a_{m-1} & a_{m-2} & \cdots & a_2 & a_1 \\ \vdots & \vdots & \vdots & \cdots & a_3 & a_2 \\ 0 & 0 & a_{m-4} & \cdots & \vdots & 0 \\ 0 & 0 & \cdots & a_{m-1} & \cdots & a_{m-n} \end{bmatrix}$$

(4.14)

For the derivation of the above results, please refer to the paper [Sunar99].

The multiplication matrix of the modified Mastrivito's multiplier over GF (2^7) for the primitive polynomial  $x^7+x^3+1$  is derived as follows.

In this encoder, m=7 and n=3. Then k=2 and

$$Y = \sum_{i=0}^{k-1} T\left[\uparrow i(m-n)\right] + \sum_{i=0}^{k-1} U\left[\to i(m-n)\right]$$

=  $\sum_{i=0}^{1} T\left[\uparrow i(7-3)\right] + \sum_{i=0}^{1} U\left[\to i(7-3)\right]$  (4.15)

where

$$T = \begin{bmatrix} 0 & a6 & a5 & a4 & a3 & a2 & a1 \\ 0 & 0 & a6 & a5 & a4 & a3 & a2 \\ 0 & 0 & 0 & a6 & a5 & a4 & a3 \\ 0 & 0 & 0 & 0 & a6 & a5 & a4 \\ 0 & 0 & 0 & 0 & 0 & a6 & a5 \\ 0 & 0 & 0 & 0 & 0 & 0 & a6 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 \end{bmatrix}$$

(4.16)

$$Y=T+T[\uparrow 4]+U+U[\rightarrow 4] = \begin{bmatrix} 0 & a6 & a5 & a4 & a3 & a2+a6 & a1+a5 \\ 0 & 0 & a6 & a5 & a4 & a3 & a2+a6 \\ 0 & 0 & 0 & a6 & a5 & a4 & a3 \\ 0 & a6 & a5 & a4 & a6+a3 & a5+a6+a2 & a4+a5+a1 \\ 0 & 0 & a6 & a5 & a4 & a6+a3 & a5+a6+a2 \\ 0 & 0 & 0 & a6 & a5 & a4 & a6+a3 \\ 0 & 0 & 0 & a6 & a5 & a4 & a6+a3 \\ 0 & 0 & 0 & 0 & a6 & a5 & a4 \end{bmatrix}$$

Finally Z=X+Y

|   | a0           | <i>a</i> 6 | <i>a</i> 5  | <i>a</i> 4 | <i>a</i> 3 | a2 + a6                | a1+a5                  |        |

|---|--------------|------------|-------------|------------|------------|------------------------|------------------------|--------|

|   | <i>a</i> 1   | <i>a</i> 0 | <i>a</i> 6  | a5         | <i>a</i> 4 | <i>a</i> 3             | <i>a</i> 2+ <i>a</i> 6 |        |

|   | <i>a</i> 2   | <i>a</i> 1 | <i>a</i> 0  | <i>a</i> 6 | a5         | <i>a</i> 4             | <i>a</i> 3             |        |

| = | <i>a</i> 3   | a2 + a6    | a1 + a5     | a0 + a4    | a6 + a3    | a5 + a6 + a2           | a4 + a5 + a1           | (4.20) |

|   | <i>a</i> 4   | <i>a</i> 3 | $a^2 + a^6$ | a1 + a5    | a0 + a4    | a6 + a3                | a5 + a6 + a2           |        |

|   | <i>a</i> 5   | <i>a</i> 4 | <i>a</i> 3  | a2 + a6    | a1 + a5    | <i>a</i> 0+ <i>a</i> 4 | <i>a</i> 6+ <i>a</i> 3 |        |

|   | _ <i>a</i> 6 | a5         | <i>a</i> 4  | <i>a</i> 3 | a2 + a6    | a1 + a5                | a0+a4                  |        |

For the constant coefficient in the RS encoder, we pre-calculate these matrixes and the design example of g4=alpha^52 in the generator polynomial is  $g4 = \alpha^5 + \alpha^4 + \alpha^3 + \alpha^2 + \alpha^1$ .i.e a6=a0=0, all others are 1. The multiplication matrix

|    | 0 | 0 | 1 | 1 | 1 | 1 | 0<br>1<br>1<br>1<br>0<br>1<br>1<br>1 |

|----|---|---|---|---|---|---|--------------------------------------|

|    | 1 | 0 | 0 | 1 | 1 | 1 | 1                                    |

|    | 1 | 1 | 0 | 0 | 1 | 1 | 1                                    |

| Z= | 1 | 1 | 0 | 1 | 1 | 0 | 1                                    |

|    | 1 | 1 | 1 | 0 | 1 | 1 | 0                                    |

|    | 1 | 1 | 1 | 1 | 0 | 1 | 1                                    |

|    | 0 | 1 | 1 | 1 | 1 | 0 | 1                                    |

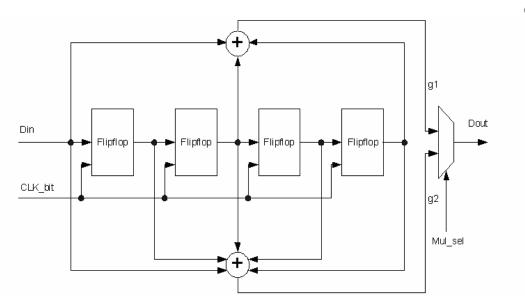

Then, the diagram of the multiplier over  $GF(2^7)$  can be derived from the matrix shown in Fig. 4.3

|   | 0  | b0 | b0 | b0 | b0 | b0 | 0  |

|---|----|----|----|----|----|----|----|

|   | b1 | b1 | b1 | b1 | b1 | 0  | 0  |

|   | b2 | b2 | b2 | 0  | 0  | 0  | b2 |

|   | b3 | b3 | 0  | b3 | 0  | b3 | b3 |

|   | b4 | 0  | b4 | b4 | b4 | b4 | b4 |

|   | 0  | b5 | b5 | 0  | b5 | b5 | b5 |

| + | b6 | b6 | 0  | b6 | b6 | b6 | 0  |

|   | c6 | c5 | c4 | c3 | c2 | c1 | c0 |

Fig. 4.3 Block diagram of the multiplier (C=A\*alpha^52) over GF(2^7)

The bottleneck for speeding up the GF multiplier is always the modulo operation. Here, I propose a new version of this algorithm that reduces the number of the partial product and addition operations to speed up the design. In this proposed structure, we use both the polynomial and exponential representations instead of single polynomial or exponential terms. The key idea to simplify modulo operation is pre-computing, which takes advantage of the fixed coefficients. Let us consider  $C = AB \mod p(x)$ , where  $A, B, C \in GF(2^n)$  and p(x) is primitive polynomial over  $GF(2^n)$ . The polynomial representation is used for A and C, so

$$A = a_{m-1}\alpha^{m-1} + a_{m-2}\alpha^{m-2} + \dots + a_1\alpha^1 + a_0$$

(4.21)

$$C = c_{m-1}\alpha^{m-1} + c_{m-2}\alpha^{m-2} + \dots + c_1\alpha^1 + c_0$$

(4.22)

$$p(x) = \alpha^{m} + p_{m-1}\alpha^{m-1} + p_{m-2}\alpha^{m-2} + \dots + p_{1}\alpha^{1} + p_{0}$$

(4.23)

Since every none zero element in the GF(2<sup>m</sup>) can be represented as  $\alpha^k$ , where  $k = 0, 1, 2, ..., 2^m - 1$ , and assuming that the fixed coefficient B is  $\alpha^k$ , then  $AB = a_{m-1}\alpha^{m-1+k} + a_{m-2}\alpha^{m-2+k} + ... + a_1\alpha^{1+k} + a_0\alpha^k$ .

We first calculate  $\alpha^{k+j} \mod p(x)$ , where j = 0,1,2...m-1:

Assume

$$(\alpha^{k+j} \mod p(x)) = r_{m-1}^{j} \alpha^{m-1} + r_{m-2}^{j} \alpha^{m-2} + \dots + r_{1}^{j} \alpha^{1} + r_{0}^{j}$$

so  $C = AB \mod p(x) = \sum_{i=0}^{m-1} \sum_{j=0}^{m-1} a_i r_i^j \alpha^i$ , and the hardware structure can be derived from this

equation.

The design example of the multiplier with B equal to alpha^52 is shown as follows.

The coefficients of  $\alpha^{52+j} \mod p(x)$ , where j=0,1,...6, is shown as the following matrix,

|    | 0 | 1 | 1 | 1 | 1 | 1                     | 0 |  |

|----|---|---|---|---|---|-----------------------|---|--|

|    | 1 | 1 | 1 | 1 | 1 | 0                     | 0 |  |

|    | 1 | 1 | 1 | 0 | 0 | 0                     | 1 |  |

| R= | 1 | 1 | 0 | 1 | 0 | 1<br>0<br>1<br>1<br>1 | 1 |  |

|    | 1 | 0 | 1 | 1 | 1 | 1                     | 1 |  |

|    | 0 | 1 | 1 | 0 | 1 | 1                     | 1 |  |

|    | 1 | 1 | 0 | 1 | 1 | 1                     | 0 |  |

The hardware structure derived from the above result is similar to the modified Mastrovito multiplier shown in Fig. 4.3. The tree structure [Chandrakasan95] can be used to compute the individual column, if the number of elements is larger than four, which is

referred to as the granularity of the LUT for Xilinx Virtex FPGA. Since all the inputs from A arrive at the same time, the tree structure effectively reduces the glitching activities by balancing the signal paths and reducing the logic depth [Chandrakasan95].

Comparing to the Mastrovito's multiplier, the computing complexity is of the same order: m for GF(2<sup>m</sup>). The proposed finite field multiplier takes advantage of the multiplication by a constant coefficient, while Mastrovito's multiplier is more general and both A and B are not limited to fixed values. On the other hand, the proposed structure is not limited to the trinomials, which is the limitation of the Mastrovito multiplier.