### **Global Positioning System Signal Acquisition and Tracking**

**Using Field Programmable Gate Arrays**

A Dissertation Presented to the Faculty of the Fritz J. and Dolores H. Russ College of Engineering and Technology Ohio University

> In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

> > by Abdulqadir A. Alaqeeli

> > > November, 2002

Copyright © 2002

Abdulqadir Alaqeeli

All rights reserved

### THIS DISSERTATION ENTITLED

### "Global Positioning System Signal Acquisition and Tracking Using Field Programmable Gate Arrays"

by Abdulqadir Alaqeeli

has been approved

for the School of Electrical Engineering and Computer Science and the Russ College of Engineering and Technology

Janusz Starzyk, Professor School of Electrical Engineering and Computer Science

> Dennis Irwin, Dean Fritz J. and Dolores H. Russ College of Engineering and Technology

### Acknowledgement

In the Name of Allah, the Most Beneficent, the Most Merciful. All praise and thanks to Allah, Lord of the universe and all that exists. Prayers and peace be upon His prophet Mohammed, the last messenger for all humankind.

First, I thank Allah for His infinite blesses. Allah blessed me with loving parents, brothers, sisters, relatives, and friends. Allah's guidance made the completion of this work possible.

I want to thank my parents for their love, education, support, encouragement, and prayers. Thanks goes to my wife and my daughter. Their support gave me spiritual strength in pursuing my ambition and staying in the United States. Thanks also goes to my brothers and sisters. Life has no taste to me without my parents and my family.

I would like to thank my advisor, Prof. Janusz Starzyk, for his constant patience, great assistance, and guidance during my Masters and Ph.D. degrees. Prof. Starzyk was an unusual advisor who helped me in the academic and the personal matters. His way of teaching and problem solving changed me from an ordinary student to a knowledge seeker.

Thanks goes to my other committee members, Dr. Frank van Graas, Dr. Jeffrey Dill, Dr. Michael Braasch, and Dr. Nicolai Pavel. This committee is a blessing from Allah. Their advice and support helped me in solving many problems during this work. I would like to say again "Thanks" for your precious time, valuable help and support. Special thanks goes to Prof. Frank van Graas who acted as a co-advisor for me during the last year. Thanks also goes to Dr. Maarten Uijt de Haag. His friendship, advice, and discussions were very helpful to me.

Dr. Ahmad Alsolaim, my dear friend, cannot be forgotten. He helped me in all of my courses. He was my main supporter during the difficult days. He was a real brother who has given me advices since I came to the US in 1995. "Thank you Ahmad" is not enough for such a close friend.

I am very thankful to all of my friends in the VLSI and the Software Radio research groups for their help, discussions, and advice. I especially thank Sanjeev Gunawardena, Jing Pang, and Zhu Zhen for their support. In addition to their helpful discussions, they provided me with useful Matlab codes and synthesizable VHDL codes.

I would like to thank my friends Dr. Saleh Aloteawi and Dr. Mohammed Alsharekh. Their friendship was helpful for me during my study. "Thank You" goes to my friends Hamad Albrethin, Abdulrahman Alsebail, Mazyad Almuhaileb, Saleh Alawirdy, Mohammed Altamimi, Hamed Alsharari and Ahmad Alahmadi.

Finally, I want to thank all friends who assisted me upon request and were very helpful in their suggestions.

# **Table of Contents**

| Acknowledgement                                                   | iii  |

|-------------------------------------------------------------------|------|

| Table of Contents                                                 | v    |

| List of Tables                                                    | ix   |

| List of Figures                                                   | x    |

| List of Abbreviations                                             | xiii |

| Chapter 1                                                         | 1    |

| Introduction                                                      | 1    |

| Chapter 2                                                         | 6    |

| Background                                                        | 6    |

| 2.1 Introduction                                                  | 6    |

| 2.2 Spread Spectrum and Code Division Multiple Access             | 6    |

| 2.3 Global Positioning System                                     |      |

| 2.4 GPS Signal Structure                                          |      |

| 2.5 GPS Receiver Architecture                                     | 10   |

| 2.5.1 Signal Tracking                                             |      |

| 2.5.2 Signal Acquisition                                          |      |

| 2.6 Block Processing                                              |      |

| 2.7 Advantages and Disadvantages of the Current Signal Processing | 19   |

| Chapter 3                                                         | 22   |

| Convolution Algorithms Using Real and Binary Transforms           | 22   |

| 3.1 Introduction                                                  |      |

| 3.2 Fermat Number Transform and Convolution                       |      |

|            |                                                                  | vi    |

|------------|------------------------------------------------------------------|-------|

| 3.2        | .1 Fermat Number Transform                                       | 23    |

| 3.2        | .2 Convolution using Fermat Number Transform                     | 24    |

| 3.3 Coi    | nvolution and Walsh Transform                                    | 27    |

| 3.3        | .1 Introduction                                                  | 27    |

| 3.3        | .2 Walsh Transform and PN Sequences                              | 27    |

| 3.3        | .3 Convolution Algorithm                                         | 29    |

| 3.3        | .4 Hardware Implementation                                       | 32    |

|            | 3.3.4.1 Permutation Generators                                   | 33    |

|            | 3.3.4.2 Walsh Transform                                          | 35    |

| 3.4 Im     | plementation of a Walsh-Based Convolver for a 1,023-bit PN Code  | 37    |

|            |                                                                  |       |

| Chapter 4. |                                                                  | 42    |

| Averaging  | Method for Block Processing                                      | 19    |

|            | troduction                                                       |       |

|            | eraging Correlator                                               |       |

|            | eraging Correlator with Zero-Padding                             |       |

|            | eraging Correlator with Modified C/A Code                        |       |

|            | aracteristics of Using the Modified-Code Averaging Correlation   |       |

|            | oposed Architecture for Block Processing Using the Modified-Code |       |

|            | ng Correlator                                                    |       |

| agi        |                                                                  | 07    |

| Chapter 5. |                                                                  | 60    |

| p          |                                                                  |       |

| FPGA Imp   | elementation of Acquisition and Tracking Processes               | 60    |

| 5.1 Int    | troduction                                                       | 60    |

| 5.2 GF     | S Block Processing Algorithm for Hardware Implementation         | 61    |

| 5.3 Re     | quired Components for the Implementation of the Averaging-Corre  | lator |

| GP         | S Block Processing                                               | 63    |

| 5.3        | .1 Numerically Controlled Oscillator (NCO)                       | 63    |

| 5.3        | .2 Carrier-Wipe-off                                              | 65    |

| 5.3        | .3 The Averager                                                  | 66    |

| 5.3        | .4 Fast Fourier Transform (FFT) and Its Inverse                  | 68    |

| 5.3.5       Local Code Component       69         5.3.6       Complex Multiplier       72         5.3.7       Peak Searcher       76         5.3.8       Carrier Phase Estimator       78         5.3.8.1       Simple Digital ATAN       79         5.3.8.2       Computing ATAN Function Using CORDIC       81         5.3.9       Time-Domain Serial Correlators       82         5.4       FPGA Implementation of GPS Block Processor       83         5.5       Overall Performance and Discussion of the Results       89         Chapter 6       93         Summary, Conclusion, and Recommendations       93         6.1       Summary       93         6.2       Conclusion       95         6.3       Recommendations       95         6.3       Recommendations       98         Appendix A       106       106         The Ballynuey FPGA Board       108         Matlab Codes       108         B.1       Walsh Hadamard Based Convolution with PN sequences       108         B.2       Approximation of ATAN Function       110         B.3       Averaging Correlation Method       112         B.4       Modified-Code Averaging Method |                                                        |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----|

| 5.3.7       Peak Searcher       76         5.3.8       Carrier Phase Estimator       78         5.3.8.1       Simple Digital ATAN       79         5.3.8.2       Computing ATAN Function Using CORDIC       81         5.3.9       Time-Domain Serial Correlators       82         5.4       FPGA Implementation of GPS Block Processor       83         5.5       Overall Performance and Discussion of the Results       89         Chapter 6       93         Summary, Conclusion, and Recommendations       93         6.1       Summary       93         6.2       Conclusion       95         6.3       Recommendations       95         6.3       Recommendations       95         References       98         Appendix A       106         The Ballynuey FPGA Board       106         Appendix B       108         Matlab Codes       108         B.1       Walsh Hadamard Based Convolution with PN sequences       108         B.2       Approximation of ATAN Function       110         B.3       Averaging Correlation Method       112         B.4       Modified-Code Averaging Method       113                                          | 5.3.5 Local Code Component                             | 69  |

| 5.3.8       Carrier Phase Estimator       78         5.3.8.1       Simple Digital ATAN       79         5.3.8.2       Computing ATAN Function Using CORDIC       81         5.3.9       Time-Domain Serial Correlators       82         5.4       FPGA Implementation of GPS Block Processor       83         5.5       Overall Performance and Discussion of the Results       89         Chapter 6       93         Summary, Conclusion, and Recommendations       93         6.1       Summary       93         6.2       Conclusion       95         6.3       Recommendations       95         6.3       Recommendations       96         Predix A       106       106         The Ballynuey FPGA Board       106         Appendix A       108         8.1       Walsh Hadamard Based Convolution with PN sequences       108         8.2       Approximation of ATAN Function       110         8.3       Averaging Correlation Method       112         8.4       Modified-Code Averaging Method       113                                                                                                                                        | 5.3.6 Complex Multiplier                               | 72  |

| 5.3.8.1 Simple Digital ATAN       79         5.3.8.2 Computing ATAN Function Using CORDIC       81         5.3.9 Time-Domain Serial Correlators       82         5.4 FPGA Implementation of GPS Block Processor       83         5.5 Overall Performance and Discussion of the Results       89         Chapter 6       93         Summary, Conclusion, and Recommendations       93         6.1 Summary       93         6.2 Conclusion       95         6.3 Recommendations       95         6.3 Recommendations       98         Appendix A       106         The Ballynuey FPGA Board       108         Matlab Codes       108         B.1 Walsh Hadamard Based Convolution with PN sequences       108         B.2 Approximation of ATAN Function       110         B.3 Averaging Correlation Method       112         B.4 Modified-Code Averaging Method       113         Appendix C       114                                                                                                                                                                                                                                                    | 5.3.7 Peak Searcher                                    | 76  |

| 5.3.8.2 Computing ATAN Function Using CORDIC.       81         5.3.9 Time-Domain Serial Correlators       82         5.4 FPGA Implementation of GPS Block Processor       83         5.5 Overall Performance and Discussion of the Results       89         Chapter 6       93         Summary, Conclusion, and Recommendations       93         6.1 Summary       93         6.2 Conclusion       95         6.3 Recommendations       95         6.3 Recommendations       95         References       98         Appendix A       106         The Ballynuey FPGA Board       108         Matlab Codes       108         B.1 Walsh Hadamard Based Convolution with PN sequences       108         B.2 Approximation of ATAN Function       110         B.3 Averaging Correlation Method       112         B.4 Modified-Code Averaging Method       113         Appendix C       114                                                                                                                                                                                                                                                                    | 5.3.8 Carrier Phase Estimator                          | 78  |

| 5.3.9       Time-Domain Serial Correlators       82         5.4       FPGA Implementation of GPS Block Processor       83         5.5       Overall Performance and Discussion of the Results       89         Chapter 6       93         Summary, Conclusion, and Recommendations       93         6.1       Summary         93       6.2         6.3       Recommendations         95       6.3         84       95         References       98         Appendix A       106         The Ballynuey FPGA Board       106         Matlab Codes       108         B.1       Walsh Hadamard Based Convolution with PN sequences       108         B.2       Approximation of ATAN Function       110         B.3       Averaging Correlation Method       112         B.4       Modified-Code Averaging Method       113         Appendix C       114                                                                                                                                                                                                                                                                                                      | 5.3.8.1 Simple Digital ATAN                            | 79  |

| 5.4 FPGA Implementation of GPS Block Processor       83         5.5 Overall Performance and Discussion of the Results       89         Chapter 6       93         Summary, Conclusion, and Recommendations       93         6.1 Summary       93         6.2 Conclusion       95         6.3 Recommendations       95         References       98         Appendix A       106         The Ballynuey FPGA Board       106         Matlab Codes       108         B.1 Walsh Hadamard Based Convolution with PN sequences       108         B.2 Approximation of ATAN Function       110         B.3 Averaging Correlation Method       112         B.4 Modified-Code Averaging Method       113         Appendix C       114                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.3.8.2 Computing ATAN Function Using CORDIC           | 81  |

| 5.5 Overall Performance and Discussion of the Results       89         Chapter 6       93         Summary, Conclusion, and Recommendations       93         6.1 Summary       93         6.2 Conclusion       95         6.3 Recommendations       95         References       98         Appendix A       106         The Ballynuey FPGA Board       106         Appendix B       108         Matlab Codes       108         B.1 Walsh Hadamard Based Convolution with PN sequences       108         B.2 Approximation of ATAN Function       110         B.3 Averaging Correlation Method       112         B.4 Modified-Code Averaging Method       113         Appendix C       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5.3.9 Time-Domain Serial Correlators                   | 82  |

| Chapter 6       93         Summary, Conclusion, and Recommendations       93         6.1 Summary       93         6.2 Conclusion       95         6.3 Recommendations       95         6.3 Recommendations       95         6.3 Recommendations       95         References       98         Appendix A       106         The Ballynuey FPGA Board       106         Appendix B       108         Matlab Codes       108         B.1 Walsh Hadamard Based Convolution with PN sequences       108         B.2 Approximation of ATAN Function       110         B.3 Averaging Correlation Method       112         B.4 Modified-Code Averaging Method       113         Appendix C       114                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.4 FPGA Implementation of GPS Block Processor         | 83  |

| Summary, Conclusion, and Recommendations       93         6.1       Summary       93         6.2       Conclusion       95         6.3       Recommendations       95         6.3       Recommendations       95         References       98         Appendix A       106         The Ballynuey FPGA Board       106         Appendix B       108         Matlab Codes       108         B.1       Walsh Hadamard Based Convolution with PN sequences       108         B.2       Approximation of ATAN Function       110         B.3       Averaging Correlation Method       112         B.4       Modified-Code Averaging Method       113         Appendix C       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.5 Overall Performance and Discussion of the Results  | 89  |

| Summary, Conclusion, and Recommendations       93         6.1       Summary       93         6.2       Conclusion       95         6.3       Recommendations       95         6.3       Recommendations       95         References       98         Appendix A       106         The Ballynuey FPGA Board       106         Appendix B       108         Matlab Codes       108         B.1       Walsh Hadamard Based Convolution with PN sequences       108         B.2       Approximation of ATAN Function       110         B.3       Averaging Correlation Method       112         B.4       Modified-Code Averaging Method       113         Appendix C       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Chapter 6                                              | 03  |

| 6.1 Summary       93         6.2 Conclusion       95         6.3 Recommendations       95         6.3 Recommendations       95         References       98         Appendix A       106         The Ballynuey FPGA Board       106         Appendix B       106         Matlab Codes       108         B.1 Walsh Hadamard Based Convolution with PN sequences       108         B.2 Approximation of ATAN Function       110         B.3 Averaging Correlation Method       112         B.4 Modified-Code Averaging Method       113         Appendix C       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                        |     |

| 6.2 Conclusion       95         6.3 Recommendations       95         References       98         Appendix A       106         The Ballynuey FPGA Board       106         Appendix B       106         Matlab Codes       108         B.1 Walsh Hadamard Based Convolution with PN sequences       108         B.2 Approximation of ATAN Function       110         B.3 Averaging Correlation Method       112         B.4 Modified-Code Averaging Method       113         Appendix C       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Summary, Conclusion, and Recommendations               | 93  |

| 6.3 Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6.1 Summary                                            |     |

| References       98         Appendix A       106         The Ballynuey FPGA Board       106         Appendix B       106         Matlab Codes       108         B.1 Walsh Hadamard Based Convolution with PN sequences       108         B.2 Approximation of ATAN Function       110         B.3 Averaging Correlation Method       112         B.4 Modified-Code Averaging Method       113         Appendix C       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6.2 Conclusion                                         |     |

| Appendix A       106         The Ballynuey FPGA Board       106         Appendix B       108         Matlab Codes       108         B.1 Walsh Hadamard Based Convolution with PN sequences       108         B.2 Approximation of ATAN Function       110         B.3 Averaging Correlation Method       112         B.4 Modified-Code Averaging Method       113         Appendix C       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6.3 Recommendations                                    | 95  |

| The Ballynuey FPGA Board       106         Appendix B       108         Matlab Codes       108         B.1 Walsh Hadamard Based Convolution with PN sequences       108         B.2 Approximation of ATAN Function       110         B.3 Averaging Correlation Method       112         B.4 Modified-Code Averaging Method       113         Appendix C       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | References                                             |     |

| Appendix B108Matlab Codes108B.1 Walsh Hadamard Based Convolution with PN sequences108B.2 Approximation of ATAN Function110B.3 Averaging Correlation Method112B.4 Modified-Code Averaging Method113Appendix C114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Appendix A                                             | 106 |

| Matlab Codes       108         B.1 Walsh Hadamard Based Convolution with PN sequences       108         B.2 Approximation of ATAN Function       110         B.3 Averaging Correlation Method       112         B.4 Modified-Code Averaging Method       113         Appendix C       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | The Ballynuey FPGA Board                               | 106 |

| B.1 Walsh Hadamard Based Convolution with PN sequences       108         B.2 Approximation of ATAN Function       110         B.3 Averaging Correlation Method       112         B.4 Modified-Code Averaging Method       113         Appendix C       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Appendix B                                             | 108 |

| B.2 Approximation of ATAN Function       110         B.3 Averaging Correlation Method       112         B.4 Modified-Code Averaging Method       113         Appendix C       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Matlab Codes                                           | 108 |

| B.3 Averaging Correlation Method       112         B.4 Modified-Code Averaging Method       113         Appendix C       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | B.1 Walsh Hadamard Based Convolution with PN sequences | 108 |

| B.4 Modified-Code Averaging Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | B.2 Approximation of ATAN Function                     | 110 |

| Appendix C 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | B.3 Averaging Correlation Method                       | 112 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | B.4 Modified-Code Averaging Method                     | 113 |

| VHDL Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Appendix C                                             | 114 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VHDL Codes                                             | 114 |

| C.1 Walsh-Based Convolution                          | 114 |

|------------------------------------------------------|-----|

| C.2 Modified-Code Averaging Correlator (Acquisition) | 126 |

| C.2.1 Carrier Wipe-Off and Downsampling              | 126 |

| C.2.2 The FFT Block                                  | 134 |

| C.2.3 Frequency Domain Multiplication                | 145 |

| C.2.4 The IFFT Block                                 | 148 |

| C.2.5 The Peak Searcher                              | 148 |

| C.3 Serial Correlators (Tracking-Like Estimator)     | 153 |

| Appendix D                                           | 158 |

| C Codes                                              | 158 |

| D.1 C Code for Carrier Wipe-off and Averaging        | 158 |

| D.2 C Code for FFT Block                             | 162 |

| D.3 C Code for Frequency Domain Multiplication       | 166 |

| D.4 C Code for FFT Block                             | 171 |

| D.5 C Code for Peak Search                           | 175 |

| D.6 C Code for Tracking                              | 177 |

| Appendix E                                           | 180 |

| FPGA Layout of the Mapped Designs                    | 180 |

| E.1 Modified-Code Averaging Correlator (Acquisition) | 181 |

| E.2 Serial Correlators of the GPS Block Processing   | 186 |

| Abstract                                             |     |

# List of Tables

| Table 5-1. Implementation Cost (Virtex Resources)          | 91 |

|------------------------------------------------------------|----|

| Table 5-2. Maximum Net Delays in (nsec) for Each Partition | 92 |

# List of Figures

| Figure 2-1: Block Diagram of a GPS Receiver                                | 11 |

|----------------------------------------------------------------------------|----|

| Figure 2-2: Code Tracking Using Delay-Lock-Loop (DLL)                      | 13 |

| Figure 2-3: Carrier Tracking Using Frequency-Lock-Loop (FLL)               | 13 |

| Figure 2-4: Serial Search Technique                                        | 16 |

| Figure 2-5: Parallel Carrier-Frequency Search Technique                    | 17 |

| Figure 2-6: FFT-Based Circular Correlator                                  | 18 |

| Figure 2-7: Parallel Code-Phase Search Technique                           | 18 |

| Figure 3-1: FNT-Based Convolver                                            | 25 |

| Figure 3-2: Example for the Walsh-Based Convolution                        | 30 |

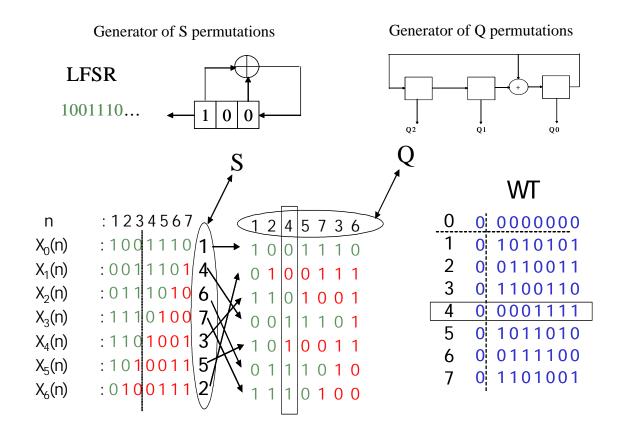

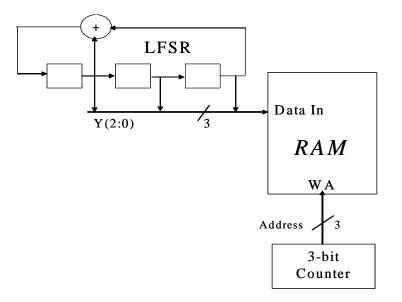

| Figure 3-3: Hardware Implementation of the Generator of the Permutations S | 33 |

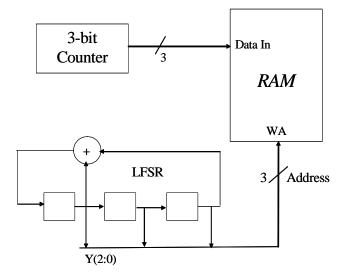

| Figure 3-4: Implementation of the Inverse Permutations of S                | 34 |

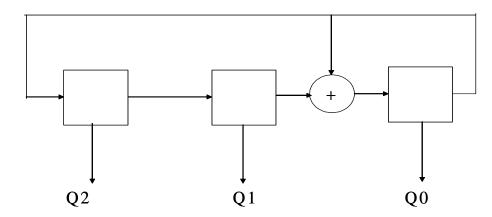

| Figure 3-5: Implementation of Generator of Permutations Q                  | 35 |

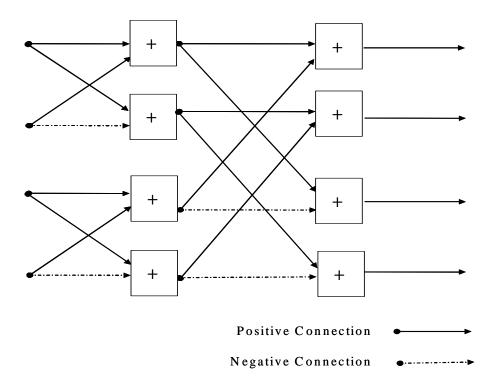

| Figure 3-6: 4-Point Walsh-Hadamard Butterfly Structure                     | 36 |

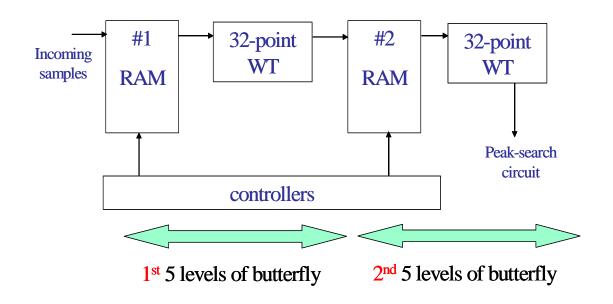

| Figure 3-7: Implementation of 1024-Point WHT                               | 38 |

| Figure 4-1: Zero-Padding Circular Correlation Problem                      | 47 |

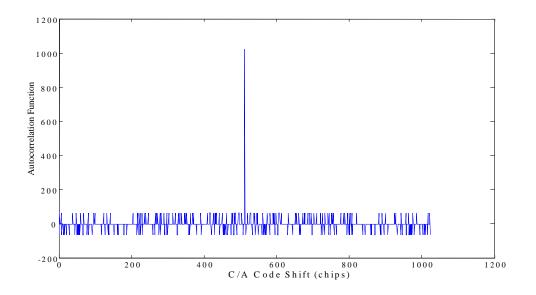

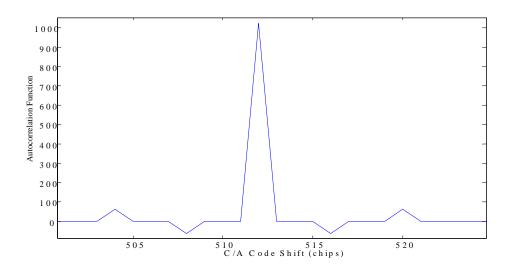

| Figure 4-2: C/A Code Auto Correlation Function                             | 49 |

| Figure 4-3: C/A Code Auto Correlation Peak Shape                           | 49 |

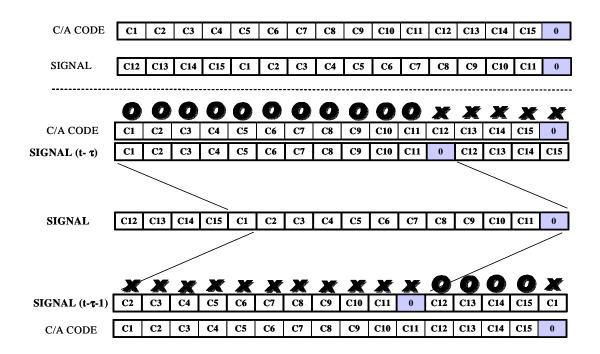

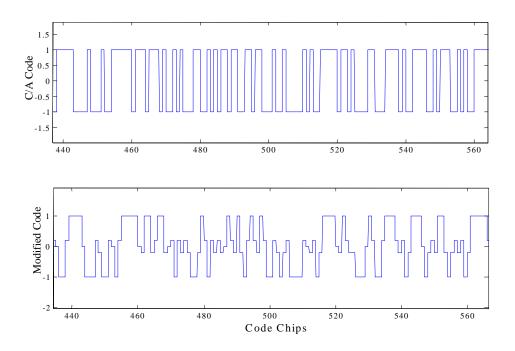

| Figure 4-4: C/A Code and the Modified Code                                                      |

|-------------------------------------------------------------------------------------------------|

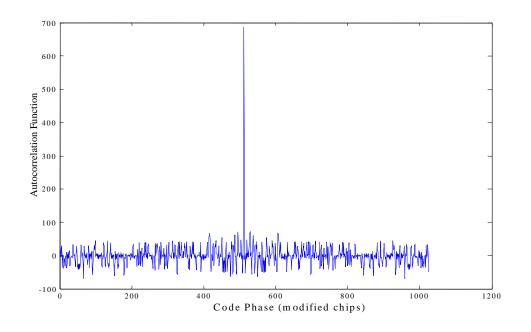

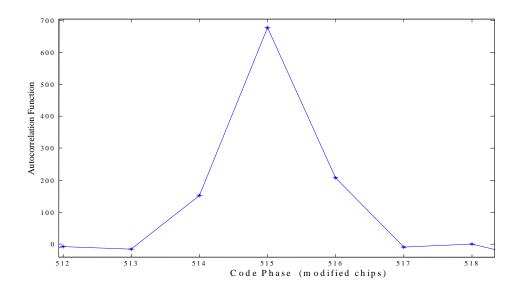

| Figure 4-5: Modified-Code Winner Correlation Function51                                         |

| Figure 4-6: Peak Shape of a Winner Correlation Function for the Modified-Code51                 |

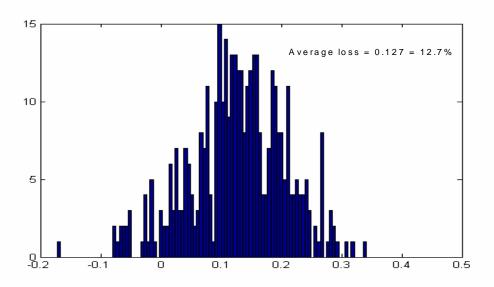

| Figure 4-7: SNR Loss in 200-ms of a GPS Signal Using the Modified-Code Averaging<br>Method      |

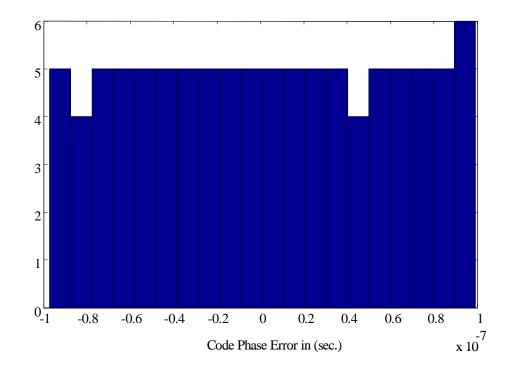

| Figure 4-8: Code-Phase Error Using Modified-Code Averaging Method54                             |

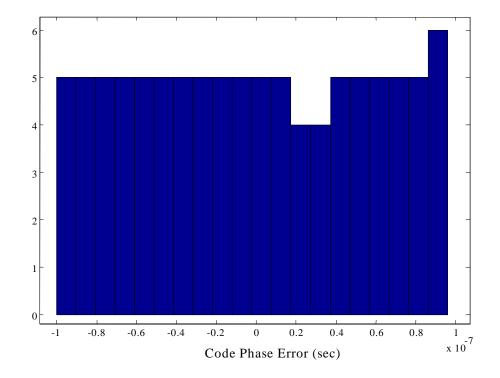

| Figure 4-9: Code-Phase Error Using 5000-Point FFT Method55                                      |

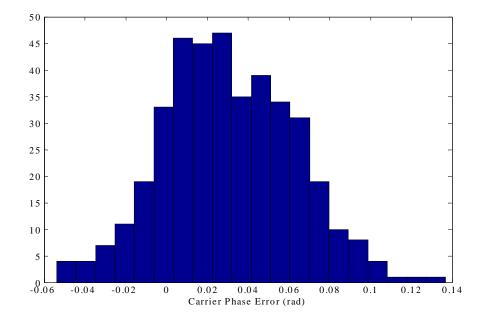

| Figure 4-10: Carrier-Phase Error Using Modified-Code Averaging Method56                         |

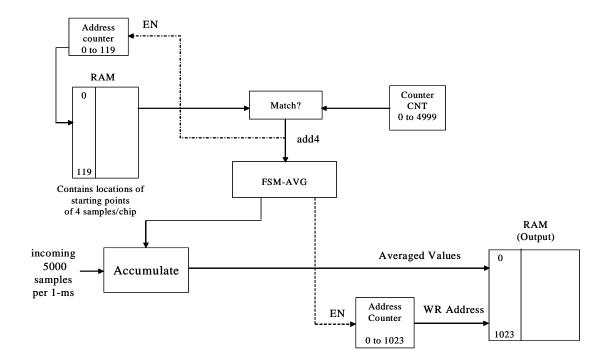

| Figure 4-11: Proposed Architecture for Block Processing Using Modified-Code Averaging<br>Method |

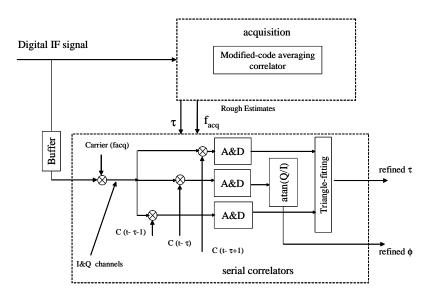

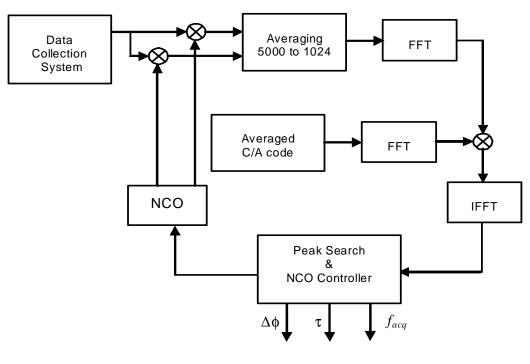

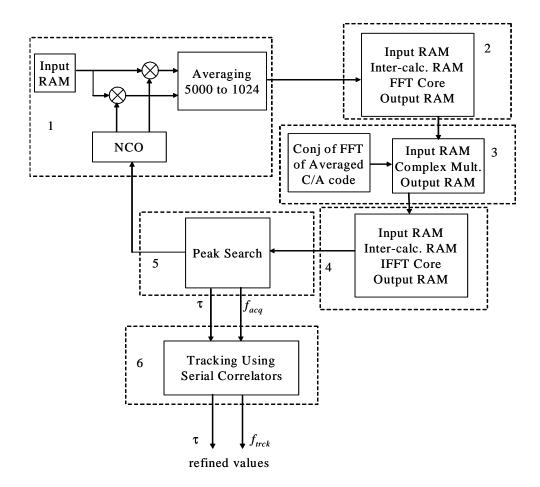

| Figure 5-1: Acquisition Using Averaging-Correlator61                                            |

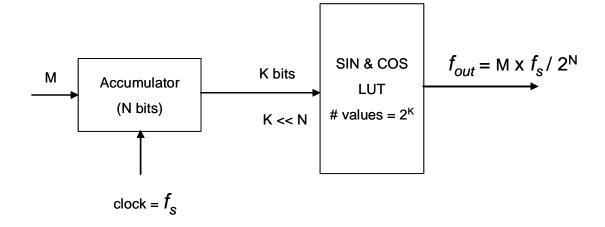

| Figure 5-2: Typical NCO Implementation64                                                        |

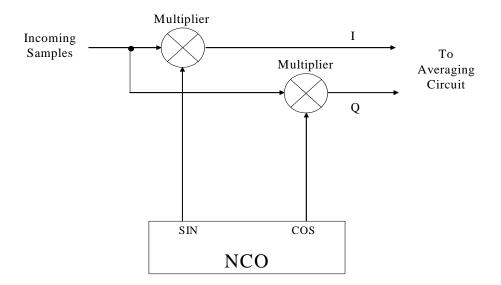

| Figure 5-3: Carrier Wipe-off Circuit65                                                          |

| Figure 5-4: Simplified Circuit for the Averager66                                               |

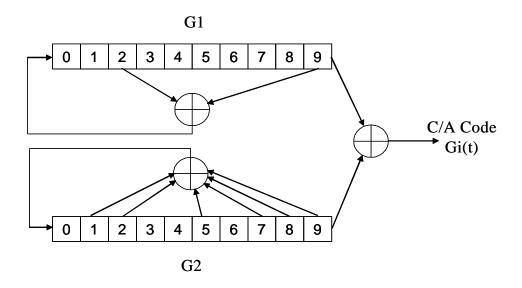

| Figure 5-5: Local Code Generator70                                                              |

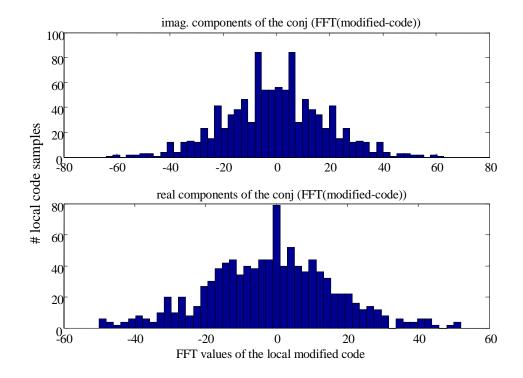

| Figure 5-6: Distribution of the Values of the FFT of the Local Modified-Code71                  |

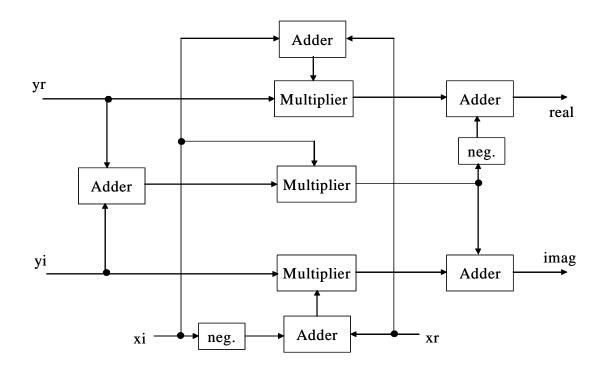

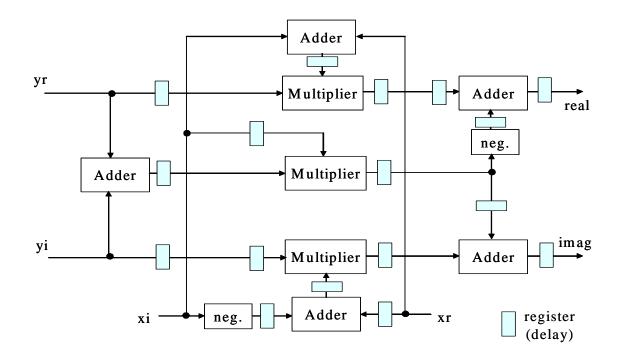

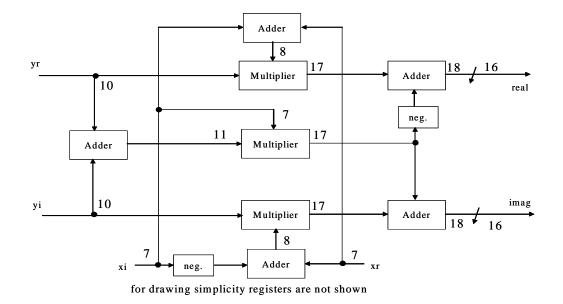

| Figure 5-7: Efficient Implementation of a Complex Multiplier73                                  |

| Figure 5-8: FPGA-Based Architecture of the Complex Multiplier74                                 |

| Figure 5-9: The Implemented Complex Multiplier76                                                |

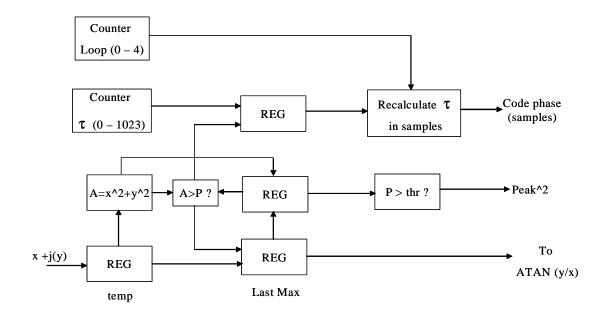

| Figure 5-10: Simplified Diagram of the Peak Searcher77                                          |

xi

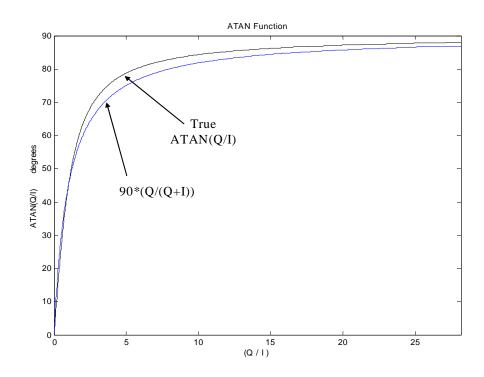

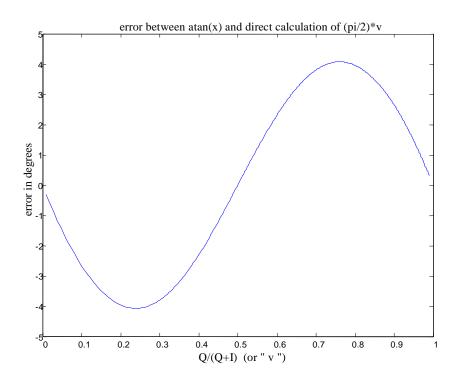

| Figure 5-11: ATAN Function and Its Approximation80                                                    |

|-------------------------------------------------------------------------------------------------------|

| Figure 5-12: ATAN Function's Approximation Error81                                                    |

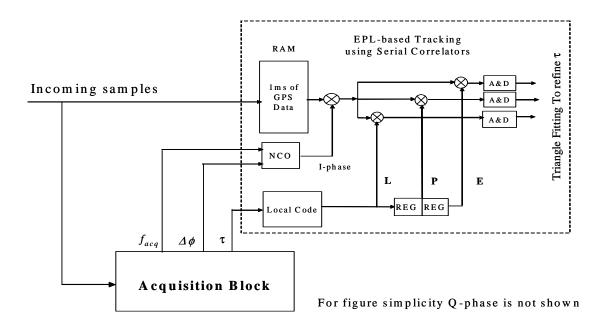

| Figure 5-13: Serial Correlators Based Process                                                         |

| Figure 5-14: System Partitioned into Small Components                                                 |

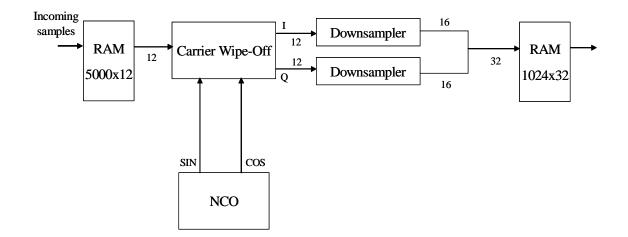

| Figure 5-15: Carrier Wipe-off and Averager (Downsampler)85                                            |

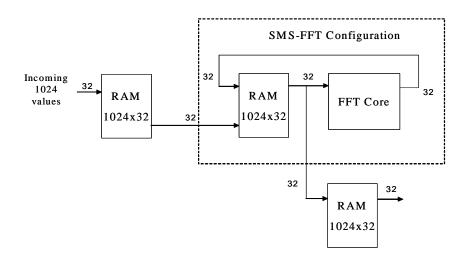

| Figure 5-16: FFT Block85                                                                              |

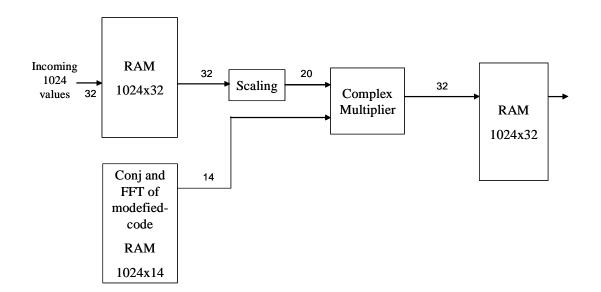

| Figure 5-17: Frequency Domain Multiplier Block                                                        |

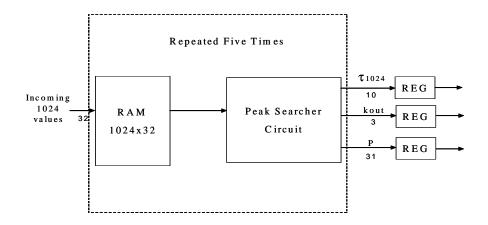

| Figure 5-18: Peak Searcher Block                                                                      |

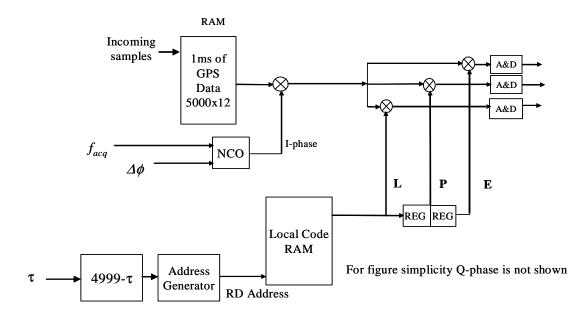

| Figure 5-19: Estimator Block (Serial Correlators)                                                     |

| Figure 5-20: FPGA Layout of the Mapped Design of the Averager and the Carrier Wipe-<br>off Components |

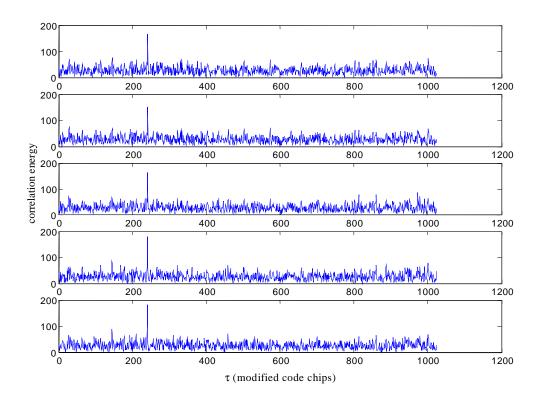

| Figure 5-21: Hardware-Based Results of the Averaging Correlation                                      |

xii

## List of Abbreviations

- ADC: Analog to Digital Converter

- ASIC: Application Specific Integrated Circuits

- BPSK: Binary Phase Shift Keying

- C/A: Coarse Acquisition

- CDMA: Code Division Multiple Access

- CORDIC: Coordinate Rotation Digital Computer

- DLL: Delay Lock Loop

- DSP: Digital Signal Processor

- DS-SS: Direct Sequence-Spread Spectrum

- EPL: Early Prompt Late

- FFT: Fast Fourier Transform

- FIR: Finite Impulse Response

- FLL: Frequency Lock Loop

- FNT: Fermat Number Transform

- FPGA: Field Programmable Gate Array

- GPS: Global Positioning System

- IFFT: Inverse Fast Fourier Transform

- IP: Intellectual Propriety

- LFSR: Linear Feedback Shift Register

- NCO: Numerically Controlled Oscillator

- NTT: Number Theoretic Transform

- PLL: Phase Lock Loop

- PN: Pseudo Noise

- PPS: Precise Positioning Service

- PRN: Pseudo Random Noise

- PSK: Phase Shift Keying

- RF: Radio Frequency

- SMS: Single Memory Setup

- SNR: Signal to Noise Ratio

- SPS: Standard Positioning Service

- TOA: Time of Arrival

- VHDL: VHSIC Hardware Description Language

- VHSIC: Very High Speed Integrated Circuit

- VLSI: Very Large Scale Integration

### Chapter 1

### Introduction

With the global positioning system (GPS) a user can get accurate positioning information at any location on Earth (French, 1996). GPS can accurately guide airplanes by providing navigational information at any stage of takeoff, flight, and landing (Kayton, 1997). GPS receivers perform many signal processing steps to synchronize the received GPS signal with a local code to enhance the positioning accuracy (Braasch, 1999). The time required to acquire satellite signals is the main problem in most GPS receivers; therefore, many researchers have investigated different designs of such receivers.

Many algorithms for acquisition of GPS signals have been developed and evaluated (Lin, 2000). Until now, the developed algorithms were not fast enough to acquire GPS signals in real time (Tsui, 2000 and Molyneux, 2002). The slow acquisition process is due to many reasons, one of them is the large computation cost of the circular correlation. Computing the correlation function in the timedomain is a very time-consuming process (Braasch, 1999). Performing the correlation of two N-point sequences using frequency domain multiplication reduces the calculations N/logN times, which is a significant reduction of the computation cost and facilitates real-time GPS signal acquisition (Van Nee, 1991).

However, direct implementation of fast Fourier transform (FFT) based circular correlation on digital signal processor (DSP) or microprocessor does not satisfy the requirements of real-time acquisition. The computation time is very long due to the slow calculation of the required FFT. The processing technique in a DSP or a microprocessor uses sequential executions of all the operations. This softwarebased technique processes all the multiplications of the FFT one at a time, which is not appropriate for real-time applications.

The speed of finding the correlation is affected, not by only the processing technique but by the selected correlation method as well. The FFT based correlation method requires approximately 3NlogN complex multiplications and 3NlogN complex additions (Smith W., 1995). These complex operations are time consuming and need to be simplified. A simpler correlation algorithm is preferable for fast GPS signal acquisition. In addition, parallel operations may reduce the total acquisition time making real-time processing feasible. A parallel processing implementation of signal acquisition is possible using a field programmable gate array (FPGA).

With fast acquisition, the use of software-based GPS receivers can be extended to additional real-time applications. Providing these information in real time will lead to major advancement in many civilian and military applications. The main challenging problem is to build a GPS receiver that has a simple, fast, and non-computationally extensive algorithm which satisfies real-time requirements.

The purpose of this dissertation is to tackle this problem. Specifically, algorithms and field programmable gate array (FPGA) based architectures are developed for real-time acquisition and tracking of GPS signals. This dissertation uses the parallel processing concept supported in the FPGA to replace the current sequential processing platform. Also, this work investigates many algorithms to reduce the computations required by the correlation function in order to shorten the acquisition time. One algorithm uses an averaging correlation for GPS signal acquisition that simplifies the implementation and reduces the required computations. This method is implemented in FPGA to benefit from the parallel processing of this technology. The implemented architecture solves the presented problem of the GPS receivers by significantly reducing the acquisition time. The performance of this implementation enables real-time acquisition of one satellite in less than one millisecond. Comparing this performance with the performance of the current GPS receivers where the acquisition time is more than 1 second, the developed architecture minimizes the acquisition time 1000 times. The presented solution is very important since it extends the use of GPS to both civilian and military applications. As a result, precise and stable navigational systems are achievable.

Chapter 2 presents a necessary and brief background to provide enough information to understand the problem. First, a brief description of a code division multiple access (CDMA) system is provided. Then the global positioning system is described. The GPS signal structure is also presented. The GPS receiver architecture is presented along with its main processes. The main processes of the GPS receiver, signal tracking and acquisition, are explained. Different acquisition search techniques are also presented along with their advantages and disadvantages.

Chapter 3 presents two algorithms to replace the necessity of the FFT computations to calculate the correlation function. The presented algorithms, use transforms that require simpler operations than the FFT. These transforms are the Fermat number transform (FNT) and the Walsh Hadamard transform (WHT). Descriptions of both algorithms are presented with examples to show how the correlation functions are computed. The possibility of using these algorithms in the GPS signal acquisition is discussed.

Chapter 4 describes an averaging correlation method that re-sizes the 5000point correlation function to the size of the C/A code, which is 1023-points. The averaging correlation method is inspected and compared against the regular correlation method. The effects of the averaging method on detection and misdetection probabilities are also provided. The limitation of implementing the averaging method is explained. Different algorithms were suggested to ease the implementation of this method in an FPGA. One fast and easy-to-implement algorithm for averaging correlation is developed and explained in detail. The algorithm is called modified-code averaging correlation based GPS block processing. The advantages and the limitations of using the developed algorithm for block processing of the GPS signals are also presented in this chapter.

Chapter 5 provides the implementation of the developed algorithm. Each component implementation is described. Circuits for those components are pro-

vided. The whole system was partitioned and implemented to fit into a small FPGA. The size, speed, and accuracy of the implemented circuits are verified for real-time applications. Full design analysis is also provided in Chapter 5.

Chapter 6 presents a summary, conclusion, description of future work and recommendations. First, the summary of this work is presented. It briefly describes the problem, the developed solutions and the performance. The conclusion is presented next. The accomplished improvements and advantages in the acquisition and the tracking implementations are stated. Possible future work and recommendations are then suggested.

The FPGA platform used during the design development and testing is described in Appendix A. The Matlab, VHDL, and C codes that were developed during this work are presented in Appendices B, C, and D. The FPGA layout (of the mapped designs) are shown in Appendix E.

### Chapter 2

### Background

### 2.1 Introduction

Chapter 2 presents an overview of the Global Positioning System (GPS). However, an important related issue, the telecommunication techniques involved with signal processing, needs to be discussed prior to the presentation of the GPS. These techniques include a description of the carrier signal, navigation data, satellite codes, and modulation techniques. Already existing communication systems that are useful for GPS transmission are presented first. The GPS system and its signal structure are discussed next. The final section is an overview of the main GPS signal processes.

### 2.2 Spread Spectrum and Code Division Multiple Access

A spread spectrum communication system uses larger frequency bandwidth than is needed to transmit information. Therefore, the transmission bandwidth is much larger than the information bandwidth (Peterson, 1995). The transmission bandwidth is found by using a spreading signal, which is independent of the information data. Military applications have used the spread spectrum techniques for more than fifty years because it offers a system that rejects intentional and unintentional interference (Gibson, 1993). Additionally, a spread spectrum delivers multi-user random access and a high resolution range. These traits were a catalyst for commercial applications switching to spread spectrum communication techniques in the last decade. These applications include mobile radio applications, satellite communications, and positioning systems. The most widely used spread spectrum is the direct sequence spread spectrum (DS-SS) (Dixon, 1994). DS-SS is achieved by multiplying a radio frequency (RF) carrier and a pseudo-random noise code (PRN code). Every user or transmitter uses a different code which is orthogonal to the codes of the other users or transmitters. This method is called the Code Division Multiple Access (CDMA) (Hassan, 1998).

In the transmitter, a PRN code is modulated with the information using phase shift keying (PSK) techniques. The PRN-modulated-information signal is then mixed with the carrier. Therefore, the RF signal is substituted with a wide bandwidth signal with the spectrum equivalent to a noise signal. The demodulation process is then simply carried out by multiplying a local copy of the PRN modulated carrier with the incoming signal. The local copy of the code and the carrier must be synchronized in order to demodulate the signal (Cook, 1983). A peak is achieved when the two signals are aligned. The correlated signal is then filtered and sent to a PSK demodulator.

A simple form of direct sequence spread spectrum (DS-SS) uses binary phase shift keying (BPSK). BPSK modulation changes the carrier phase by 180 degrees if the PRN code chip is -1. Otherwise, the carrier phase is not changed. More details pertaining to these techniques can be found in (Proakis, 1995).

#### 2.3 Global Positioning System

A Global Positioning System (GPS) is a satellite-based system. It uses the concept of one-way time-of-arrival (TOA) ranging. The range is computed by multiplying the speed of light by the amount of delay that a GPS signal needs to travel from the satellite (or the transmitter) to the user (or the receiver) (Braasch, 1999). Calculating a three-dimensional position requires utilizing three satellites. An additional satellite is necessary to solve for the receiver clock bias (Misra, 2001). Since the US military is considered a global force, the GPS system is designed to provide accurate positioning information anywhere in the world 24 hours a day. The GPS system uses 24 satellites that are placed in six orbital planes with four satellites in each plane (Kaplan, 1996 and Parkinson, 1996).

The transmitter in each satellite sends the navigation data along with ranging codes using the CDMA scheme. All GPS satellites use two frequencies for navigation purposes, known as L1 and L2. L1, with a carrier frequency of 1575.42 MHz, is used for both civilian (standard) and military (precise) positioning services, SPS and PPS respectively. Whereas L2, which uses 1227.6 MHz signal, is primarily used for military service (Kaplan, 1996 and Parkinson, 1996). L2 is used in 90% of all surveying receivers (civilians). Civilians have access to the L2 carrier, but not to the encrypted Y-code.

#### 2.4 GPS Signal Structure

Each GPS satellite has a unique PRN code that is orthogonal to the codes of other satellites. This code is called the coarse acquisition code (C/A code). The C/A

code has a rate of 1.023 MChips/s with a code period of 1ms. The navigation data is binary and has a rate of 50bits/s. This data is sent using a direct sequence spread spectrum and CDMA techniques. The navigation data is bi-phase shift keyed onto the carrier signal and the C/A code is also bi-phase shift keyed onto the resulting signal. A simplified model for the transmitted signal is written as:

$$S_i(t) = A_i C_i(t) D(t) sin(2\pi f t + \phi_0)$$

**2-1.**

where,  $A_i$  is the amplitude of the signal.

- $C_i(t)$  is the C/A code for satellite number *i*

- D(t) is the navigational data

- *f* is the L1 carrier frequency which is 1575.42 MHz

The C/A code is a gold-code type, which has noise-like auto-correlation and cross correlation characteristics. Therefore, identical codes at the exact same chip phase are necessary to produce the maximum correlation peak, otherwise they are not correlated. Each satellite's unique C/A code is used to distinguish the satellite signals from each other. The C/A code phase of the received satellite signal provides important ranging information. To calculate the range from the satellite to the receiver, one can multiply the code phase difference (which is the time a signal spends between satellite and receiver) by the speed of light (Braasch, 1999 and Kaplan, 1996).

At the receiver, the signal changes due to the Doppler effect and noise. A simplified model of a received GPS SPS signal is:

where  $R_i(t)$  is the received GPS SPS signal

$$R_{i}(t) = A_{i}C_{i}(t + \Delta t)D(t + \Delta t)sin(2\pi(f + \Delta f)t + \Delta \phi) + n(t)$$

**2-2.**

$\Delta t$  is the time delay (the time required for the signal to travel to the receiver)  $\Delta f$  is the carrier frequency offset (due to doppler and LO frequency uncertainties).

${\scriptstyle \Delta \phi}$  is the carrier phase offset. (due to oscillator, sampler, and hardware)

n(t) is a white noise.

For a more accurate model of the received signal read (Kaplan, 1996 and Parkinson, 1996).

### 2.5 GPS Receiver Architecture

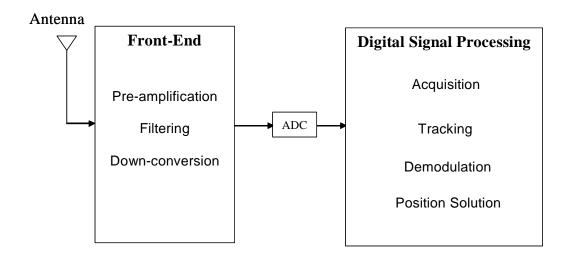

The design of a digital GPS receiver is divided into two parts. One part is the front-end component which consists of an antenna, filters, amplifiers, and a down conversion step. The signal is then digitized by an analog to a digital converter (ADC). After the signal is digitized, digital signal processing is performed in the second part of the receiver. The second part of a GPS receiver is the base-band processor of the digitized GPS signal (Tsui, 2000). The base-band processor is responsible for many signal processing steps that include, but are not limited to, PRN code synchronization, demodulation, and range calculation. Figure 2-1 shows a block diagram of a GPS receiver. This research will only investigate the baseband processing aspect of the GPS software-radio. Thus, the various designs of the front-end will not be discussed in this dissertation. However, a novel implemented design of a GPS receiver front-end can be found in (Akos, 1997 and Akos, 1996).

Figure 2-1: Block Diagram of a GPS Receiver

The base-band still needs major advances and new algorithms to speed up the position calculation for real-time applications. Such applications are currently under intense research to determine how much integration with the available GPS services can be accomplished. Navigational systems will benefit from being able to have high speed calculations and quick updates regarding their position and direction.

Therefore, a description of the major and necessary base-band processes of a GPS receiver is presented next. The most important and critical signal processing steps are the acquisition and the tracking processes. Acquisition is sometimes referred to as a search or detection process. It searches for the satellite code and for its code phase and the carrier frequency offset. Whereas, tracking is sometimes referred to as synchronization. Synchronization of the code and the carrier are necessary for a GPS receiver to be able to read the navigation data (Braasch, 1999). Moreover, acquisition and tracking processes provide information about detected satellites, pseudo-ranges, and precise carrier frequencies. The position computation becomes a straight forward problem in these cases.

#### 2.5.1 Signal Tracking

As was previously stated, tracking needs acquisition information to be able to start functioning. Signal tracking is the process that a receiver does all the time to synchronize or lock-in the GPS signal (Tsui, 2000). Therefore, a description of this process is presented before the description of the acquisition process. If the acquisition estimations are available, tracking processes (or loops) synchronize the local generated code and carrier with the received signal. Tracking loops then remove the carrier and the code to read the navigational data. They also provide critical timing information used in the position solution.

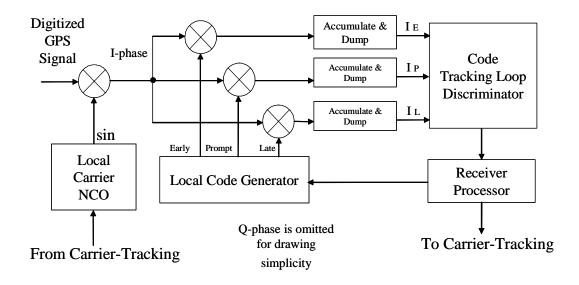

One of the tracking loops is the code tracking loop. The code tracking loop is important due to its role in the range calculation. This loop generates a synchronized copy of the C/A code to remove the spread spectrum modulation. A delaylock-loop (DLL) can be used for code tracking. Figure 2-2 shows a code tracking loop using a DLL architecture.

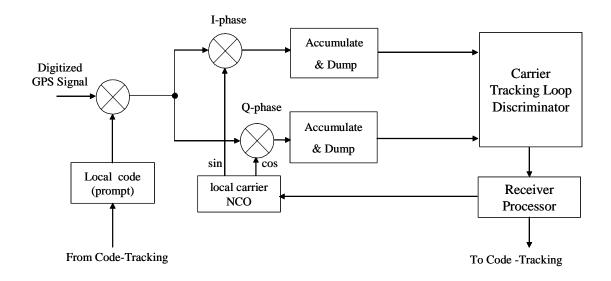

The other tracking loop is the carrier tracking loop. This loop tracks either the phase or the frequency of the incoming signal. It is also responsible for decoding the data encoded on the carrier. Frequency and/or phase lock loops are used for carrier tracking (Uijt, 1998). A FLL-based carrier tracking loop is shown in Figure 2-3.

Figure 2-2: Code Tracking Using Delay-Lock-Loop (DLL)

Figure 2-3: Carrier Tracking Using Frequency-Lock-Loop (FLL)

A code-tracking loop requires a precise carrier frequency or phase. Whereas, a carrier-tracking loop requires precise code phase estimation. Therefore, the two tracking loops are coupled in (Akos, 1997 and Uijt, 1998). These techniques are well known and have been studied extensively. These tracking loops were used in GPS receivers. Their characteristics and performances were presented in detail in (Braasch, 1999 and Uijt, 1998).

Tracking loops require initial estimations of the code phase and the carrier frequency. This is usually the task of the acquisition process. Also, when a tracking loop loses lock at any time, a re-acquisition process is required. The next section presents the acquisition process and some of its search methods.

#### 2.5.2 Signal Acquisition

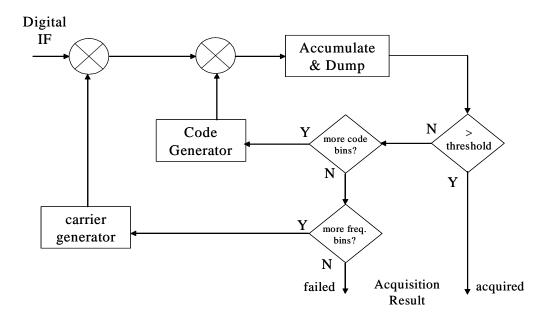

In a CDMA system, when the received signal is multiplied by a synchronized version of the PRN code, the signal is despread. Its power increases over the noise floor. Therefore it appears as a correlation peak. However, in order for a receiver to synchronize to the received signal, an initial estimation of the code and carrier is calculated. The acquisition process is the first process required by the GPS receiver (Kaplan, 1996). The acquisition process conducts a three dimensional search. The three elements (or search bins) are the available C/A code, the code phase, and the carrier frequency offset. If we assume that a GPS receiver knows which satellite code it is searching for, then a 2-D search is required (Ward, 1996).

One dimension is the code phase in range of 1,023 chips. The code phase resolution is half of a code chip. This resolution is required since the correlation peak is considered a true peak only if the code phase is within a half chip. The second search dimension is for the carrier frequency. Its range is ±10kHz centered at an intermediate frequency (IF) of 1.25MHz. The resolution of the carrier frequency is typically 667Hz for 1-ms integration (Ward, 1996). Searching with 500Hz steps can be used (Uijt, 1998).

Therefore, in a GPS receiver, this search detects the correlation peak and compares it to a certain threshold to determine whether a satellite was detected or not. When a satellite is detected the auto-correlation result provides a rough estimation of the code phase and the carrier frequency. The acquisition process should provide this data. However, if the search process does not locate a peak that passed the detection threshold, a satellite is considered "not-acquired" and the search continues.

These searches are very slow especially when the GPS receiver does not know anything about its last position and the satellites' orbits. When this occurs, the receiver searches all of the satellites in a certain order. This procedure is called a "cold start." Whereas, if the receiver has knowledge regarding a previous position and an approximation of the satellites' orbits, this data aids the search process. This is known as a "warm start." Many different search algorithms were investigated and tested in (Lin, 2000 and Akos, 1997).

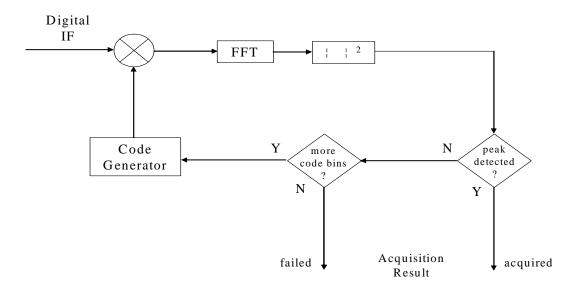

A serial search can be done by evaluating each unknown until a correct combination of the parameters is achieved. If there is no correct combination of carrier frequency and code phase, the receiver searches for a different PRN code. Figure 2-4 shows a simplified diagram of the serial search technique. The disadvantage of this search is that it might necessitate exploring all of the combinations of the 2-D search plane serially. Thus, it tests 2,046 half chips on the code phase dimension for 21 carrier frequency search steps (bin resolution=  $\pm 500$ Hz). This means searching approximately 40,000 combinations, which is time consuming (Akos, 1997 and Uijt, 1998).

Figure 2-4: Serial Search Technique

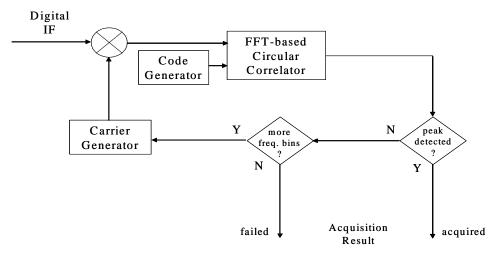

The acquisition process time is shortened when the search dimensions can be searched in parallel. Consider that the incoming signal is multiplied by a local copy of the PRN code, assuming that the correct code phase is utilized, a fast fourier transform (FFT) is performed to the signal after wiping off the code (see Figure 2-5). The acquisition is complete if there is a peak in the output of the FFT after its magnitude is squared. This means the search is performed in parallel for all of the frequencies. In the worse case scenario, the FFT is repeated 2,046 times to cover all of the code phase bins (Akos, 1997 and Uijt, 1998). However, the calculation of one FFT requires much more effort than one serial search.

Figure 2-5: Parallel Carrier-Frequency Search Technique

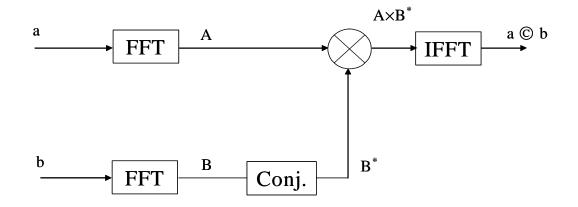

Since the total number of code phase search bins (2,046) is greater than the frequency search bins (21), then searching the code phase dimension in parallel will speed up the acquisition process. This is carried out by using the frequency domain circular correlation. The circular correlation is performed by using the FFT convolution property. FFT-based circular convolution is achieved by multiplying the two sequences (or signals) in the frequency domain. Equation 2-3 shows how the convolution is calculated using the FFT/IFFT functions.

$$y = IFFT(FFT(x1) \times FFT(x2))$$

**2-3.**

Conjugate in frequency domain is similar to signal reversal in time domain. Therefore, circular correlation is implemented in the same fashion by conjugating one signal in the frequency domain before the multiplication. Equation 2-4 shows the FFT-based circular correlation formula. A block diagram of the FFT-based correlator is shown in Figure 2-6.

Figure 2-6: FFT-Based Circular Correlator

A parallel code phase search diagram is shown in Figure 2-7. This type of search greatly minimizes the search time since it evaluates all of the code phases in one single search cycle. Therefore, it does the FFT/IFFT correlation a total of 21 times in the worse case scenario (Van Nee, 1991 and Coenen, 1992).

Figure 2-7: Parallel Code-Phase Search Technique

### 2.6 Block Processing

In the previous section, most of the presented acquisition search methods and the tracking loops are processed sequentially. This means that the samples of the received signal are treated sample by sample. Processing the data sequentially has some disadvantages. One disadvantage is that the receiver may lose the lock of signal due to anomalies (Feng, 1999). Tracking the lost signal needs a re-acquisition step. This problem is considered critical in some conditions such as weak signal tracking or in high-dynamic applications.

One possible solution was introduced in (Feng, 1999). The authors presented a method based on block processing of the data. Block processing has a better performance than the sequential processing. The block size is usually equal to the length of the C/A code. Thus, the block size is 1-ms. If a weak signal detection is desired then a multiple of this size can be used (Lin, 2001). 20-ms block size is used for weak signal processing. Block addition is one of the block processing techniques that helped in weak signals detection (Uijt, 1998). The FFT-based correlator is also employed with block processing to have a fast search method. More information about the GPS block processing can be found in (Feng, 1999 and Tsui, 1997).

### 2.7 Advantages and Disadvantages of the Current Signal Processing

The block processing method was implemented in software in (Feng, 1999). It is easier to implement algorithms in software because a designer can modify the algorithms at any stage of the design development. The important issue in the above reference was the validation of the algorithm and the study of the signal quality monitoring system. Therefore, the delay of software processing was not an issue. However, since the acquisition of the GPS signal is the most time consuming process, the hardware implementation is a necessary step to shorten the acquisition time. Application specific integrated chips (ASICs) have been used in GPS receivers for a long time. They complete the sequential search quickly compared to the software based implementation.

There are two primary sources of trouble connected with slow acquisition. One of them is related to the large computation count in the search algorithm. This can be seen in the FFT-based convolution algorithm. While it is a fast search method, it requires the computation of two FFTs and one IFFT. These functions require a large number of multiplication and addition operations for the 1ms data. Thus, the correlation function takes most of the computation time in the GPS receiver (Gunawardena, 2000). Therefore, investigating different methods for convolution (or correlation) that require less computation time is an important research topic. Using parallel processing concepts along with digital design techniques in a reconfigurable platform such as a field programmable gate array (FPGA) would be the optimum and easily available solution. The advantages of using FPGAs are clear since they provide flexibility of software and performance of ASIC that shorten the acquisition time.

This chapter introduced the GPS system and the current GPS receiver implementations. The required processes for a GPS receiver were introduced. They are the acquisition and the tracking processes. Current search techniques were presented in the chapter. Block processing technique which replaces the ordinary acquisition process and tracking loops was explained. The problems and the challenges of designing a GPS receiver were presented. Two primary and challenging tasks will be covered in this work. One task is the development of a new fast algorithm for acquisition and especially for performing fast circular correlation. The development of such algorithms is discussed next. This is followed by a fast acquisition method and its effect on detection probability in chapter 4. The other challenging task is the hardware implementation of such a method in an FPGA. The implementation of the method in the hardware is presented in Chapter 5.

## Chapter 3

# Convolution Algorithms Using Real and Binary Transforms

## 3.1 Introduction

Signal processing applications usually require complex and numerous operations. Therefore, fast and easy-to-implement algorithms have been sought by research groups and industries to cope with the advancement in the very large scale integrated circuits (VLSI) technology. Fast Fourier transforms (FFTs) have gained a tremendous amount of appreciation. They were used in most of the fast algorithms for DSP applications. Despite the fact that FFTs are efficient, they still require a large amount of processing time and a large silicon area when the size of the required FFTs is large. This is due to the complex multiplication computations that the FFTs have to perform.

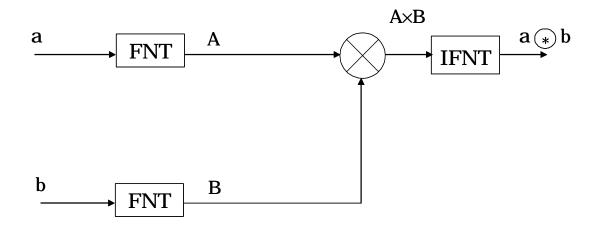

This chapter investigates two other transforms for their use in calculating circular correlation or convolution. The next section presents a real transform called Fermat number transform (FNT). The FNT-based convolution method is presented along with the method limitations. Another useful transform is presented later in the chapter. It is a binary transform and is called the Walsh Hadamard transform (WHT).

## 3.2 Fermat Number Transform and Convolution

#### 3.2.1 Fermat Number Transform

Number theoretic transforms (NTTs) are discrete transforms defined over finite rings. All the arithmetic in this finite ring is modulo the number of elements in the finite ring (Agarwal, 1974). Choosing the modulus as a Fermat number Ft makes the NTT a Fermat number transform (FNT). Fermat number transform (FNT) is defined as

$$X(k) = \langle \sum_{n=0}^{N-1} x(n) \alpha^{kn} \rangle Ft \qquad k = 0, 1, ..., N-1$$

$$Ft = 2^{b} + 1, b = 2^{t}$$

(3-1)