# FAULT DIAGNOSIS IN ANALOG AND MIXED MODE LOW TESTABILITY SYSTEM

# J. Starzyk, J. Pang

Electrical Engineering and Computer Science Ohio University Athens, OH 45701, USA

# ABSTRACT

This paper describes our views on how to detect faults in low testability analog or mixed mode (analog electro-mechanical) system. A new method is developed to identify a minimum number of faulty parameters in the system with ambiguities. From sensitivity analysis of the system, we can extract solution invariant matrix and identify singular cofactors of this matrix. The approach can be extended to the electro-mechanical systems, which combine electronic circuits with mechanical components.

# 1. INTRODUCTION

Testing issues are becoming more and more important with the quick development of both digital and analog circuit industry [1]. Among them, fault diagnosis and fault location are important parts of analog circuit testing and a lot of efforts are put to the automate fault diagnosis procedure [2][3][4][5][6].

Testability is strictly tied to the concept of networkelement-value-solvability, which was first introduced by Berkowitz [7]. Successively, a very useful testability measure was introduced by Saeks et al. [8][9][10]. Although other definitions exist [11][12], the Saeks definition is still popular. In fact, it gives a measure of solvability of nonlinear fault diagnosis equations, and indicates the ambiguity, which will result from an attempt to solve such equations in a neighborhood of almost any failure. Another concept which is strictly related to testability and which is extremely useful, particularly in case of a system with low testability value, is that of canonical ambiguity group. Although the concept of testability and canonical ambiguity group are important in a fault location method, test results are severely limited [13] without using them properly.

In this paper, we focus on a new method for low testability systems. Our method provides the minimum form solution under the assumption that the number of faulty parameters in VLSI circuits is small. First, we obtain system test equation by sensitivity analysis and find ambiguity groups. Then, for each ambiguity group, the equivalent fault vector is obtained based on the linear combination matrix. Although the system test equations usually have various solutions, the solution for the equivalent fault vector is unique. So it is possible to construct the solution invariant matrix to find the final detectable faults by our new methodology.

Especially, we developed integration method to find faults in electro-mechanical circuits, which usually have complicated high order differential equation models for the mechanical parts. By means of integration of system equation and sensitivity analysis for the system in time domain, we can extend our approach to detect faults in such system.

In addition, the weak dependence phenomenon is described and dealt with the NPN transistor circuit example. In such a case, we use decreased rank to get minimum linear combination matrix and find faults efficiently.

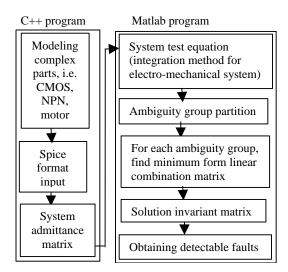

Our goal is to develop an efficient computer-aided fault diagnosis method. A block diagram of our approach can be seen in Fig. 1. The left part of the diagram basically get the parameter value and location information from the spice format description of the circuit system, whereas the right part corresponds to the set of ideas we developed for fault detection of analog low testability system. Sensitivity analysis is needed to construct system test equation from the system modified admittance matrix.

Fig. 1. Block diagram of our program MASTA (mixed-mode ambiguous system testability analysis program)

This paper is organized as follows. In section 2 we discuss our methodology for fault identification in low

This work was supported by the Air Force Research Lab #OSP 97145 F33615-96-2-1945 M#1 testability systems. In section 3, we list two test examples. Finally, we summarize our major research results in section 4.

# 2. FAULT IDENTIFICATION IN LOW TESTABILITY SYSTEMS

## 2.1 System test equations:

Let us consider the modified system admittance equation [14] first:

$$T \times X = W \tag{1}$$

$$\partial T / \partial h \times X + T \times \partial X / \partial h = \partial W / \partial h$$

(2)

$$\partial X / \partial h = -T^{-1} \times \partial T / \partial h \times X + T^{-1} \times \partial W / \partial h$$

(3)

Here, matrix T and vector W include not only the effects of admittance and current source, but also that of extra rows added for some components like voltage source. Matrix X is composed of node voltage and extra branch currents. h represents circuit parameter. Usually we may be more concerned with only several necessary node voltages

$$Y = d^{t} \times X$$

(4)

Next we define adjoint vector

$$Xa = -(T^t)^{-1} \times d \tag{5}$$

Combining equations (3)(4)(5), we can get

$$\frac{\partial Y}{\partial h} = \left\| X_a \right\|_{t}^{t} \times \frac{\partial T}{\partial h} \times X - \left\| X_a \right\|_{t}^{t} \times \frac{\partial W}{\partial h}$$

(6)

Moreover sensitivity matrix

$$B = \partial Y_i / \partial h_j \tag{7}$$

where  $Y_i$  represents the set of node voltages and branch currents which may be obtained under different frequency, and  $h_i$  represents different parameters.

Then we can get the nominal solution  $X = T^{-1} \times W$ and comparing with the actual measurement  $X_{error}$ , the measurement matrix is  $M = X_{error} - X$ . So the system test equation is

$$B \times P = M \tag{8}$$

# 2.2 INTEGRATION METHOD IN ELECTRO-MECHANICAL SYSTEM

Usually, the electro-mechanical system can be modeled in the state-space form by choosing the mechanical parameters and electrical parameters as the state variables. Suppose that the electro-mechanical state-space form equation is  $dZ/dt = G \times Z + C \times V$ , where Z is the state variable matrix, V is voltage input, G and C are constant matrix composed of electrical and mechanical parameters. In order to get system characteristics, integral method is implemented so that  $Z_{n+1} = \iint G \times Z_n + C \times V \oiint X \Delta t + Z_n$ , where  $Z_0$  is initial state variable,  $\Delta t$  is sufficient small time interval,  $n \ge 0$ , and n is integer. As a result, we can get  $dZ_{n+1}/dh = dZ_n/dh +$

$$(G \times d)Z_n / dh + dG/dh \times Z_n + dC/dh \times V \times \Delta t$$

(9)

If we define matrix  $B = dZ_n / dh$  and matrix  $M = Z_{error} - Z$ , which are calculated for different integer n at each time interval, the system test equation  $B \times P = M$  can be obtained, where **h** represents different mechanical and electrical parameters and *P* corresponds to parameter faults.

# 2.3 FAULT DIANOSIS METHOLODGY

For the system test equation  $B \times P = M$ , we assume the number of faulty parameters is small as a result of the uniform environment in the VLSI fabrication process and the number of the measurements M is greater than the number of parameters P.

The rank of testability matrix B determines a maximum number of the circuit parameters that can be uniquely identified by solving the test equations. If B does not have the full column rank, then it can be written as following:

$$BP = B_{1} \begin{bmatrix} I & C_{1} \end{bmatrix} | P_{2} | = \sum_{i=1}^{g} B_{i} P_{i} = \sum_{i=1}^{g} M_{i} = M \quad (10)$$

$$\hat{P} = P_1 + C_1 P_2 \tag{11}$$

and

$$B_{i} P_{i} = B_{1i} [I C_{1i}] \left\| P_{2i} \right\| = B_{1i} \hat{P}_{i} = M_{i}$$

(12)

with disjoint subsets of parameters representing ambiguity groups or testable components, where  $\hat{P}_i = P_{1i} + C_{1i} P_{2i}$  (13)

$\hat{P}_i$  is an equivalent set of parameter deviations in i-th ambiguity group and is called the equivalent fault vector. Since matrix  $B_{1i}$  has the full column rank, the equivalent fault vector is unique. However, in general, a solution for  $P_{1i}$  and  $P_{2i}$  is not unique. Since our aim is to solve the test equations with a minimum number of faulty components, we can obtain  $\hat{P}_i$  by forcing all  $P_{2i}$  to zero, therefore the largest number of faults we will consider equals to the size of  $P_{1i}$  which is equal to the rank of its ambiguity group. The following results are useful to find faults in the ambiguity groups.

**Lemma 1:** if i-th row of the linear combination matrix  $C_{1i}$  obtained by solving equation (11) is zero then i-th element of  $P_{1i}$  is uniquely identified.

Lemma 1 permits identification of all parameters that do not belong to any ambiguity group. All other parameters cannot be identified uniquely. Our objective is to identify a minimum number of faulty parameters that can satisfy test equations. **Lemma 2:** if an element  $\hat{p} \in \hat{P}_i$  of the equivalent fault vector obtained by solving equation (11) equals zero, with  $\hat{p} = p_{1k} + \sum_j c_{kj} p_{2j}$ , where  $p_{1k} \in P_{1i}$

and  $p_{2j} \in P_{2i}$ , then  $p_{1k} = p_{2j} = 0$  with probability equal to one (excluding a singular subspace in the solution space).

Even if conditions of Lemma 2 are not satisfied, a number of parameter deviations can be set to zero depending on the cofactors of the solution invariant matrix. For the i-th ambiguity group, we define solution invariant matrix  $S_i = [\hat{P}_i C_{ii}]$ . If a cofactor of  $S_i$  contains elements of  $\hat{P}_i$  as its first column and its remaining columns are linearly independent, we call it a proper cofactor. Since a proper cofactor must include at least one element of  $\hat{P}_i$ , its minimum size is one. In addition, it cannot have zero columns except the first one. If a proper cofactor is zero, then  $\hat{P}_i$  can be expressed by smaller number of nonzero parameters  $P_{1i}$  and  $P_{2i}$  than its size, which means that the number of nonzero parameters in the ambiguity group is less than its rank. We call such proper cofactor a nullifying cofactor.

**Lemma 3:** if none of nullifying cofactor of solutions of the invariant matrix  $S_i$  exists, and there is the *m*-th row of  $C_1$  that has only one nonzero element in its *n*th column, then  $\|P_1\|_m = 0$ , and  $\|P_2\|_n = \hat{P}_m / \|C_1\|_{mn}$ .

# 3. Test Examples

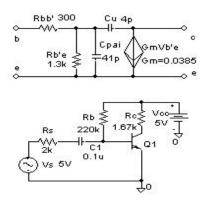

## 3.1 Negative phase NPN transistor

For this example, we can get modified admittance matrix T at different frequency using c++ program. For simulation purpose, we set only

Fig. 2. Negative phase amplifier and transistor model

two faults  $\Delta G_s = -0.0050$  and  $\Delta G_{bb'} = -0.0166$ . After we obtain system test equations, we can find that there is only one ambiguity group in this system:  $\left[ \Delta G_S, \Delta C_1, \Delta G_b, \Delta G_{bb'}, \Delta G_{bc'}, \Delta C_{cai}, \Delta C_u, \Delta G_m, \Delta G_c \right]$ .

Although rank of B is 8, we still find weak dependence. If weak dependencies are removed, then we can reduce the rank B to 4 by using singular value decomposition method as  $B = U \times S \times V'$ , where S is a diagonal matrix of the same dimension as B and with nonnegative diagonal elements in decreasing order, and matrices U and V are unitary. So, we adjust the linear combination matrix  $C_1$  to relate both dependent and weak dependent columns of matrix B. Then, following fault diagnosis methodology described in section 2.3, we can correctly identify faults and their values.

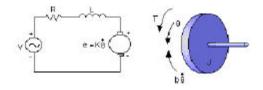

#### 3.2 Open loop DC motor

As the second example, consider electro-mechanical system illustrated by fig. 3.

Fig. 3. Electronic circuit with open loop DC motor

This system can be described by the equation:

$$\frac{d}{dt} \begin{pmatrix} d\mathbf{q}/dt \\ i \end{pmatrix} = D \times \begin{pmatrix} d\mathbf{q}/dt \\ i \end{pmatrix} + C \times V$$

(14)

where

$$D = \begin{vmatrix} -b/J & K/J \\ -K/L & R/L \end{vmatrix}, \text{ and } C = \begin{vmatrix} 0 \\ 1/L \end{vmatrix}.$$

J is moment of inertia of the rotor, b is the damping ratio of the mechanical system, and K is the electromotive force constant. Here, we use  $J=0.01 kg \cdot m^2 / s^2$ , b=0.1Nms, K=0.01Nm/Amp, R=10hm, L=0.5H, V=1v. For simulation purpose, we set one fault b=0.001. The system test equation is constructed in the following way:

$$d\mathbf{q}/dt \bigcup_{n+1} = D \times d\mathbf{q}/dt \bigcup_n + C \times V \times \Delta t + d\mathbf{q}/dt \bigcup_n$$

(15)

where

$$d\mathbf{q}/dt_{o} = 0$$

$i_{0} = 0$ .

$$\begin{aligned} & \downarrow d\mathbf{q}/dt \Big|_{n+1} / dh \\ & di_{n+1}/dh \end{aligned} = \begin{bmatrix} D \times \begin{bmatrix} d\mathbf{q}/dt \Big|_{n} \\ di_{n}/dh \end{bmatrix} + dC/dh \times V \\ & + dD/dh \times \begin{bmatrix} d\mathbf{q}/dt \Big|_{n} \\ i_{n} \end{bmatrix} \times \Delta t + \begin{bmatrix} d\mathbf{q}/dt \Big|_{n} \\ di_{n}/dh \end{bmatrix}$$

(16)

where h is a group of parameters [b, K, J, R, L].

We iterate equation (14) and (15) for different values of n. As a result, system test matrix B consists of solutions of equation (15). Moreover, we can get measurement matrix M by deducting,

$$\begin{bmatrix} i, d\boldsymbol{q}/dt \end{bmatrix}^T$$

from  $\begin{bmatrix} i_{error}, d\boldsymbol{q}_{error} / dt \end{bmatrix}^T$ . Then,

we find only one ambiguity group  $(\Delta K, \Delta R, \Delta L, \Delta J, \Delta b)$ .

Finally, using our fault diagnosis method, program MASTA can successfully find fault in the damping ratio parameter.

# 4. Summary

New method of fault detection in mixed-mode low testability system has been proposed. The method is based on sensitivity analysis to obtain system test equations and then find minimum faulty solution under the assumption that the number of faulty parameters is limited because of the uniform deviation of VLSI process.

For each ambiguity group in the analog system, the equivalent fault vector has unique solution. Based on this idea, we introduce several useful concepts such as linear combination matrix, solution invariant matrix, proper cofactor, and nullifying cofactor. Then, we prescribe 3 lemmas to further describe our fault diagnosis methodology. In addition, weak dependence phenomenon and a solution method is described in the example. By combining state equations of mechanical components with electrical system through interface equations, we extend our fault testability approach to electro-mechanical systems. Integral sensitivity and regularization approach can described in [15] can be added to this method in future work. Furthermore, if efficient ways to get access to testing points in MEMS (Microelectromechanics Systems) exist, which remain to be the challenging issues because of the complex machine structure with micron feature sizes in such systems, the measurements can be combined with our system approach to find faults.

### 5. References

[1] European design and test conference conclusions, Mars 1996.

[2] S. Manetti, M.C. Piccirilli, and A. Liberatore, "Automatic test point selection for linear analog network fault diagnosis," Proc. IEEE Symp. Circuits and Systems, vol. 1, IEEE CS Press, 1990. [3] J. Rutkowski, J. Machniewski, "Sensitivity based analog fault dictionary," Proc. ECCTF'99 Stresa-Lago Maggiore, Sep. 1999.

[4] K. C. Varghese, J. H. Williams and D. R. Towill, "Simplified ATPG and analog fault location via a clustering and separability technique", IEEE Trans. Circuits and Systems, vol. CAS-26, pages 496-505, 1979.

[5] N. Nagi, A. Chatterjee, A. Balivada, J. Abraham, "Fault-based automatic test generator for linear analog circuits", Proc 1993 IEEE ACM Int. Conf. Computer Aided Design, 1993, Published by IEEE. Service Center, Piscataway, NJ, USA, IEEE cat. n 93CH3344-9, pages 88-91

[6] A. E. Salama, J. A. Starzyk and J. W. Bandler, "A unified decomposition approach for fault location in large analog circuits", IEEE. Trans. Circuits and Systems, vol. CAS-31 pages 609-622, 1981.

[7] M. Slamani; B. Kaminska, "Multifrequency testability analysis for analog circuits", Proceedings of the IEEE VLSI Test Symposium 1994. IEEE, Los

Alamitos, CA, USA. pages 54-59

[8]] C. C. Wu, K. Nakajima, C. L. Wey and R. Saeks, "Analog fault diagnosis with failure bounds", IEEE. Trans. Circuits and Systems, vol. CAS-29, pages 277-284, 1982.

[9] N.Sen and R. Saeks, "Fault diagnosis for linear systems via multifrequency measurement", IEEE. Trans. Circuits and Systems, vol. CAS-26, pages 457-465, 1979.

[10] H. M. S. Chen and R. Saeks, "A search algorithm for the solution of multifrequency fault diagnosis equations", IEEE. Trans. Circuits and Systems, vol. CAS-26, pages 589-594, 1979.

[11] J. W. Bandler and A. E. Salama, "Fault diagnosis of analog circuits", Proc. IEEE, vol. 73, pages 1279-1325,1985.

[12] R. W. Priester and J. B. Clary, "New measures of testability and test complexity for linear analog failure analysis", IEEE. Trans. Circuits and Systems, vol. CAS-28, pages 1088-1092, 1981.

[13] G. Fedi, S. Manetti, J.A. Starzyk, M. C. Piccirilli "Determination of an Optimum Set of Testable Components in the Fault Diagnosis of Analog Circuits", IEEE Trans. Circuits and Systems, Part I, vol. 46, no.7, 1999, pages 779-787.

[14] Lawrence T. Pillage, R. A. Rohrer, C. Visweswariah, "Electronic circuit and system simulation methods", McGraw-Hill, Inc., 1995

[15] V. Brygillewicz, J. Wociechowski, J. Starzyk, "Testing of analog dynamic systems based on integral sensitivity", Proc. of the European Conference on Circuit theory and design, ECTD'99, Stresa, Italy, Aug, 1999, pages 1043-1046