## Some Virtual Memory Design Parameters

|                       | Paged VM                     | TLBs                 |

|-----------------------|------------------------------|----------------------|

| Total size            | 16,000 to<br>250,000 words   | 16 to 512<br>entries |

| Total size (KB)       | 250,000 to<br>1,000,000,000  | 0.25 to 16           |

| Block size (B)        | 4000 to 64,000               | 4 to 32              |

| Miss penalty (clocks) | 10,000,000 to<br>100,000,000 | 10 to 1000           |

| Miss rates            | 0.00001% to<br>0.0001%       | 0.01% to<br>2%       |

11

## Two Machines' Cache Parameters

|                  | Intel P4                                    | AMD Opteron                                                       |

|------------------|---------------------------------------------|-------------------------------------------------------------------|

| TLB organization | 1 TLB for instructions<br>and 1TLB for data | 2 TLBs for instructions and 2 TLBs for data                       |

|                  | Both 4-way set<br>associative               | Both L1 TLBs fully<br>associative with ~LRU                       |

|                  | Both use ~LRU                               | replacement                                                       |

|                  | replacement                                 | Both L2 TLBs are 4-way set<br>associative with round-robin<br>LRU |

|                  | Both have 128 entries                       | Both L1 TLBs have 40 entries                                      |

|                  |                                             | Both L2 TLBs have 512<br>entries                                  |

|                  | TLB misses handled in<br>hardware           | TBL misses handled in hardware                                    |

| TLB Event Combinations |               |       |                                                                 |

|------------------------|---------------|-------|-----------------------------------------------------------------|

| TLB                    | Page<br>Table | Cache | Possible? Under what circumstances?                             |

| Hit                    | Hit           | Hit   | Yes – what we want!                                             |

| Hit                    | Hit           | Miss  | Yes – although the page table is not<br>checked if the TLB hits |

| Miss                   | Hit           | Hit   | Yes – TLB miss, PA in page table                                |

| Miss                   | Hit           | Miss  | Yes – TLB miss, PA in page table, but data<br>not in cache      |

| Miss                   | Miss          | Miss  | Yes – page fault                                                |

| Hit                    | Miss          | Miss/ | Impossible – TLB translation not possible if                    |

|                        |               | Hit   | page is not present in memory                                   |

| Miss                   | Miss          | Hit   | Impossible – data not allowed in cache if page is not in memory |

| Summary |                                                                                                                          |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

|         | The Principle of Locality:                                                                                               |  |  |  |

|         | <ul> <li>Program likely to access a relatively small portion of the address<br/>space at any instant of time.</li> </ul> |  |  |  |

|         | Temporal Locality: Locality in Time                                                                                      |  |  |  |

|         | Spatial Locality: Locality in Space                                                                                      |  |  |  |

|         | Caches, TLBs, Virtual Memory all understood by examining how they deal with the four questions                           |  |  |  |

|         | I. Where can block be placed?                                                                                            |  |  |  |

|         | 2. How is block found?                                                                                                   |  |  |  |

|         | 3. What block is replaced on miss?                                                                                       |  |  |  |

|         | 4. How are writes handled?                                                                                               |  |  |  |

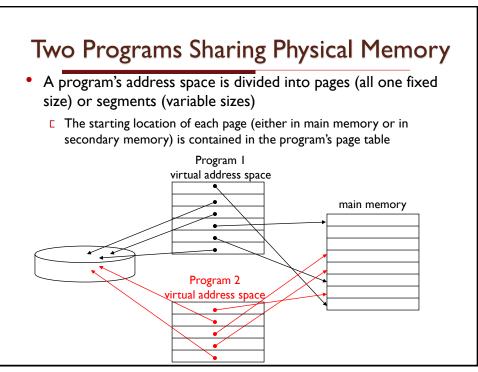

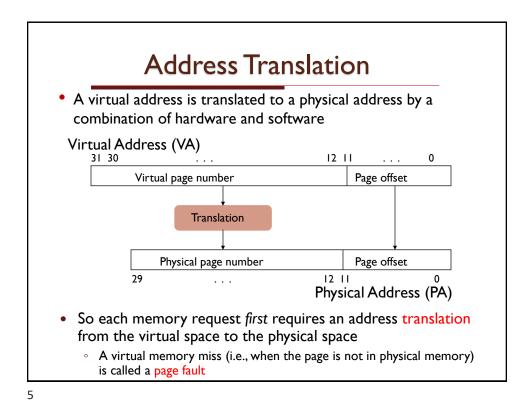

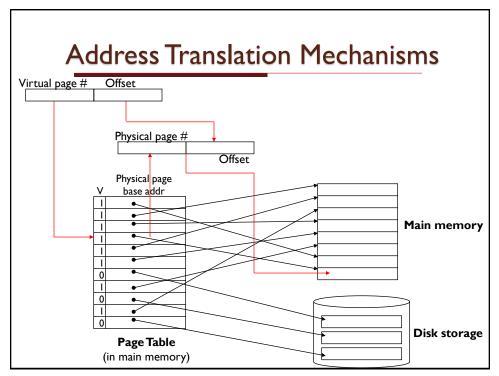

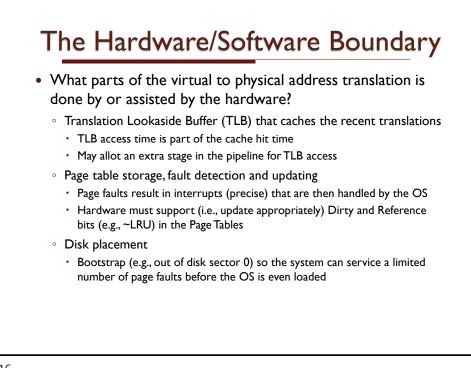

|         | Page tables map virtual address to physical address                                                                      |  |  |  |

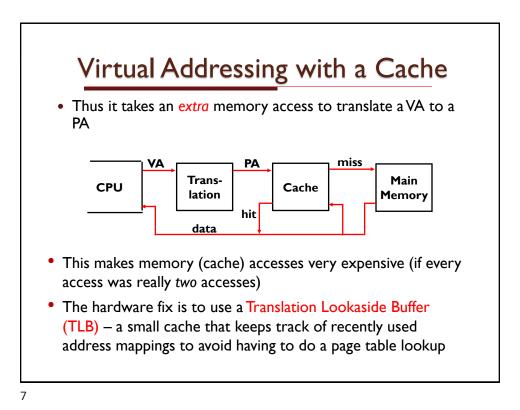

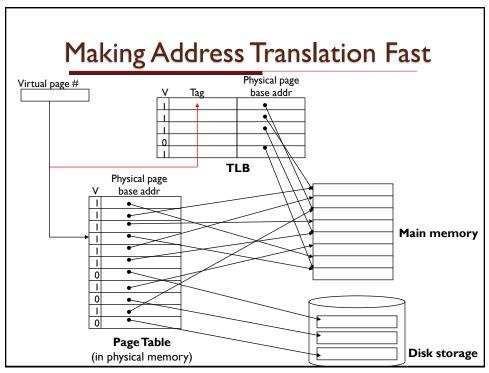

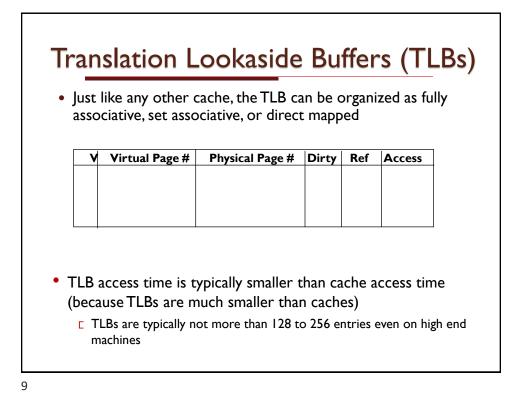

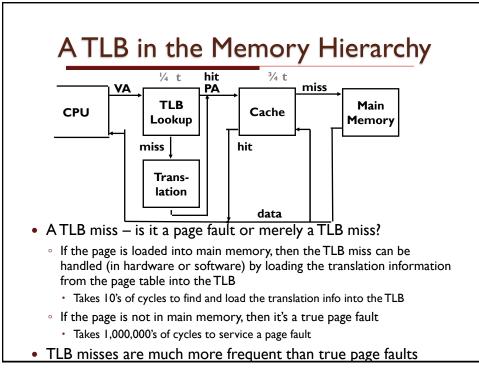

|         | • TLBs are important for fast translation                                                                                |  |  |  |