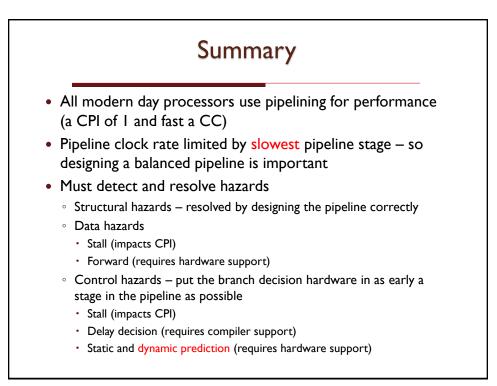

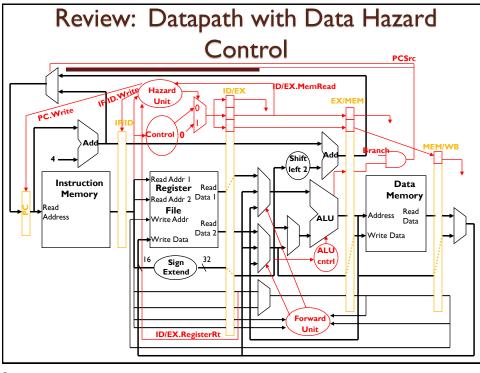

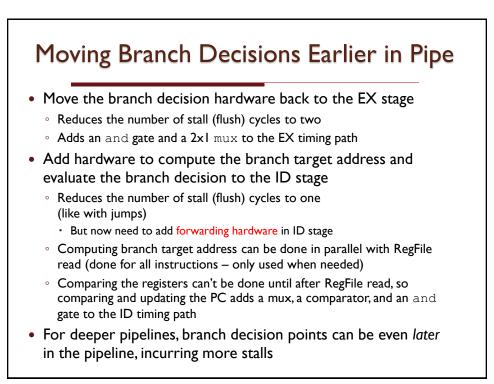

## Control Hazards When the flow of instruction addresses is not sequential (i.e., PC = PC + 4); incurred by change of flow instructions Conditional branches (beq,bne) Unconditional branches (j, jal, jr) Exceptions Possible approaches Stall (impacts CPI) Move decision point as early in the pipeline as possible, thereby reducing the number of stall cycles Delay decision (requires compiler support) Predict and hope for the best ! Control hazards occur less frequently than data hazards, but there is *nothing* as effective against control hazards as forwarding is for data hazards

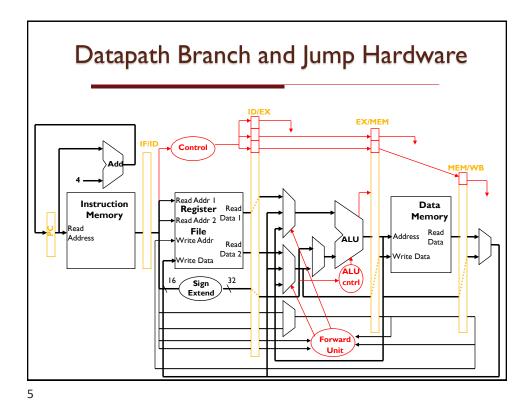

Datapath Branch and Jump Hardware PCSrc Shift ID/EX EX/MEI left 2 Control Add PC+4[31-28] Shift ١dd left 2 lead Addr I Instruction Data Register Read Read Addr 2 Data I Memory Memory Read File Read Data Address Address ALU rite Addr Read Data 2 Vrite Data rite Data ALU 32 Sign Extend cntrl Forward Unit

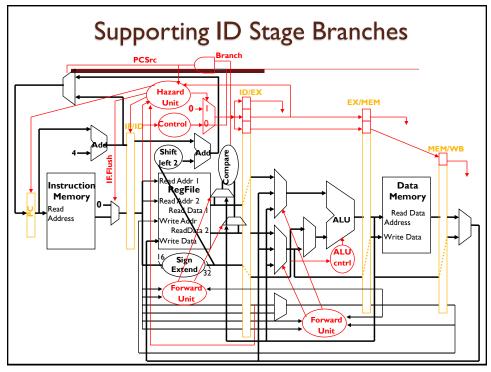

| ID Branch Forwarding Issues                                                                                                                                                                                    |                             |                                                                           |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------|--|

| <ul> <li>MEM/WB "forwarding"<br/>is taken care of by the<br/>normal RegFile write<br/>before read operation</li> </ul>                                                                                         | WB<br>MEM<br>EX<br>ID<br>IF | add3 \$1,<br>add2 \$3,<br>add1 \$4,<br>beq \$1,\$2,Loop<br>next_seq_instr |  |

| <ul> <li>Need to forward from the<br/>EX/MEM pipeline stage to<br/>the ID comparison hardware<br/>for cases like</li> </ul>                                                                                    | WB<br>MEM<br>EX<br>ID<br>IF | add3 \$3,<br>add2 \$1,<br>add1 \$4,<br>beq \$1,\$2,Loop<br>next_seq_instr |  |

| <pre>if (IDcontrol.Branch and (EX/MEM.RegisterRd != 0 and (EX/MEM.RegisterRd = IH         ForwardC = 1 if (IDcontrol.Branch and (EX/MEM.RegisterRd != 0 and (EX/MEM.RegisterRd = IH         ForwardD = 1</pre> | ))                          | second previous<br>instr. to either<br>input of the                       |  |

## ID Branch Forwarding Issues, con't

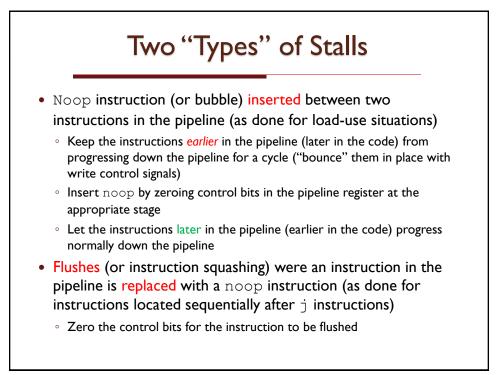

| <ul> <li>If the instruction immediately<br/>before the branch produces<br/>one of the branch source<br/>operands, then a stall needs<br/>to be inserted (between the<br/>beg and add1) since the EX stage ALU<br/>operation is occurring at the same time a<br/>the ID stage branch compare operation</li> </ul> |  | add3 \$3,<br>add2 \$4,<br>add1 \$1,<br>beq \$1,\$2,Loop<br>next_seq_instr |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---------------------------------------------------------------------------|--|--|

| "Bounce" the beq (in ID) and next_seq_instr (in IF) in place (ID Hazard Unit deasserts PC.Write and IF/ID.Write)                                                                                                                                                                                                 |  |                                                                           |  |  |

| Insert a stall between the add in the EX stage and the beg in the<br>ID stage by zeroing the control bits going into the ID/EX pipeline<br>register (done by the ID Hazard Unit)                                                                                                                                 |  |                                                                           |  |  |

| <ul> <li>If the branch is found to be taken, then flush the<br/>instruction currently in IF (IF.Flush)</li> </ul>                                                                                                                                                                                                |  |                                                                           |  |  |

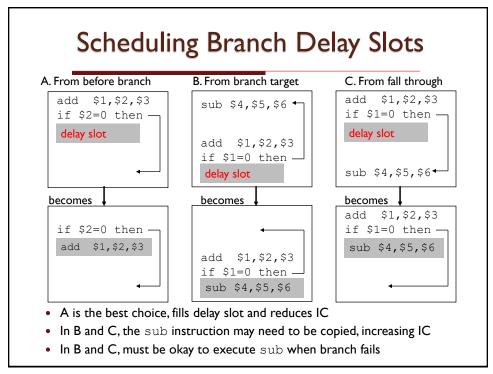

- If the branch hardware has been moved to the ID stage, then we can eliminate all branch stalls with delayed branches which are defined as always executing the next sequential instruction after the branch instruction – the branch takes effect *after* that next instruction

- MIPS compiler moves an instruction to immediately after the branch that is not affected by the branch (a safe instruction) thereby hiding the branch delay

- With deeper pipelines, the branch delay grows requiring more than one delay slot

- Delayed branches have lost popularity compared to more expensive but more flexible (dynamic) hardware branch prediction

- Growth in available transistors has made hardware branch prediction relatively cheaper

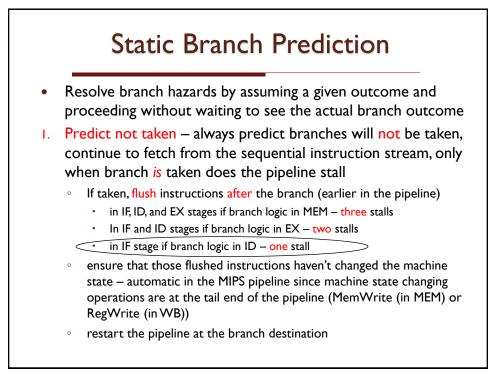

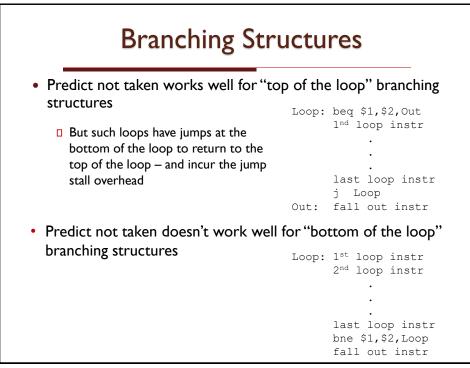

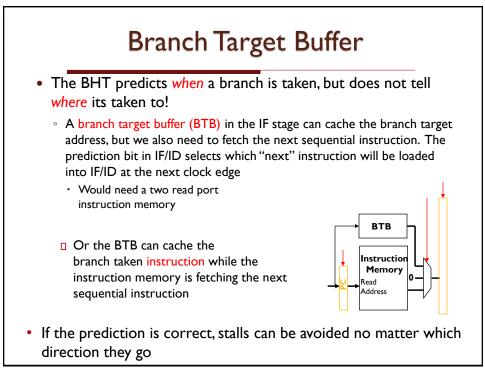

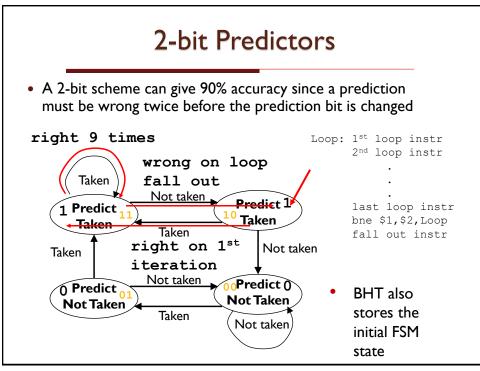

- A branch prediction buffer (aka branch history table (BHT)) in the IF stage addressed by the lower bits of the PC, contains a bit passed to the ID stage through the IF/ID pipeline register that tells whether the branch was taken the last time it was executed

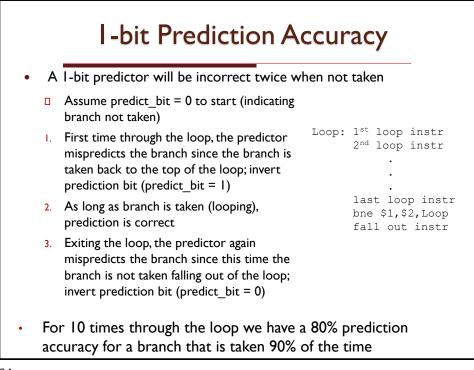

- Prediction bit may predict incorrectly (may be a wrong prediction for this branch this iteration or may be from a different branch with the same low order PC bits) but the doesn't affect correctness, just performance

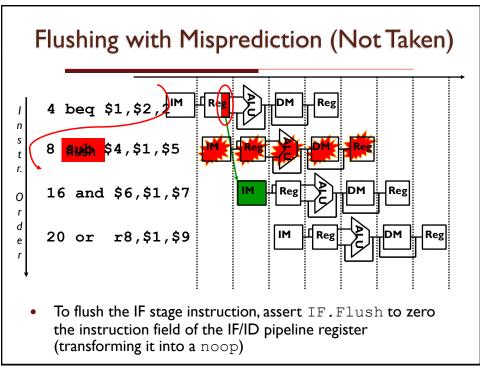

- Branch decision occurs in the ID stage after determining that the fetched instruction is a branch and checking the prediction bit

- If the prediction is wrong, flush the incorrect instruction(s) in pipeline, restart the pipeline with the right instruction, and invert the prediction bit

- A 4096 bit BHT varies from 1% misprediction (nasa7, tomcatv) to 18% (eqntott)

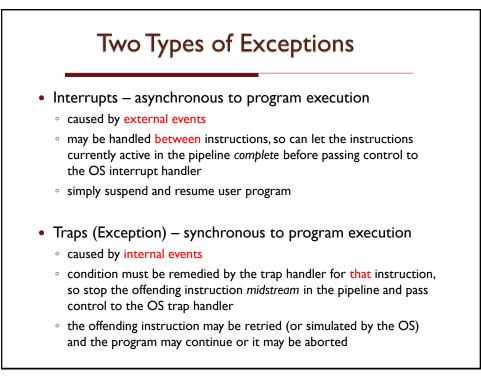

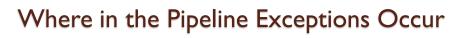

## Dealing with Exceptions

- Exceptions (aka interrupts) are just another form of control hazard. Exceptions arise from

- R-type arithmetic overflow

- Trying to execute an undefined instruction

- An I/O device request

- An OS service request (e.g., a page fault, TLB exception)

- A hardware malfunction

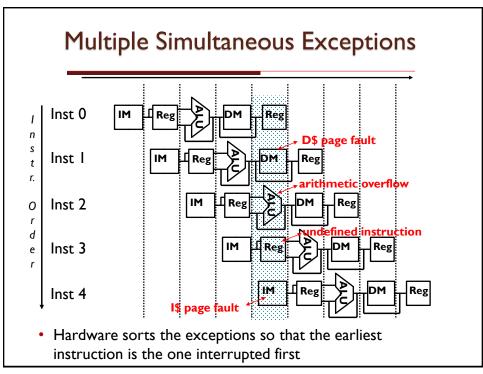

- The pipeline has to stop executing the offending instruction in midstream, let all prior instructions complete, flush all following instructions, set a register to show the cause of the exception, save the address of the offending instruction, and then jump to a prearranged address (the address of the exception handler code)

- The software (OS) looks at the cause of the exception and "deals" with it

## Additions to MIPS to Handle Exceptions (Fig 6.42)

- Cause register (records exceptions) hardware to record in Cause the exceptions and a signal to control writes to it (CauseWrite)

- EPC register (records the addresses of the offending instructions) – hardware to record in EPC the address of the offending instruction and a signal to control writes to it (EPCWrite)

- · Exception software must match exception to instruction

- A way to load the PC with the address of the exception handler

- Expand the PC input mux where the new input is hardwired to the exception handler address - (e.g., 8000 0180<sub>hex</sub> for arithmetic overflow)

- A way to flush offending instruction and the ones that follow it