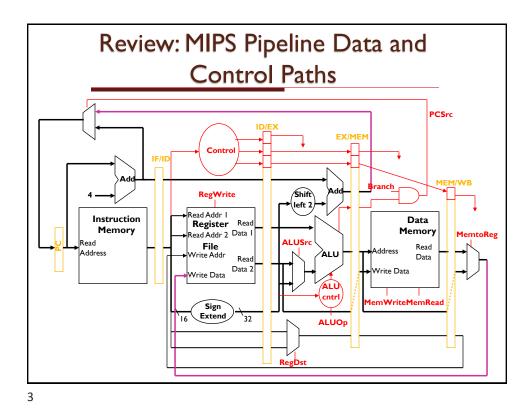

|     | Control Settings |             |            |            |           |             |              |              |              |  |

|-----|------------------|-------------|------------|------------|-----------|-------------|--------------|--------------|--------------|--|

|     |                  |             |            |            |           |             |              |              |              |  |

|     | EX Stage         |             |            |            | MEM Stage |             |              | WB Stage     |              |  |

|     | RegDst           | ALU<br>Op I | ALU<br>Op0 | ALUS<br>rc | Brch      | MemR<br>ead | Mem<br>Write | RegWr<br>ite | Mem<br>toReg |  |

| R   | I                | I           | 0          | 0          | 0         | 0           | 0            | I            | 0            |  |

| lw  | 0                | 0           | 0          | I          | 0         | 1           | 0            | I            | I            |  |

| sw  | X                | 0           | 0          | I          | 0         | 0           | I            | 0            | Х            |  |

| beq | Х                | 0           | I          | 0          | I         | 0           | 0            | 0            | Х            |  |

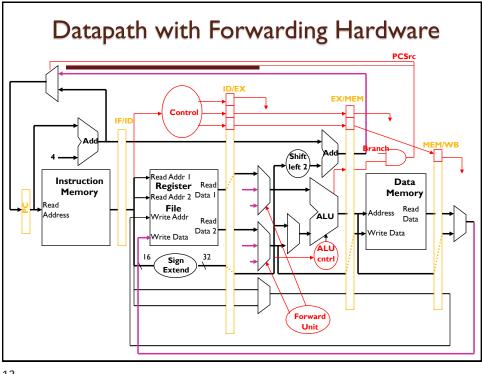

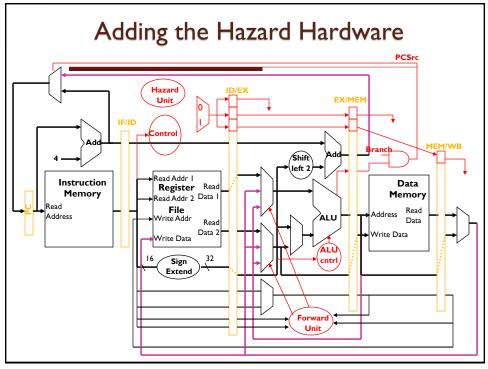

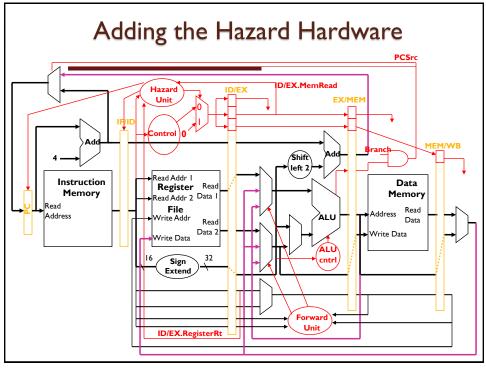

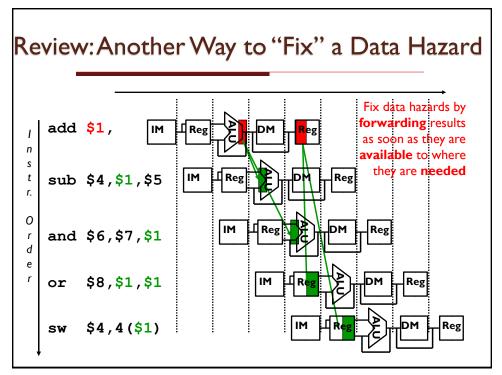

## Data Forwarding (aka Bypassing)

- Take the result from the earliest point that it exists in any of the pipeline state registers and forward it to the functional units (e.g., the ALU) that needs it in that cycle

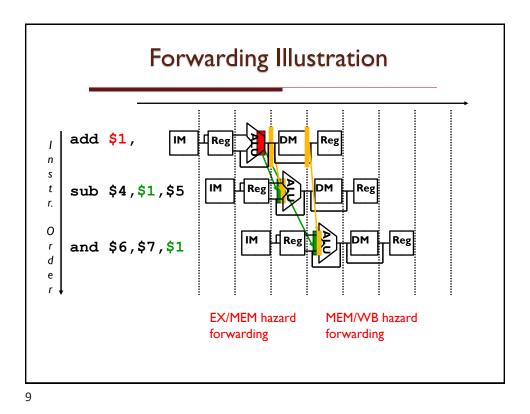

- For ALU functional unit: the inputs can come from any pipeline register rather than just from ID/EX by

- adding multiplexors to the inputs of the ALU

- connecting the Rd write data in EX/MEM or MEM/WB to either (or both) of the EX's stage Rs and Rt ALU mux inputs

- adding the proper control hardware to control the new muxes

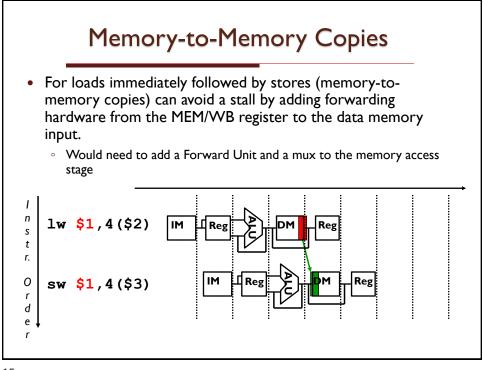

- Other functional units may need similar forwarding logic (e.g., the DM)

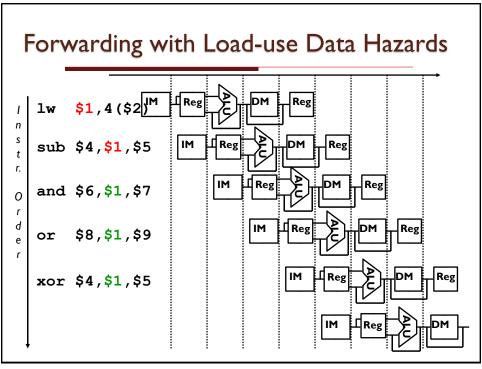

- With forwarding can achieve a CPI of I even in the presence of data dependencies

7

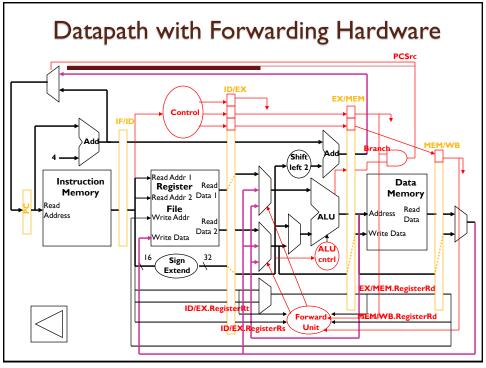

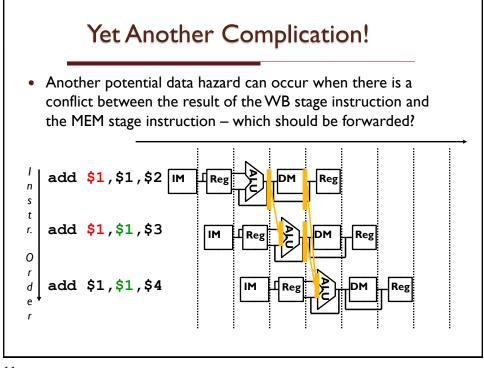

## **Data Forwarding Control Conditions** EX/MEM hazard: Ι. if (EX/MEM.RegWrite Forwards the and (EX/MEM.RegisterRd != 0) result from the and (EX/MEM.RegisterRd = ID/EX.RegisterRs)) previous instr. to ForwardA = 10if (EX/MEM.RegWrite either input of and (EX/MEM.RegisterRd != 0) the ALU and (EX/MEM.RegisterRd = ID/EX.RegisterRt)) ForwardB = 102. MEM/WB hazard: if (MEM/WB.RegWrite Forwards the and (MEM/WB.RegisterRd != 0) result from the and (MEM/WB.RegisterRd = ID/EX.RegisterRs)) second previous ForwardA = 01instr. to either if (MEM/WB.RegWrite input of the ALU and (MEM/WB.RegisterRd != 0) and (MEM/WB.RegisterRd = ID/EX.RegisterRt)) ForwardB = 01

## Description of the provide the provided the provided